Fターム[5F032BA03]の内容

素子分離 (28,488) | 形状・配置 (1,422) | 分離領域の形状(断面・平面) (924) | 厚さの異なる分離領域 (214)

Fターム[5F032BA03]に分類される特許

1 - 20 / 214

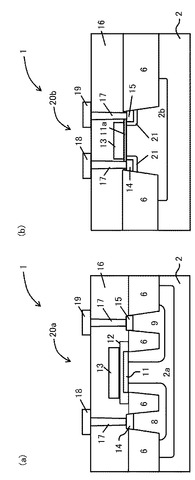

半導体装置およびその製造方法

【課題】低耐圧トランジスタ特性への影響なく、耐圧特性および動作特性が安定した高耐圧素子を組み込む。

【解決手段】同一の半導体基板2上に、トレンチ分離絶縁膜(プラズマ酸化膜6)によって素子分離された高耐圧素子20aと低耐圧素子20bを設けた半導体装置1において、高耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さが低耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さよりも低く形成されている。高耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さが、高耐圧素子20aのチャネルを形成する半導体基板2の表面に対して−10〜60nm(より好ましくは−10〜30nm)だけ高くなるように形成されている。

(もっと読む)

様々な絶縁領域及び/又は局所的な垂直導電領域を有する混合積層構造物を製造する方法

【課題】化学機械的研磨の長い段階に頼らずに半導体基板上に半導体構造物を製造することを提案する。

【解決手段】本発明は、深さpのパターンを有する表面トポロジーを有する半導体基板上に半導体構造物を製造する方法であって、前記方法は、(a)前記表面に第1絶縁材料の第1層(24)を形成する段階と、(b)前記第1層上に前記第1絶縁材料より密度が低い第2絶縁材料(28)の第2層を形成する段階と、(c)前記段階(a)及び段階(b)によって形成された構造物を薄膜化する段階と、(d)前記段階(c)によって薄膜化された前記構造体の第2層を緻密化する段階と、(e)前記段階(d)によって緻密化された前記第2層を有する構造体を薄膜化する段階と、(f)第2基板を用いた組立段階と、を含む方法である。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】FinFETの特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板の上層部分に凹部を形成する工程と、前記凹部内に犠牲材を配置する工程と、前記半導体基板及び前記犠牲材を選択的に除去することにより、一方向に延び、周期的に配列された複数本のフィンを形成する工程と、前記フィン間の空間の下部に素子分離絶縁膜を形成する工程と、前記犠牲材を除去する工程と、前記フィンの露出面上にゲート絶縁膜を形成する工程と、前記素子分離絶縁膜上に、前記フィンを跨ぐように、前記一方向に対して交差した方向に延びるゲート電極を形成する工程と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SOIウェハに高耐圧素子の領域と低耐圧素子の領域とが形成された半導体装置であって、製造工程の中で、作業ステージに静電吸着したり、異常放電を引き起こしたりすることを抑えることができる半導体装置を提供する。

【解決手段】半導体層2と、半導体層2の上に形成された絶縁層3と、絶縁層3の上に形成された半導体の第1領域10aと、絶縁層3の上に形成され、第1領域10aに隣接する半導体の第2領域20と、絶縁層3の上に形成され、第1領域10aの側面を覆うように取り囲み、第1領域10aと第2領域20とが直接接続するように開口された開口部31aを有する絶縁体の第1絶縁壁30aとを具備する。

(もっと読む)

集積回路装置及びその製造方法

【課題】FinFETの特性が均一な集積回路装置及びその製造方法を提供する。

【解決手段】実施形態に係る集積回路装置は、半導体基板の上面に形成され、第1方向に延びる複数本のフィンと、前記フィン間に配置された素子分離絶縁膜と、前記第1方向に対して交差した第2方向に延び、前記素子分離絶縁膜上に設けられたゲート電極と、前記フィンを前記ゲート電極から絶縁する絶縁膜と、を備える。そして、連続して配列された複数本の前記フィンが配置された第1領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも下方の第1の位置に位置し、前記第1領域から見て前記第2方向に位置する第2領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも上方の第2の位置に位置する。また、前記第2領域においては、前記素子分離絶縁膜が前記フィンの側面の全体を覆っている。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性の高い半導体装置を実現する。

【解決手段】半導体装置100は、基板30と、基板30に埋め込まれた絶縁膜20と、絶縁膜20上に形成された複数の抵抗素子10と、を備えている。基板30は、複数の抵抗素子10を有する抵抗素子形成領域40において複数の凸部32を有している。複数の凸部32は、絶縁膜20に入り込んでおり、かつ上端が絶縁膜20の表面よりも低い。このため、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスが複雑になるといったことを防ぎつつ、n型及びp型MOSトランジスタについて両方の性能を向上させた半導体装置を提供する。

【解決手段】半導体基板1の面内に、n型MOSトランジスタと、p型MOSトランジスタとを備える半導体装置であって、n型MOS型トランジスタが形成される第1の拡散層2aの間を絶縁分離する第1の絶縁層3aと、p型MOS型トランジスタが形成される第2の拡散層2cの間を絶縁分離する第2の絶縁層3bとを備え、第1の絶縁層3aは、半導体基板1の表層に形成された第1の溝部4aに、シリコン窒化膜5と、このシリコン窒化膜5の上にシリコン酸化膜6とを埋め込むことによって形成され、第2の絶縁層3bは、半導体基板1の表層に第1の溝部4aよりも幅広となるように形成された第2の溝部4bに、シリコン酸化膜6を埋め込むことによって形成されている。

(もっと読む)

半導体装置

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】クラックや結晶欠陥の発生なしに高電圧トランジスタの素子領域間の耐圧を向上できるようにした不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域の第1素子分離絶縁層が当該メモリセル領域の第1素子分離溝内に第1の酸化膜を埋め込んで構成され、第1の酸化膜の上面が半導体基板の上面と第1ゲート電極の上面との間に存在するように構成されている。

周辺領域の第2素子分離絶縁層は、周辺領域の第2素子分離溝内の全体に埋込まれると共にその上面が半導体基板の上面の上方に突出した第1の酸化膜と、当該第1の酸化膜上に積層され、その上面が第1導電膜の上面より上方に突出している第2の酸化膜とで構成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

半導体装置

【課題】より確実に画素間クロストークを抑制することが可能な、固体撮像素子を備える半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に配置された第1導電型の不純物層DPWと、不純物層DPW上に、第1導電型の不純物領域と第2導電型の不純物領域とが互いに接合する構成を含む光電変換素子と、光電変換素子を含む単位画素を構成し、光電変換素子と電気的に接続されるトランジスタM1〜M4とを備えている。平面視において光電変換素子の外周部の少なくとも一部には、内部に空隙AGが含まれ、光電変換素子と、光電変換素子に隣接する光電変換素子とを、互いに電気的に絶縁する分離絶縁層SIが配置されている。上記分離絶縁層SIは、第1導電型の不純物層DPWの最上面に接する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイおよび周辺回路領域の素子分離領域の深さを調節しつつ、周辺回路部の素子分離領域に形成されるマイクロトレンチ形状の影響を抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に設けられデータを記憶する複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられメモリセルアレイを制御する周辺回路部とを備えている。素子分離部は、複数のメモリセルおよび周辺回路部が形成されるアクティブエリア間に設けられている。側壁膜は、周辺回路部におけるアクティブエリアの側面に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

半導体装置の製造方法

【課題】高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板にアライメントマークとなる溝を形成し、アライメントマークに位置合わせして素子分離領域となる領域を露出し素子領域となる領域を覆うマスク膜を形成し、マスク膜をマスクとして半導体基板を異方性エッチングし、半導体基板の素子分離領域となる領域に素子分離溝を形成し、素子分離溝を絶縁膜で埋め込み素子分離絶縁膜を形成する半導体装置の製造方法において、溝を形成する工程では、マスク膜の厚さに相当する深さよりも浅い溝を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】パワーデバイスの高耐圧とオン抵抗の低減とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板101内のソース領域107A、ドレイン領域107B、及びドレイン領域107Bに接したドリフト領域105と、ソース領域107A及びドレイン領域107B間のドリフト領域105内のSTI絶縁層I−2と、STI絶縁層I−2上、ドリフト領域105上、並びに、ソース領域107A及びドレイン領域107B間のチャネル領域上のゲート電極110とを備える。STI絶縁層I−2は、第1及び第2のトレンチの内面上の第1の酸化膜102及び窒化膜103と、第1及び第2のトレンチを満たす窒化膜103上の第2の酸化膜104とを備える。第2のトレンチは、第1のトレンチ内に形成され、第1のトレンチの底面よりも低い底面を有し、第1のトレンチの幅よりも狭い幅を有する。

(もっと読む)

1 - 20 / 214

[ Back to top ]