Fターム[5F033HH12]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | Cu (5,213) | Cu合金 (720)

Fターム[5F033HH12]に分類される特許

701 - 720 / 720

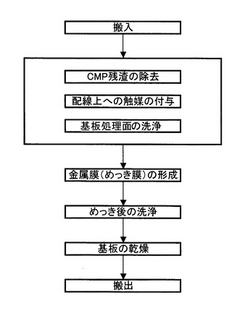

基板処理方法及び装置

【課題】 例えば配線等の下地金属の内部にボイドを発生させることなく、下地金属の露出表面に無電解めっきによって金属膜を確実に形成でき、しかも、スループットを向上させることができるようにする。

【解決手段】 下地金属を形成した基板の表面に無電解めっきにより金属膜を形成するに際し、基板の表面を、カルボキシル基を有する有機酸またはその塩の水溶液に界面活性剤を添加した洗浄液で洗浄し、洗浄後の基板の表面を、金属触媒イオンを含む溶液に前記洗浄液を混合した処理液に接触させて基板の表面に触媒を付与する。

(もっと読む)

デュアル・ダマシン構造におけるMIMキャパシタの構造および製作方法

【課題】MIM(金属−絶縁体−金属)キャパシタ(242/252)構造およびそれを形成する方法を提供すること。

【解決手段】第1パターン(216)および第2パターン(218)を有するデュアル・ダマシン・パターンで、半導体デバイス(200)の誘電体層(214)をパターニングする。第2パターン(218)は、第1パターン(216)よりも深い。第1パターン中の誘電体層(214)の上に導電層(226)を形成し、第1パターン(216)中のこの導電層の上に導電層を形成する。第2パターン(218)の導電層(226)の上に、誘電体層(232)、導電層(234)、誘電体層(236)、および導電層(238)を配設する。導電層(234)、誘電体層(232)、および導電層(226)が、第1のMIMキャパシタ(252)を形成する。導電層(238)、誘電体層(236)、および導電層(234)が、第1のMIMキャパシタ(252)に並列な第2のMIMキャパシタ(242)を形成する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、低抵抗であって且つ絶縁膜及び配線との間で高い密着性を有するバリアメタル膜を有する半導体装置を提供する。

【解決手段】 半導体装置は、基板(1)上に形成された絶縁膜(6,8)と、絶縁膜(6,8)中に形成された埋め込み配線(14)と、絶縁膜(6,8)と埋め込み配線(14)との間に形成されたバリアメタル膜(A1)とを有する。バリアメタル膜(A1)は、絶縁膜(6,8)が存在している側から埋め込み配線(14)が存在している側へ向かって順に積層されている金属酸化物膜(11)、遷移層(12a)及び金属膜(13)よりなり、遷移層(12a)は、金属酸化物膜(11)の組成と金属膜(13)の組成とのほぼ中間的な組成を有する単一の原子層よりなる。

(もっと読む)

相互接続構造の製造方法

【課題】 従来のデュアル・ダマシンとULK IMD材料との統合が有する問題を解決するための相互接続構造を形成する方法を提供する。

【解決手段】 相互接続構造は、原子層堆積又は超臨界流体ベースのプロセスによって薄いコンフォーマルな不動態化誘電体及び/又は拡散障壁キャップ及び/又はハード・マスクを堆積させるステップを含む方法により製造される。

(もっと読む)

メモリセル形成のためのインサイチュ表面処理

有機メモリセルの製造中などに実施されうるものなど、導電層上にパッシブ層を形成するためのシステムおよび方法が開示され、これは、一般に、従来の無機メモリデバイスに固有の不具合を低減させる。パッシブ層は硫化銅(Cu2S)などの導電促進化合物を含み、これは、導電材料の上部から形成される。この導電材料はメモリセルにおいて下部電極として作用し、導電材料の上部が、フッ素(F)系ガスから生成されたプラズマによる処理によってパッシブ層に変換されうる。  (もっと読む)

(もっと読む)

積層回路材料

【課題】特性インピーダンスを小さくできるために、超高周波又は超高速信号の伝送時においても反射や放射が少なく、かつ低損失である回路材料を提供する。

【解決手段】単一元素からなる原子層が単層若しくは複数層で構成する導体層と、導体層を構成する元素同士間の原子間結合よりもより安定な結合を形成する単一又は復数の元素からなる原子層が単層若しくは複数層で構成する拘束層とからなり、前記導体層と拘束層の原子同士が原子的整合状態(ヘテロ構造)で積層することを特徴とする回路材料の電気抵抗低下方法。

(もっと読む)

銅表面に対する表面還元、不動態化、腐食防止、および活性化のためのシステムおよび方法

【課題】

【解決手段】露出された導電材料を不動態化するシステムおよび方法は、処理チャンバ内に基板を配置する工程と、処理チャンバ内に水素種を注入する工程とを備える。処理チャンバ内で、水素種のプラズマが形成される。基板の上面から、表面層の種が還元される。還元された表面層の種は、処理チャンバから取り除かれる。

(もっと読む)

動的な液体メニスカスを用いたストレスフリーのエッチング処理

【課題】動的な液体メニスカスを用いたストレスフリーのエッチング処理

【解決手段】パターン形成された半導体基板上の不均一性を平坦化および制御するためのシステムおよび方法は、パターン形成された半導体基板を受け取る工程を備える。パターン形成された半導体基板はパターン内の複数の特徴を導電性配線材料で満たされ、導電性配線材料は過剰部分を有する。過剰部分のバルクは除去され、過剰部分の残りの部分は不均一性を有する。不均一性はマッピングされ、不均一性を補正するために、最適の液体が決定され、動的液体メニスカスエッチング処理レシピが作成される。そして、不均一性を補正して、過剰部分の残りの部分をほぼ平坦化するために、動的液体メニスカスエッチング処理レシピを使用した動的液体メニスカスエッチング処理が実施される。

(もっと読む)

低KのCVD材料の勾配堆積

【課題】 全体として低いkをもつILDを提供し、ILDに内在する接着性の欠陥に対する抵抗性だけでなく、ILDと基板との間の良好な接着性を提供する構造体と方法を提供すること。

【解決手段】 全般的に低い誘電率、半導体基板への良好な接着、及び熱循環によるクラッキングへの良好な抵抗性を有する、半導体デバイスのための誘電体層(12)である。誘電体層(12)は、誘電率の勾配をもつ誘電体層を提供するために、誘電体材料の堆積条件の連続的変化を含むプロセスによって生成される。

(もっと読む)

基板処理方法、プラズマ室および半導体デバイス

【課題】

【解決手段】基板処理のシステムおよび方法には、プラズマ室に基板を装填しプラズマ室の圧力を所定の圧力設定値に設定することが含まれる。プラズマ領域を構成するいくつかの内面が約200℃以上の処理温度に加熱される。プラズマを形成するために処理ガスがプラズマ領域に注入され、基板が処理される。

(もっと読む)

無電解堆積のエンドポイントを検出するための装置および方法

基板の表面に向けて電磁放射を方向付けて、該基板の該表面上の部材から反射された該電磁放射の強度の変化を1つ以上の波長で検出することによって無電解堆積プロセスをコントロールするための装置および方法。一実施形態において、該基板が検出機構に対して移動されると、無電解堆積プロセスステップの検出された終了が測定される。別の実施形態において、多数の検出ポイントが、該基板の該表面にわたる該堆積プロセスの状態を監視するために使用される。一実施形態において、該検出機構は該基板上で無電解堆積流体に浸される。一実施形態において、コントローラは、記憶されたプロセス値、異なる時間に収集されたデータの比較、および種々の算出された時間依存データを使用して無電解堆積プロセスを監視、記憶および/またはコントロールするために使用される。 (もっと読む)

銅メタライゼーションのためのALD窒化タンタルの集積

窒化タンタル/タンタルバリア層を堆積させるための方法および装置が、集積処理ツールでの使用のために提供される。遠隔発生プラズマによる洗浄ステップの後、窒化タンタルは原子層堆積法で堆積され、タンタルはPVDで堆積される。窒化タンタル/タンタルは、堆積された窒化タンタルの下の導電性材料を露呈するために、誘電体層の部材の底部から除去される。場合によって、さらなるタンタル層が、除去ステップの後に物理気相堆積法で堆積されてもよい。場合によって、窒化タンタル堆積およびタンタル堆積は同一の処理チャンバで生じてもよい。シード層が最後に堆積される。 (もっと読む)

改良されたグローバルデュアルダマシン平坦化のためのシステム、方法、及び装置

【課題】

【解決手段】パターン化半導体基板(100)を平坦化する方法及びシステムは、パターン化半導体基板を受領する工程を含む。パターン化半導体基板(100)は、パターン内の多数の特徴部に充填された導電相互接続材料(120)を有する。導電相互接続材料は、過堆積(112)を有する。過堆積は、局所的な不均一性を有する。過堆積の全体部は、過堆積(120)を平坦化するために除去される。実質的に局所平坦化された過堆積は、大域的な不均一性を決定するためにマッピングされる。実質的に局所平坦化された過堆積は、大域的な不均一性を実質的に除去するためにエッチングされる。

(もっと読む)

デュアルダマシンによる半導体装置の製造方法

【課題】 放熱性が良好で、製造コストが低く、微細加工に好適なデュアルダマシンによる半導体装置の製造方法を提供する。

【解決手段】 基板1上に無機層間膜5、有機層間膜6、シリコン酸化膜からなる下部マスク7、シリコン窒化膜からなる上部マスク8を形成し、上部マスク8上にシリコン酸化窒化膜からなり膜厚が20乃至100nmであるカバーマスク10を形成する。そして、反射防止膜11及びレジスト膜12を形成する。次に、レジスト膜12をマスクとして、反射防止膜11、カバーマスク10、下部マスク7をエッチングする。そして、カバーマスク10をマスクとして、有機層間膜6及び無機層間膜5をエッチングしてビアホールを形成する。次に、上部マスク8をマスクとして有機層間膜6をエッチングして配線溝を形成する。

(もっと読む)

配線用シード膜および半導体装置の配線方法

【課題】 低コストにて歩留まり,信頼性,電気的特性の高い半導体装置を作製する。

【解決手段】 絶縁膜60上の下層絶縁膜61に銅の下層配線62を形成(S61)した後、プラズマCVD法により層間絶縁膜63,ストッパ膜64を順次形成し、ストッパ膜64における下層配線62上に孔64aを形成してから、ドライエッチングして層間絶縁膜63にコンタクトホール63aを形成する(S62)。その後、上層絶縁膜65を形成しマスク66を介してドライエッチングすることにより、上層絶縁膜65に溝部65aを形成すると共に、コンタクトホール63a中の上層絶縁膜65を除去する(S63)。そして、バリア膜67を形成(S64)した後、Cu−Ni膜,Cu−Zn膜,Cu−Zn−Ni膜のうち何れかを堆積してシード膜68を形成する(S65)。

(もっと読む)

多層配線構造又は電極取り出し構造、電気回路装置、及びこれらの製造方法

【課題】 Al層上にCu層を接続性よく形成することができる、多層配線構造又は電極取り出し構造、電気回路装置、及びこれらの製造方法を提供することにある。

【解決手段】 アルミニウムの電極パッド56、57及び電極層77上に絶縁層79を形成する工程と、電極パッド56、57及び電極層77上において絶縁層79にビアホール70’を形成する工程と、ビアホール70’内に無電解Niメッキ層81を形成する工程と、無電解Niメッキ層81上にCu配線86を形成する工程とを有する、多層配線構造又は電極取り出し構造の製造方法。

(もっと読む)

配線構造

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造を提供する。

【解決手段】 半導体素子が形成された基板上に絶縁膜103が多層形成され、絶縁膜103に形成された配線溝およびビアホールに金属配線剤が充填されて、配線および接続プラグが形成された配線構造において、絶縁膜103のうち少なくとも一層が対電子線感光性を有する材料から形成されており、絶縁膜103の層間にはバリア絶縁膜104を有し、前記金属配線剤は銅を含むものである。

(もっと読む)

配線構造の製造方法

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造の製造方法を提供する。

【解決手段】 配線構造の製造方法が、半導体素子201の上にWプラグ203(下層配線)が形成された基板上に、対電子線感光性を有する材料を含む第二層間絶縁膜204(絶縁膜)を形成する工程と、第二層間絶縁膜204に電子線を照射して、第二層間絶縁膜204を露光する工程と、第二層間絶縁膜204を現像して未露光部を除去し、配線溝および/またはビアホールおよび/またはコンタクトホールを形成する工程とを有する。

(もっと読む)

多層配線構造

【課題】シールドによる配線容量の増加を抑え、シールド効果も補償できる多層配線構造を提供する。

【解決手段】半導体基板100上の酸化膜4上に所定の間隔で平行に配置された下層メタル配線3と、下層メタル配線3上の層間絶縁膜5上に下層メタル配線3と平行でかつ下層メタル配線3間に位置するように配置されたシールド用の配線メタル配線1と、メタル配線1上の層間絶縁膜6上に下層メタル配線3と重なるように配置された上層メタル配線2とから多層配線を構成し、シールド効果と同時に上層メタル配線2の全容量値の低減を図る。

(もっと読む)

多層スピンオン多孔性誘電体からなるlow−k配線構造

【課題】その中にマイクロトレンチを含まない低誘電体層間絶縁膜金属導体配線構造およびそのような構造の形成方法を提供する。

【解決手段】導体抵抗に対する制御は、第1の原子組成を有する多孔性の低誘電体層間絶縁膜の線とバイア誘電体層との間に位置する第2の原子組成を有する埋込みエッチング停止層により行われる。本発明の配線構造は、また、二重波形模様タイプの配線構造を形成する際に助けになるハードマスクを含む。第1および第2の組成は、エッチング選択性が少なくとも10:1またはそれ以上になるように選択され、特定の原子組成および他の発見できる量を有する多孔性の低誘電体層間絶縁膜有機材料または無機材料の特定のグルーブから選択される。

(もっと読む)

701 - 720 / 720

[ Back to top ]