Fターム[5F033HH17]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733)

Fターム[5F033HH17]の下位に属するFターム

Fターム[5F033HH17]に分類される特許

201 - 220 / 962

半導体装置

【目的】プロービング試験での導電パッド下に配置された金属配線上の絶縁膜のクラック発生を抑制することが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、導電パッドと、前記導電パッド上に配置され、前記導電パッドの一部が露出するように開口領域が形成された第1の絶縁膜と、前記導電パッドの下方に配置された第2の絶縁膜と、銅(Cu)を用いた配線を有し、前記第2の絶縁膜を介して前記導電パッドの下方に配置され、前記開口領域と重なる領域での最上層における前記配線の最大配線幅w(nm)と前記配線の被覆率R(%)とがある条件を満たすように配置された少なくとも1層の配線層と、を備えたことを特徴とする。

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

薄膜素子およびその製造方法

【課題】 製造に際し、当初、耐熱性の高い仮基板を用い、最終的に、耐熱性の低いフィルム基板を用い、仮基板を除去し、これにより得られた薄膜トランジスタパネルにおいて、画素電極(薄膜)が破損しにくいようにする。

【解決手段】 仮基板51上に形成された分離層52上に画素電極2を形成する。この場合、画素電極2下以外の領域における分離層52が膜減りしたとしても、その上に下地絶縁膜1を形成し、仮基板51および分離層52を除去すると、下地絶縁膜1の下面に平板状の画素電極2が凹んだ状態で埋め込まれることになるので、画素電極2が破損しにくいようにすることができる。

(もっと読む)

半導体装置

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置を提供する。

【解決手段】半導体装置は、主表面1aを有するガラス基板1と、主表面1a上に設けられ、チャネル領域11と、チャネル領域11の両側に位置するソース領域9およびドレイン領域13とが形成されたポリシリコン膜7と、ポリシリコン膜7に接触するように設けられたゲート絶縁膜17と、ゲート絶縁膜17を介してチャネル領域11に向い合う位置に設けられたゲート電極21とを備える。ポリシリコン膜7は、50nmを超え150nm以下の厚みを有する。ソース領域9およびドレイン領域13は、ポリシリコン膜7の頂面7aからポリシリコン膜7の底面7cにまで達して形成されている。

(もっと読む)

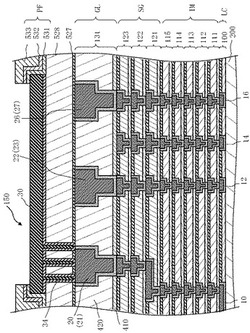

マスクを使用せずに導電性ビアに対して裏面位置合わせを行うことによる半導体構成部品の製造方法

半導体構成部品(90)を製造する方法が、回路面(54)と、裏面(56)と、導電性ビア(58)とを有する半導体基板(52)を提供するステップと、導電性ビア(58)の端子部分(76)を露出するために、基板(52)の一部分を裏面(56)から除去するステップと、端子部分(76)を封入するポリマー層(78)を裏面(56)に堆積するステップと、次いで、ポリマー層(78)および端子部分(76)の端部を平坦化して、ポリマー層(78)に埋め込まれた自己整合導体を形成するステップとを含む。導電性ビア(58)に電気的に接触させて、端子接点(86)や裏面再分配導体(88)等の追加の裏面要素を形成することもできる。半導体構成部品(90)は、半導体基板(52)と、導電性ビア(58)と、およびポリマー層(78)に埋め込まれた裏面導体とを有する。積重ね半導体構成部品(96)が、電気的に互いに通じる位置の整合した導電性ビア(58)を有する複数の構成部品(90-1、90-2、90-3)を有する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】Au系微細金属配線を線幅制御性良く形成することを可能とする半導体装置の製造方法を提供すること。

【解決手段】基板1上の絶縁膜2の上にAuを主材料とする金属配線層3を形成し、金属配線層3上にマスク用W層4を形成し、マスク用W層4上にレジスト層を形成してこのレジスト層をパターニングし、パターニングされたレジスト層5をマスクとしてマスク用W層4を反応性イオンエッチング法によりパターニングし、パターニングされたマスク用W層4をマスクとして金属配線層3を、アルゴンと酸素の混合ガスを用いる反応性イオンエッチング法により選択的に除去した後、マスク用W層4を反応性イオンエッチング法により除去することによってAu系金属配線を形成する金属配線形成工程を備えることを特徴とする半導体装置の製造方法を構成する。

(もっと読む)

半導体装置の製造方法

【目的】従来よりも比抵抗の低いW膜のプラグ或いは配線が得られる半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜に開口部を形成する工程(S106)と、前記開口部の少なくとも底面に、ルテニウム(Ru)膜を形成する工程(S112)と、前記Ru膜が形成された前記開口部内に、水素(H2)還元による化学気相成長(CVD)法によりタングステン(W)膜を埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一つとする。

【解決手段】チャネル形成領域にSiOxを含む酸化物半導体層を用い、電気抵抗値の低い金属材料からなるソース電極層及びドレイン電極層とのコンタクト抵抗を低減するため、ソース電極層及びドレイン電極層と上記SiOxを含む酸化物半導体層との間にソース領域またはドレイン領域を設ける。ソース領域またはドレイン領域は、SiOxを含まない酸化物半導体層または酸窒化物膜を用いる。

(もっと読む)

薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物

【課題】パターンの不良が減少した薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物を提供する。

【解決手段】基板上に導電性物質からなる導電膜を形成する段階と、導電膜上にネガティブフォトレジスト組成物からなるエッチングパターンを形成する段階と、エッチングパターンをエッチングマスクとして利用して導電膜をエッチングし、導電膜パターンを形成する段階とを含み、ネガティブフォトレジスト組成物は、アルカリ現像液に溶解性を有するヒドロキシル基を含有するノボラック樹脂10〜50重量部、第1光酸発生剤(特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、第2光酸発生剤(第1光酸発生剤とは構造の異なる特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、架橋結合剤1〜20重量部および溶媒10〜90重量部を含む。

(もっと読む)

半導体装置の作製方法

【課題】 レジスト材料の利用効率を向上させて、作製コストの削減を目的としたレジス

トパターンの作製方法、レジストパターンの除去方法、半導体装置の作製方法を提供する

ことを課題とする。

【解決手段】 本発明は、減圧下で、被加工物上に、感光剤を含む組成物を吐出してレジ

ストパターンを形成するステップを有することを特徴とする。また、前記レジストパター

ンをマスクとして前記被加工物をエッチングするステップ、若しくは、前記レジストパタ

ーンに、フォトマスクを介して前記感光剤の感光波長域の光を照射するステップ、前記レ

ジストパターンをマスクとして前記被加工物をエッチングするステップ、前記被加工物上

の前記レジストパターンを除去するステップを有することを特徴とする。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】一般的なウエハ・レベル・パッケージ・プロセスでは、メッキ・プロセス中におけるスクライブ領域のアルミニウム系パッド電極の腐食を防止するために、製品領域における有機系保護膜と同層のパッド保護用樹脂膜でパッド電極をカバーしている。しかし、これでは再配線形成後にスクライブ領域のパッド電極に対するプローブ検査が実行できない。

【解決手段】本願発明は、ウエハ・レベル・パッケージ方式の半導体集積回路装置の製造方法において、チップ領域およびスクライブ領域の有機系保護膜を相互に連結した一体の膜パターンとし、ペレタイズ工程においては、スクライブ領域中央部の有機系保護膜を含む表層部分を先ず、レーザ・グルービングで除去することで幅広の溝を形成し、その後、この溝内の中央部をダイシング処理することで、ここのチップ領域に分離するものである。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】配線抵抗の上昇を抑制したまま、EM特性を改善させる半導体装置或いはその製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、絶縁膜に開口部を形成する工程(S106)と、開口部内に、ケイ化物の形成エネルギーがCuケイ化物の形成エネルギーよりも小さい金属含有膜を形成する工程(S108)と、前記金属含有膜が形成された開口部内に銅(Cu)膜を埋め込む工程(S112)と、Cu膜上に、300℃未満の温度でCuとSiとを含有する化合物膜を選択的に形成する工程(S120)と、を備えたことを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】W−CSPにおいて、絶縁樹脂を塗布した後の半導体ウエハーの反りを防止することで薄型、小型化された半導体装置を提供する。

絶縁樹脂からのアウトガスの発生量が少ない半導体装置を提供する。

【解決手段】

半導体基板1上に形成された絶縁層12と、この絶縁層12上に形成されたインダクター13と、このインダクター13を被覆する樹脂封止層14とを備えてなり、前記インダクター13が形成されていない領域の絶縁層12の少なくとも一部が除去されている。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子機器

【課題】端子間の接合性に優れ高い信頼性を備えたものにするとともに、端子の狭ピッチ化も容易に対応できる半導体装置、半導体装置の製造方法、及び電子機器を提供する。

【解決手段】本発明の半導体装置1は、半導体基板10と、半導体基板10に形成された貫通孔7内に設けられるとともに、半導体基板10の能動面10Aと反対側の裏面10Bに部分的に突出する貫通電極5と、を有し、貫通電極5は、樹脂コア9と、樹脂コア9の少なくとも一部を覆う導電膜15と、を有し、貫通孔7は、内壁面7aの少なくとも一部が能動面10A側に向かって貫通孔7の内径を狭めるテーパー形状となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】 ビアホールの微細化及び高アスペクト比化が進むと、銅からなるシード層でビアホールの内面を連続的に覆うことが困難になる。

【解決手段】 半導体基板(10)の上に絶縁膜(20)が形成されている。絶縁膜に凹部(21)が形成されている。凹部の内面を第1の導電膜(22)が覆う。島状組織(25)が、第1の導電膜の表面に離散的に分布する。島状組織は、銅に対して、第1の導電膜の濡れ性よりも高い濡れ性を有する。凹部が、銅または銅合金からなる導電部材(31)で充填されている。

(もっと読む)

半導体装置

【課題】金属配線と金属酸化物を有する層を形成する際、電蝕といわれる腐食の発生をおさえることにより、半導体装置の動作特性および信頼性を向上させ、歩留まりの向上を実現することを目的とする。

【解決手段】配線は、耐酸化性金属からなる第1の層と、その上に形成されたアルミニウムもしくはアルミニウムを主成分とする第2の層と、その上に形成された耐酸化性金属からなる第3の層からなる3層構造とし、前記配線と電気的に接続する金属酸化物を有する層を有する。また、第2の層の上面及び下面は第1及び第3の層と接し、側面は酸素とアルミニウムを含む酸化層と接する。

(もっと読む)

半導体装置

【課題】抵抗値を調整可能な半導体装置をコンパクト化する。

【解決手段】基板接続領域と、外部配線接続領域と、基板接続領域と外部配線接続領域との間に設置される抵抗調整領域とを、1つの電極パッドに形成し、コンパクト化する。電極パッドの抵抗調整領域に対してトリミングを行うことによって、電極パッドの基板接続領域と外部配線接続領域との間の抵抗値を調整することができる。これによって、抵抗値を調整可能な半導体装置をコンパクト化することができる。

(もっと読む)

半導体装置の製造方法

【課題】シード膜の酸化を抑制して、電気的信頼性の低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有する基板100の少なくとも凹部1aの内面1b上に、シード膜5を形成する工程と、シード膜5上に、シード膜5の構成材料より酸化されやすい材料からなる保護膜6を形成する工程と、保護膜6に熱処理を施す工程と、熱処理が施された保護膜6の少なくとも一部を除去し、シード膜5の少なくとも一部を露出させる工程と、少なくとも一部が露出したシード膜5に電流を供給して、シード膜5上に凹部1aに埋め込まれるように電解めっきによりめっき膜7を形成する工程と、凹部1aに埋め込まれた部分以外のめっき膜7を除去する工程とを具備することを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置、およびその作製方法

【課題】アクティブマトリクス型表示装置等の半導体装置において、トランジスタの駆動能力を低下させることなく寄生容量の容量値を低減することを課題の一とする。または、寄生容量の容量値を低減した半導体装置を低コストに提供することを課題の一とする。

【解決手段】トランジスタのゲート電極と同一の材料層で形成される配線と、ソース電極またはドレイン電極と同一の材料層で形成される配線との間に、ゲート絶縁層以外の絶縁層を設ける。

(もっと読む)

201 - 220 / 962

[ Back to top ]