Fターム[5F033HH23]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | 高融点金属の合金 (485) | TiW (366)

Fターム[5F033HH23]に分類される特許

161 - 180 / 366

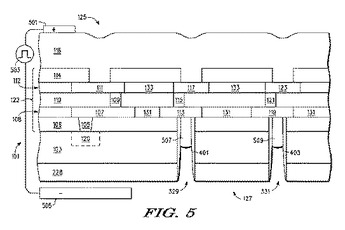

電気メッキを利用した導電ビア形成

導電ビアを形成する方法について説明され、そして該方法は、シード層を半導体基板(103)の第1面(125)に形成する工程であって、該半導体基板が該第1面を第2面(127)の反対側に含む、前記シード層を形成する工程と、ビアホール(329)を、該半導体基板の該第2面側の半導体基板中に形成する工程であって、該ビアホールが該シード層を露出させる、前記ビアホールを形成する工程と、そして電気メッキ法で導電ビア材料(601,603)を該ビアホールに、該材料が該シード層上に堆積するように充填する工程と、を含む。一つの実施形態では、連続導電層(116)を該シード層の上に形成し、かつ該シード層に電気的に接続する。該連続導電層は、電気メッキ法で導電ビア材料を充填する際の電流供給源として機能することができる。  (もっと読む)

(もっと読む)

多孔質低誘電率層の製造方法及び構造、相互接続処理方法及び相互接続構造

【課題】多孔質低誘電率層を形成する方法が、記載されている。

【解決手段】CVDプロセスは、基板に導入され、ここで、枠体前駆体及びポロゲン前駆体は供給される。枠体前駆体の供給の終了期間において、CVDプロセスの生成物の密度と否定的に相関している少なくとも一つの堆積パラメータの値は、減少する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、微細化しても剥離が生じ難い金属層を導電膜上に形成することを図ることを目的とする。

【解決手段】集積回路12が形成され、集積回路12に電気的に接続された電極14を有する半導体基板10に、電極14を覆うように第1の導電膜20を形成する。第1の導電膜20をエッチングして第1の導電膜パターン24を形成する。第1の導電膜パターン24を覆うように第2の導電膜26を形成する。第2の導電膜26に電流を流して行う電解メッキによって、第2の導電膜26上に、全体が第1の導電膜パターン24とオーバーラップするように金属層30を形成する。金属層30をマスクとして第2の導電膜26をエッチングして、全体が第1の導電膜パターン24とオーバーラップするように第2の導電膜パターン32を形成する。

(もっと読む)

半導体装置の製造方法

【課題】パワートランジスタを有する半導体装置の信頼性を向上させる技術を提供する。

【解決手段】素子を形成した半導体ウェハ1の主面に、素子と電気的に接続するように堆積した第1導体膜14および第2導体膜15に所望のパターンを形成する工程であり、まず、半導体ウェハ1を第1の回転速度で回転させた状態で、半導体ウェハ1の主面に対して薬液17を供給することにより、第2導体膜15に対してウェットエッチング処理を施す(工程100)。エッチング終了後、薬液17が半導体ウェハ1の主面に残るように、回転速度を第1の回転速度よりも遅い第2の回転速度に変更し、その状態で半導体ウェハに純水19を撒水することにより、純水19が半導体ウェハ1の主面に残されるようにした状態で薬液17を洗浄する(工程101)。続いて、第1導体膜14に対してドライエッチングを施す(工程102)。

(もっと読む)

電子デバイス及びその製造方法

【課題】信頼性の高い電子デバイス、及び、その製造方法を提供する。

【解決手段】電子デバイスは、ベース基板12と配線パターン14とを有する配線基板2と、電極22が形成された半導体チップ20と、半導体チップにおける電極が形成された面25に形成された樹脂突起30と、樹脂突起上に形成された電気的接続部42を含む、電極に電気的に接続された配線40と、を有し、電気的接続部が配線パターンに接触するように、配線基板に搭載された半導体装置3と、配線基板と半導体装置とを接着する接着剤4とを含む。配線40は、第1の層44と、第1の層上に形成された、第1の層よりも延性の高い材料で構成された第2の層46とを含む。第1の層における樹脂突起と重複する領域には、ひび割れが形成されており、第2の層における樹脂突起と重複する領域には、ひび割れが形成されていない。

(もっと読む)

半導体装置

【課題】表面保護膜や層間膜などの配線被覆膜の剥がれやひび割れの進行を防止することができる半導体装置を提供すること。

【解決手段】この半導体装置は、半導体チップ1と、半導体チップ1上に積層された保護膜2と、保護膜2上に突出する凸型端子3と、凸型端子3に接着される半田ボール4とを備えている。半導体チップ1の基体をなす半導体基板7上には、第1配線層8、第1層間膜9、第2配線層10、第2層間膜11、第3配線層12および最上層配線被覆膜15が半導体基板7側からこの順に積層されている。そして、半導体基板7の周縁から所定幅だけ内側の位置においては、最上層配線被覆膜15の表面から第2層間膜11および第1層間膜9を貫通して半導体基板7の表層部に達する溝18が半導体基板7の素子形成領域Bを取り囲んで形成されている。そして、この溝18には、保護膜2が入り込んでいる。

(もっと読む)

半導体装置

【課題】表面保護膜や層間膜などの絶縁膜の剥がれの発生を防止することができる半導体装置を提供すること。

【解決手段】この半導体装置は、半導体チップ1と、半導体チップ1上に積層された応力緩和層2と、応力緩和層2上に突出する接続パッド3と、接続パッド3に接着される半田ボール4とを備えている。半導体チップ1は、多層配線構造を有しており、この半導体チップ1の基体をなす半導体基板7上には、第1配線層8、第1層間膜9、第2配線層10、第2層間膜11、第3配線層12および表面保護膜15が半導体基板7側からこの順に積層されている。そして、表面保護膜15の周縁部22および、表面保護膜15の表面から半導体基板7の表面7Aに達する各絶縁膜(第1層間膜9、第2層間膜11および表面保護膜15)の各側面(9A、11A、15A)には、無機薄膜21が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高いBGAを有する半導体装置を提供する。

【解決手段】第1の主面上にパッド電極53を形成された半導体基板の第2の主面から前記パッド電極53に到達するビアホールVHを形成する工程と、前記ビアホールVH内を含む前記半導体基板の第2の主面上に絶縁膜を形成する工程と、前記絶縁膜上に緩衝層60を形成する工程と、前記ビアホールVHの底部の絶縁膜をエッチング除去する工程と、前記ビアホールVHを通して、前記パッド電極53と電気的に接続され、かつ前記ビアホールVHから前記緩衝層60上に延びる配線層64を形成する工程と、前記配線層64上に導電端子66を形成する工程と、前記半導体基板を複数の半導体チップ51Aに分割する工程と、を具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗値を向上させつつ高集積化が可能な薄膜抵抗を備えた半導体装置およびその製造方法を提供する。

【解決手段】薄膜抵抗9が樹脂層10の表面の厚さT方向の凹部16および凸部17に沿って形成されていることを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置の製造装置

【課題】配線溝への埋め込み特性が良好で、信頼性の高い半導体装置を作製することができる半導体装置の製造方法および半導体装置の製造装置を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、配線溝103が設けられた絶縁膜102を形成する工程(a)と、絶縁膜102上に導電性バリア膜104およびシード膜105を順次形成する工程(b)と、シード膜105上に電解めっき法により電解めっき膜106を形成する工程(c)とを備えている。工程(c)では、半導体基板101の基板面に対して70度以上90度以下の方向から光を照射しながら、電解めっきを行う。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体基板の能動面に形成された金属層に傷が付かないようにすることを目的とする。

【解決手段】集積回路が形成された半導体基板10の集積回路に電気的に接続された電極12を有する第1の面16に応力緩和層20を形成し、応力緩和層20及び電極12を覆うように導電膜22を形成し、導電膜22上に導電膜22の一部が露出する開口24を有するようにメッキレジスト層26を形成し、導電膜22に電流を流して行う電解メッキによって導電膜22のメッキレジスト層26からの露出部上に金属層28を形成する。その後に、メッキレジスト層26を除去する。その後に、金属層28をマスクとして、導電膜22の金属層28からの露出部をエッチングして除去する。その後に、金属層28上にソルダレジスト層30を形成する。その後に、半導体基板10の第1の面16とは反対の第2の面32に保護層34を形成する。

(もっと読む)

半導体装置

【課題】キャパシタの信頼性や品質を確保しつつ、ウェハ工程完了後にキャパシタの容量を調整できる半導体装置を提供する。

【解決手段】容量調整用キャパシタを、同一の半導体基板に対して複数備え、容量調整用キャパシタがパッシベーション膜によって被覆された半導体装置であって、複数の容量調整用キャパシタは、同一層の電極間がそれぞれ層内繋ぎ配線によって連結されて1つのキャパシタブロックを構成しており、層内繋ぎ配線によって連結された各層の電極のうち、少なくとも1層の電極と当該電極間を繋ぐ層内繋ぎ配線とが、同一の導電材料からなる薄膜抵抗体として構成され、薄膜抵抗体のうち、層内繋ぎ配線に相当する部位の少なくとも1箇所に光を選択的に照射して部位を断線させることにより、キャパシタブロックの容量が調整可能である。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体基板の能動面に形成された金属層に付いた傷を除去することを目的とする。

【解決手段】集積回路が形成された半導体基板10の集積回路に電気的に接続された電極12を有する第1の面18に電極12を覆うように導電膜18を形成し、導電膜18上に導電膜18の一部が露出する開口20を有するようにメッキレジスト層22を形成し、導電膜18に電流を流して行う電解メッキによって導電膜18のメッキレジスト層22からの露出部上に金属層24を形成する。その後に、メッキレジスト層22を除去する。その後に、半導体基板10の第1の面16とは反対の第2の面26に樹脂層28を形成する。その後に、金属層24をマスクとして、導電膜18の金属層24からの露出部をエッチングして除去するとともにエッチングによって金属層24の表面をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】表面にパッド電極を有する半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板上にトレンチ型ゲート構造の縦型MISFETを形成し、ゲート配線及びソース配線を形成してから、最上層の表面保護膜をスピンコート法で形成する。それから、ゲートパッド電極形成予定位置に開口部28aを有するレジストパターンRP1を表面保護膜上に形成し、レジストパターンRP1をエッチングマスクとして表面保護膜をエッチングすることで表面保護膜に開口部29aを形成する。開口部29aから露出されるゲート配線により、ゲートパッド電極が形成される。レジストパターンRP1の開口部28aの平面形状は、四角形状をベースとするが、後で半導体チップとなる半導体装置領域10Aの角部44aに最も近い部分を、丸みを持たせて、その角部44aから離れる方向に後退させた形状とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】Cu配線のCu拡散防止性能を向上する。

【解決手段】酸化シリコン膜39の上面、配線溝42の側壁部の酸化シリコン膜39の表面、配線溝42の底部の酸化シリコン膜31bの上面およびスルーホール34の側壁部の酸化シリコン膜31bの表面に、アンモニアプラズマ処理を施す。これにより、例えば厚さ10nm未満の薄い窒化シリコン膜が形成される。この結果、酸化シリコン膜39の上面、配線溝42の側壁部の酸化シリコン膜39の表面、配線溝42の底部の酸化シリコン膜31bの上面およびスルーホール34の側壁部の酸化シリコン膜31bの表面部分の膜質、清浄度、電気的な安定性を向上でき、Cuの拡散防止性能を向上させることが可能となる。

(もっと読む)

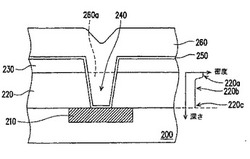

半導体装置とその製造方法及び電子装置

【課題】絶縁層と絶縁層との密着性を高め、半田バンプシア強度、半田バンププル強度を高め、半導体装置の基板実装後の信頼性を向上し得る半導体装置とその製造方法及び半導体装置を使用した電子装置の提供。

【解決手段】本発明は、半導体基板21の表面に絶縁層23が設けられ、該絶縁層上に導電層24,25が設けられ、該導電層上に半田バンプ26が設けられた半導体装置において、前記導電層に、前記絶縁層側に突出する楔部28Aを少なくとも1箇所有することを特徴とする半導体装置20Aを提供する。

(もっと読む)

半導体モジュール、電子機器および半導体モジュールの製造方法

【課題】チップサイズの拡大を抑制しつつ、層間接続の信頼性を向上させる。

【解決手段】半導体基板1a〜1cのスクライブラインSLの位置に溝4a〜4cを設け、半導体基板1a〜1cを積層した後、半導体基板1a〜1cの切断面に設けられた溝4a〜4c内に導電材料11を充填する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、微細化しても剥離が生じ難い配線を形成することを図ることを目的とする。

【解決手段】集積回路が形成された半導体基板10の、集積回路に電気的に接続された電極12を有する面に、凹部24を有するように樹脂層20を形成する。樹脂層20及び電極12を覆うように導電膜30を形成する。樹脂層20の凹部24の内側面及び底面上方で導電膜30の一部が露出する開口42を有するようにメッキレジスト層40を導電膜30上に形成する。導電膜30に電流を流して行う電解メッキによって導電膜30のメッキレジスト層40からの露出部上に金属層50を形成する。メッキレジスト層40を除去する。金属層50をマスクとして、導電膜30の金属層50からの露出部をエッチングして除去する。

(もっと読む)

半導体ウェハ及び半導体ウェハの製造方法

【課題】バリアメタル膜上に形成される金属めっき膜から、その金属成分が層間絶縁膜に拡散することを防止すること。

【解決手段】層間絶縁膜6、バリアメタル膜9、Cuシード膜10及びCuめっき膜11の成膜領域に関して、バリアメタル膜9、Cuシード膜10、Cuめっき膜11を成膜する時のウェハ外周領域での各端部位置が、上層になるほど、層間絶縁膜6の端部位置よりも段階的にウェハ内側にくるように形成する。これにより、Cuシード膜10及びCuめっき膜11の下には、必ずバリアメタル膜9が存在することになる。その結果、Cuシード膜10やCuめっき膜11を形成した後の工程における熱処理中に、Cuシード膜10やCuめっき膜11からCuが層間絶縁膜6中に異常拡散して、デバイス特性を変動させることを防止できる。

(もっと読む)

半導体装置及びその製造方法、並びに電子部品

【課題】ウエハレベルCSP化された半導体装置において、所定の入光面以外の面から光が入射することを抑制し、搭載された集積回路やデバイスなどが赤外〜紫外域の電磁波によって誤作動を生じないパッケージを実現するための構造を有する、半導体装置及び製造方法、並びにこの半導体装置を用いた電子部品を提供する。

【解決手段】本発明の半導体装置10は、一方の面に電極3を備える半導体からなる基板2、前記基板の一方の面に配された絶縁部4、前記基板の他方の面に配された第一保護部6、を少なくとも備えた構造体11を有する。また、半導体装置10は、前記構造体の側面部の一部又は全部を被覆する第二保護部7を有することにより構成され、前記第一保護部及び前記第二保護部は何れも、遮光性を有することを特徴とする。

(もっと読む)

161 - 180 / 366

[ Back to top ]