Fターム[5F033HH23]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | 高融点金属の合金 (485) | TiW (366)

Fターム[5F033HH23]に分類される特許

201 - 220 / 366

半導体装置およびその製造方法

【課題】熱変化等により導電部にかかる応力を低減し、導電部の破壊や断線等の損傷を防止して、貫通電極における電気的な接続信頼性を向上した半導体装置を提供すること。

【解決手段】本発明の半導体装置1は、基板2の一方の面に配された第一の導電部3と、前記基板の他方の面から前記第一の導電部の少なくとも一部が露呈するように、前記基板内に設けられた貫通孔4と、前記貫通孔内の側面および露呈された前記第一の導電部を覆うとともに、前記基板の他方の面上を覆うように延びて配され、前記第一の導電部と電気的に接続される第二の導電部6と、前記基板の他方の面上において、前記第二の導電部上に配され電気的に接続される第三の導電部8と、を備えることを特徴とする。

(もっと読む)

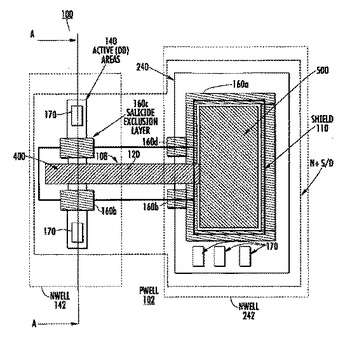

フローティングゲートトンネリング素子構造体のシールド

フローティングゲートトンネリング素子をシールドする方法とその構造体。標準的なCMOSプロセスを用いて、電界酸化物に囲まれた基板内に形成された第1および第2のドープウェル領域により定義される2つの活性領域内のゲート酸化物上にフローティングゲートを配置する工程と、前記フローティングゲートを囲むようにフローティングゲートシールド層を形成する工程を含む方法。前記フローティングゲートは、前記第1のドープウェル領域内の活性領域上の第1のフローティングゲート部および前記第2のドープウェル領域内の活性領域上の第2のフローティングゲート部を含む。前記第1のドープウェル領域と前記第1のフローティングゲート部との間にファウラーノルドハイムトンネリングのための適当な電圧カップリングが発生しうるよう、前記第1のフローティングゲート部は第2のフローティングゲート部より実質的に小さくなっている。トンネリングの方向は、前記ドープウェル領域の1つに高電圧を印加することにより決定される。  (もっと読む)

(もっと読む)

配線基板

【課題】腐食性ガス雰囲気中に置かれても電極パッドの腐食を防止可能であると共に機能を阻害せずコンパクトな配線基板を低コストに提供する。

【解決手段】第2配線層16が層間絶縁膜13のビアホール13aにて第1配線層15と接続され、その第2配線層16が第1配線層15から離れた位置まで延出されて引き出され、その第2配線層16の延出部分16aの一部が保護絶縁膜14の開口部14aから露出して電極パッドPadが形成されている。そのため、半導体チップ10が腐食性ガス雰囲気中に置かれると、電極パッドPadが腐食性ガスに直接晒される。しかし、電極パッドPadは腐食性ガスに耐性のある形成材料を用いた第2配線層16の一部であるため、腐食性ガスにより電極パッドPadが腐食されることはなく、電極パッドPadの断線不良を防止できる。

(もっと読む)

半導体装置とその製造方法

【課題】コスト増を招くことなく高いインダクタンス値を得る。

【解決手段】半導体基板10にインダクタ素子40が形成される。粉末状の磁性体が分散された樹脂材で形成され、インダクタ素子40を覆う磁性樹脂体30、66を備える。また、巻き線41における配線間の隙間を埋めるように、透磁率の低い材料として非磁性の樹脂層42が製膜されている。樹脂剤42は磁性樹脂層30を形成する材料の中、磁性体が添加されない樹脂で形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】生産効率が高く、信頼性及び歩留まりの高い半導体装置の製造方法を提供する。

【解決手段】半導体基板1の裏面研削(バックグラインド)を行い、半導体基板1を薄くする。次に、裏面研削で生じたダメージ層7の除去をこの段階では行わずに、レジスト層8を半導体基板の裏面に選択的に形成する。次に、レジスト層8をマスクとして半導体基板1をエッチングし、ビアホール9を形成する。次に、当該エッチング工程で利用したエッチング装置内に半導体基板1を配置したまま、ビアホール9形成と連続的にレジスト層8を除去する。このように、エッチング工程とその後のアッシング工程とを一つの処理装置で連続的に行う。次に、半導体基板1の裏面のダメージ層7の除去及び、ビアホール9の内壁面の平坦化工程についても、上記アッシング工程と同一装置で連続的に行う。

(もっと読む)

半導体装置及び半導体モジュール

【課題】小型化を実現しつつ所望の抵抗値を得ることができる半導体装置を提供する。

【解決手段】半導体装置は、半導体チップ2と、半導体チップ2の一方の面側に合成樹脂によって形成された凸部材6,7と、少なくとも一部が凸部材上に形成された膜状の抵抗素子8とを備えている。上記構成により、膜状の抵抗素子8を半導体チップ2の第1面2Aから離れる方向に引き延ばすことができ、少ない占有面積で所望の抵抗値を持った薄膜抵抗8を実現できる。

(もっと読む)

個別電子コンポーネントのマトリクスを形成する方法および形成されるマトリクス

本発明は、基板(100)上にアクティブ層(101)を形成する段階および少なくとも基板(100)が出現するまで、トレンチ(102)をアクティブ層(101)内に形成することでコンポーネントを個別化する段階を含む、電子コンポーネント(111)のマトリクスを製造する方法に関する。この方法は、アクティブ層(101)上に機能材料の層(102)を蒸着する段階と、前記トレンチ(102)を充填し、電子コンポーネント(111)の上側面に薄膜(115)を形成するように、材料の層(103)上に感光性樹脂(104)を蒸着する段階と、トレンチの樹脂の部分の露光を少なくしつつ樹脂(104)を放射線に少なくとも部分的に曝露する段階と、適切に露光された部分を除去するように樹脂(104)を現像する段階と、現像段階の後、外面に現われる機能材料の層(103)の部分を除去する段階と、樹脂の残り部分を除去する段階とを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】酸化ハフニウム等の高誘電率絶縁膜を用いたMIMキャパシタにおいて、高容量密度と高容量精度を両立し、MIMキャパシタの耐圧低下を防止し、リーク電流増大を低減する技術を提供する。

【解決手段】第一の金属配線700、加工された容量膜405、加工された上部電極215、第三の金属配線702から構成されるMIMキャパシタにおいて、第一の金属配線を被覆するように酸化シリコンからなる層間絶縁膜を形成した後、この第一の金属配線直上の層間絶縁膜の接続孔層に相当する領域に対し、第一の金属配線の上面が露出しないようにこの層間絶縁膜に第一の開口部を形成し、次に、第一の金属配線表面が露出するように第一の開口部の内部に第二の開口部を形成した後、容量膜、第三の金属配線を形成されることにより達成される。

(もっと読む)

回路基板及び電子機器

【課題】高周波信号の伝送特性を向上させることができるとともに、高周波ノイズの放射を低減することができる回路基板、及び当該回路基板を備える電子機器を提供する。

【解決手段】本発明の回路基板は、電気回路の信号線S1〜S5と電気的に接続されており、回路基板の表面と裏面との間であって回路基板の表面に対して交差する方向に延びるスルーホールT10〜T12と、スルーホールT10〜T12に対して隣接して設けられており、電気回路の基準電位を定めるグランド線G1〜G6に接続され、回路基板の表面に対して交差する方向に延びるスルーホールT20,T22,T23,T30〜T32を備え、スルーホールT10〜T12の各々は、少なくとも一つ以上のスルーホールT20,T22,T23,T30〜T32と隣接して配置される。

(もっと読む)

半導体素子の配線形成方法

【課題】本発明は、配線の抵抗を減らして電気的な特性を向上させるための半導体素子の配線形成方法を提供する。

【解決手段】所定の構造物が形成された半導体基板上に非晶質シリサイド膜または非晶質TiSiN膜を形成する段階と、上記非晶質シリサイド膜または非晶質TiSiN膜の上に配線用導電膜を形成する段階を含む。

(もっと読む)

半導体構造体及びその製造方法

【課題】突出部が形成される前面及び凹部が形成される後面を有する半導体ユニットを含む半導体構造体及びその製造方法を提供する。

【解決手段】本発明の半導体構造体は、パッケージ単位体300を含み、前記パッケージ単位体300の前面には突出部である補助プラグパターン170が形成され、前記半導体ユニットの後面には凹部が形成される。また、本発明の半導体構造体の製造方法は、半導体ユニットの前面に突出部である補助プラグパターン170を形成するステップと、前記半導体ユニットの後面に凹部を形成するステップと、を含む。

(もっと読む)

半導体装置及びその製造方法、回路基板並びに電子機器

【課題】配線及び外部端子が高密度に形成できる半導体装置及びその製造方法、この半導体装置を搭載した回路基板並びにこの半導体装置を有する電子機器を提供する。

【解決手段】複数の電極9を有する半導体素子2に、複数の樹脂層と、電極9に電気的に接続する複数の配線4と、該配線4に電気的に接続する複数の外部端子7が形成された半導体装置1であって、複数の配線4のうち、その一部の第1の配線4aが、1つの樹脂層(第1の樹脂層3)又は積層された複数の樹脂層の底面に形成され、複数の配線4のうち、その一部を除いた第2の配線4bが、1つの樹脂層(第1の樹脂層3)又は積層された複数の樹脂層の表面に形成され、第1の配線4aが、複数の外部端子7のうちの、少なくとも半導体素子2の最も外周部側に位置する外部端子7に接続されており、外部端子7が、鉛フリーはんだボールから形成されているものである。

(もっと読む)

半導体装置

【課題】ウエハレベルCSP等の半導体パッケージ構造を有する半導体装置において、微細化が可能であると共に、絶縁樹脂層との界面で剥離が発生しにくい導電部を備え、導電部における良好な導電性が確保される半導体パッケージ構造を有する半導体装置を提供する。

【解決手段】半導体装置1は、一面に電極3を配してなる半導体基板2と、該半導体基板の一面を覆うように配され、かつ、前記電極が露呈するように開口部を有する絶縁樹脂層4と、前記絶縁樹脂層の一部を覆うように配され、前記開口部を介して前記電極と電気的に接続されるシード層5と、前記シード層上の外周域に配された無機薄膜層6と、前記シード層及び前記無機薄膜層上に配され、前記シードを介して前記電極と電気的に接続される導電部7と、を少なくとも備える。

(もっと読む)

パッシベーション及びポリイミドにより包囲されたコンタクト及びその製造方法

半導体装置(10)は、ボンディングパッド(28)と最終相互接続層(16)との間にコンタクトを有し、そのコンタクトは、最終相互接続層(16)とボンディングパッドとの間にバリアメタル(26)を含む。パッシベーション層(18)及びポリイミド層(22)の両方により、最終相互接続層(16)とボンディングパッド(28)とが分離される。パッシベーション層(18)は、最終相互接続層(16)と接するように第一の開口(20)を形成すべくパターン化される。また、ポリイミド層(22)も、パッシベーション(18)を貫通する第一の開口(20)よりも内側にあって、それゆえにより小さな第二の開口(24)を残存させるようにパターン化される。次に、バリア層(22)が最終相互接続層(16)と接して堆積されて、ポリイミド層(22)により境界を形成する。次に、バリア(26)と接してボンディングパッド(28)が形成されると、その後、ボンディングパッド(28)に対してワイヤボンド(30)が形成される。  (もっと読む)

(もっと読む)

半導体装置、電子部品、回路基板及び電子機器

【課題】本発明の目的は、パッケージサイズがチップサイズに近く、応力吸収層とは別に、熱ストレスを効果的に吸収することができる半導体装置及びその製造方法、回路基板並びに電子機器を提供することにある。

【解決手段】パッケージサイズがチップサイズに近く、応力吸収層とは別に、熱ストレスを効果的に吸収することができる半導体装置である。半導体装置150は、電極158を有する半導体チップと、半導体チップの上に設けられる応力緩和層としての樹脂層152と、電極158から樹脂層152の上にかけて形成される配線154と、樹脂層152の上方で配線154に形成されるハンダボール157と、を有し、樹脂層152は表面に窪み部152aを有するように形成され、配線154は窪み部152aの上を通って形成される。

(もっと読む)

半導体装置の製造方法

【課題】ボッシュプロセスを利用して形成されたビアホールを有する半導体装置の製造方法において、ビアホール内での均一な成膜を達成することを目的とする。

【解決手段】マスク層2をマスクとし、ボッシュプロセスを利用して半導体基板1の一方の面から他方の面方向へエッチングし、当該半導体基板1の所定領域を貫通するビアホール3を形成する。次に、マスク層2を除去する。次に、ドライエッチング法によりスキャロップ形状4を除去し、ビアホール3の内壁面を平坦化させる。続いて、ビアホール3内に絶縁膜やバリア層などを均一に成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】ビアホールを有する半導体装置及びその製造方法において、ビアホール内におけるバリア層の被覆不足防止とビア抵抗を制御することの両者を同時に達成することを目的とする。

【解決手段】その表面上にパッド電極3を有する半導体基板1を準備する。次に、半導体基板1の裏面から表面方向にエッチングし、パッド電極3を露出させるビアホール8を形成する。次に、スパッタリング法またはPVD法、及び逆スパッタリング(エッチング)によりビアホール8内に第1のバリア層11を形成する。この逆スパッタリングによりビアホール8底部のバリア層が除去され、パッド電極3が露出される。次に、ビアホール内で露出したパッド電極3上に第2のバリア層12を形成する。第2のバリア層12の膜厚のみを調節することでビア抵抗を制御する。

(もっと読む)

半導体装置

【課題】本発明の目的は、配線の、幅の異なる部分の連結部分に生じる応力を減らすことにある。

【解決手段】半導体装置は、半導体チップ10と、幅の異なる第1、第2の配線の連結部分34と、連結部分34とオーバーラップする位置に形成されたパッド40と、パッド40上に形成されてなるバンプ44と、連結部分34とパッド40との間に位置して連結部分34の全体を覆うように形成されてなる緩衝層50と、連結部分34と緩衝層50との間及び緩衝層50とパッド40との間に、それぞれ形成されてなる無機絶縁層60,62と、を含む。緩衝層50は、樹脂を除く材料であって、無機絶縁層60,62よりも柔らかい材料から形成されてなる。

(もっと読む)

配線基板および半導体装置

【課題】配線が高密度化しても導電層が絶縁層から剥離することのない配線基板および半導体装置を提供する。

【解決手段】絶縁層12の一面12aに形成された凹部13によって導電層14の下面側が絶縁層12の内側に食い込むので、導電層14の形成時に、導電層14と絶縁層12との間に配された密着層15や給電層16が、導電層14の配線幅W1よりも内側まで抉られてしまっても、導電層14が絶縁層12から剥離してしまうことが防止される。

(もっと読む)

半導体装置

【課題】本発明の目的は、パッドとバンプの接合部分の強度を上げることにある。

【解決手段】半導体装置は、集積回路12が作り込まれた半導体チップ10と、集積回路12に電気的に接続されるように半導体チップ10上に形成されておりパッド22を一部に有する配線20と、パッド22の上面に形成されてなるバンプ40と、を含む。配線20は、パッド22を除いて、上面がAlから形成されている。パッド22の上面は、TiN又はTiWから形成されている。バンプ40の少なくとも下面はAuから形成されている。

(もっと読む)

201 - 220 / 366

[ Back to top ]