Fターム[5F033HH23]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | 高融点金属の合金 (485) | TiW (366)

Fターム[5F033HH23]に分類される特許

141 - 160 / 366

半導体装置および半導体装置の製造方法

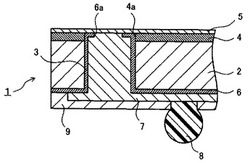

【課題】半導体基板の貫通配線部において、貫通孔底部での絶縁層の被覆性が向上され、電気的絶縁性の低下や接続不良が改善された半導体装置を提供する。

【解決手段】貫通孔3を有する半導体基板2の表面に、該貫通孔3と同径の開口4aを有する第1の絶縁層4が被覆され、その上に第1の配線層5が開口4aを覆い形成されている。また、貫通孔3内および半導体基板2の裏面に第2の絶縁層6が被覆されている。第2の絶縁層6は、第1の配線層5と内接するように形成され、内接部に第1の絶縁層4の開口4aよりも小径の開口6aを有している。さらに、貫通孔3内に第2の配線層7が充填・形成され、この第2の配線層7は第2の絶縁層6の開口6aを介して第1の配線層5に内接している。

(もっと読む)

表示装置の製造方法

【課題】フォト工程の低減を図った表示装置の製造方法。

【解決手段】第1導電型TFTと第2導電型TFTの各形成領域に、半導体層、第1絶縁膜、ゲート電極が形成され、前記半導体層のチャネル領域の各外側に第1導電型不純物領域が形成されている基板上に第2絶縁膜を形成し、前記第1導電型TFTの形成領域において当該ゲート電極を露出させることなく、前記第2導電型TFTの形成領域において当該ゲート電極のうち半導体層と交差する各辺の一部を露出させるようにして、ドレインおよびソースの各電極の接続用のコンタクトホールを形成し、多層導電層によって、前記第1導電型TFTの形成領域における前記各コンタクトホール、前記第2導電型TFTの形成領域において前記各コンタクトホールのゲート電極の一部を被うようにして、ドレインおよびソースの各電極を形成し、第2導電型不純物をドープして、半導体層に第2導電型不純物領域を形成する。

(もっと読む)

半導体素子の製造方法

【課題】コンタクトホールにおける断線や電流リークがなく、また、絶縁層上に形成された配線パターン同士の残渣による短絡なく、穴径に対する穴深さの比率が例えば2.4以上の高アスペクト比を有する低い導通抵抗のコンタクトホールを形成可能な、半導体素子の製造方法を提供する。

【解決手段】半導体基板1上に第1絶縁層3を形成し、この第1絶縁層を貫通して半導体基板を露出させる第1穴部3aを形成し、第1絶縁層上にAlまたはAl合金からなる導電膜8を成膜し、この導電膜を加熱して流動化させ冷却した後にパターン化して中継電極10を形成し、第1絶縁層上に中継電極を覆う第2絶縁層12を形成し、この第2絶縁層を貫通して中継電極を露出させる第2穴部12aを形成し、第2絶縁層上に第2穴部を介して中継電極と電気的に接続する配線パターンを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗素子による半導体装置の厚みの増加や立体構造による導通不良、および抵抗素子と電極との間の界面によって生じる導通性の低下などに囚われない、接続信頼性の高い抵抗素子を備えた半導体装置を提供する。

【解決手段】第一電極1を一面に備える半導体基板2、半導体基板2の一面にあり、第一電極1と整合して第一開口部を設けた第一絶縁層3、第一絶縁層3に積層し、第一開口部と連通する第二開口部を配した第二絶縁層4、前記第一開口部と、前記第二開口部と、第二絶縁層4とを覆うように配したシード層5、および第一電極1と電気的に接続し、前記第二開口部を覆うようにシード層5上に配した第二電極6、を少なくとも備える半導体装置であって、シード層5は多層をなし、少なくとも第二電極6に接したシード層5上部は第二電極6と同じパターンであり、シード層5下部は抵抗素子として機能することを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置

【課題】 Cuの層間絶縁膜中への拡散を防止することができるCu配線を備えた半導体装置を実現する。

【解決手段】 半導体装置1は、半導体基板10の基板面10aの上方に、順番に積層形成された第1配線層33、第2配線層34及び第3配線層35を備えている。第1配線層33は、SOI基板などの半導体基板10の基板面10a上に形成されており、層間絶縁膜12、側面バリアメタル層15、Cu配線18及び上面バリアメタル層19を備えている。Cu配線18の上面部18aは、側面バリアメタル層15と同様の材料により形成された上面バリアメタル層19により覆われている。ここで、上面バリアメタル層19の幅は、上面部18aの幅よりも大きく形成されている。この上面バリアメタル層19により、Cu配線18から上層の層間絶縁膜12へのCuの拡散を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明の目的は、パッケージサイズがチップサイズに近く、応力吸収層とは別に、熱ストレスを効果的に吸収することができる半導体装置及びその製造方法、回路基板並びに電子機器を提供することにある。

【解決手段】パッケージサイズがチップサイズに近く、応力吸収層とは別に、熱ストレスを効果的に吸収することができる半導体装置である。半導体装置150は、電極158を有する半導体チップと、半導体チップの上に設けられる応力緩和層としての樹脂層152と、電極158から樹脂層152の上にかけて形成される配線154と、樹脂層152の上方で配線154に形成されるハンダボール157と、を有し、樹脂層152は表面に窪み部152aを有するように形成され、配線154は窪み部152aの上を通って形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明の目的は、大型化することなく、Q値が高いスパイラルインダクタを有する半導体装置及びその製造方法を提供することにある。

【解決手段】半導体基板10の電極14が形成された面に樹脂層20が形成されている。スパイラルインダクタを構成する配線30は、電極14に電気的に接続され、樹脂層20の、半導体基板10の電極14が形成された面と対向する下面22とは反対の上面24に形成されている。配線30は、スパイラル状に延びる軸線に交差する幅方向の両端部36と、両端部36間の中間部38と、を有する。中間部38の少なくとも一部は、樹脂層20の上面24に接触する。配線30の一部と、樹脂層20の上面24と、の間にはギャップが形成されている。少なくとも両端部36は、ギャップを介して樹脂層20の上面24から間隔をあけて位置する。

(もっと読む)

半導体集積回路用インダクタ及びその製造方法

【課題】広大な断面積が得られ、抵抗値を著しく低下させることができてQ値を向上させることができると共に、膜厚の均一性が高い半導体集積回路用インダクタ及びその製造方法を提供する。

【解決手段】ダマシン法により形成された多層配線層の最上層配線層18上に、スパイラルインダクタ40が形成されている。このインダクタ40は、最上層配線29が形成された絶縁膜17a上に、この最上層配線29に接触するようにしてバリアメタル層をパターン形成し、その後、全面に保護絶縁膜を形成した後、この保護絶縁膜におけるバリアメタル層上の部分を開口し、その上に更にバリアメタル層を全面に形成し、このバリアメタル層をメッキ電極としてCu膜をメッキにより厚く形成し、このCu膜を湿式エッチングすることにより、形成する。このため、膜厚が厚く、線幅が広いインダクタ40を形成することができる。

(もっと読む)

導電膜パターンの形成方法、デバイスの製造方法、及び液滴吐出ヘッドの製造方法

【課題】均一な膜厚の導電膜パターンを形成する方法と、これを用いたデバイスの製造方法及び液滴吐出ヘッドの製造方法を提供する。

【解決手段】本発明の導電膜パターンの形成方法は、開口部18、25を有する基板10に第1の金属薄膜からなる導電膜下地パターン21aを形成するとともに、導電膜下地パターン21aの形成箇所と開口部18、25との間に第1の金属薄膜からなるダミー導電膜下地パターン22a、23aを形成する工程と、導電膜下地パターン21a及びダミー導電膜下地パターン22a、23aにめっき処理してこれらの上に第2の金属薄膜21b、22b、23bを形成し、導電膜下地パターン21aと第2の金属薄膜21bからなる導電膜パターン21、及びダミー導電膜下地パターン22a、23aと第2の金属薄膜22b、23bからなるダミー導電膜パターン22、23を形成する工程と、を有する。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】デュアルダマシン(Dual-Damascene)法を用いた多層Cu配線の形成工程を簡略化する。

【解決手段】層間絶縁膜45上に形成したフォトレジスト膜51をマスクにして層間絶縁膜45をドライエッチングし、層間絶縁膜45の中途部に形成したストッパ膜46の表面でエッチングを停止することによって配線溝52、53を形成する。ここで、ストッパ膜46を光反射率の低いSiCN膜によって構成し、フォトレジスト膜51を露光する際の反射防止膜として機能させることにより、フォトレジスト膜51の下層に反射防止膜を形成する工程が不要となる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、配線層間に形成される酸化膜により、配線層間の接続抵抗値が低減され難いという問題があった。

【解決手段】本発明の半導体装置では、第1の配線層3と第2の配線層とを接続する開口領域8〜12を埋設する第1の金属層14〜18上のスピンコート樹脂膜21に開口部22が形成されている。開口部22内では、メッキ用金属層23を構成するCr層とCuメッキ層24とが接続している。この構造により、第1の金属層14〜18上のCr層は、結晶粒子間が広くなり、粗な領域となる。そして、Cr層の粗な領域には、第2の金属層19とCuメッキ層24との合金層が形成され、接続抵抗値が低減される。

(もっと読む)

半導体装置およびその製造方法

【課題】貫通電極に空洞部が形成されることを防止する。

【解決手段】第1半導体基板1の表面および貫通孔2の内壁面を保護膜3で覆った状態で導体にて構成されたパッド8の表面に導体膜11を結晶成長させる。この導体膜11にて、貫通電極4を形成する。このように、パッド8の表面に主に結晶成長させ、保護膜3には結晶成長がほとんど起こらない選択成長によって貫通電極4を形成しているため、空洞の無い、良好な貫通電極4とすることができる。このため、断線・配線抵抗の増加を防止できると共に、EM耐性の低下等も防止することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、樹脂層によって半導体基板に与える影響を減らすことを目的とする。

【解決手段】半導体装置は、集積回路12が形成され、集積回路12に電気的に接続された電極14を有する半導体基板10と、半導体基板10の電極14が形成された面に形成された樹脂層20と、電極14に電気的に接続され、樹脂層20の上に形成された配線30と、を含む。樹脂層20は、熱可塑性樹脂からなる第1の層22と、第1の層22と配線30の間に介在する熱硬化性樹脂からなる第2の層24と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を高めることができ、且つ、製造コストの上昇を防ぐことができる半導体装置の製造方法を提供する。

【解決手段】ステップS101で、半導体素子の表面上に形成された表面保護膜およびパッド電極を覆うように、TiW膜をスパッタ法で形成する。引き続いて、TiW膜上にAu膜を形成する。ステップS103で、Au膜をメッキ用電極として用いて、Au膜上にAuバンプを形成する。ステップS105で不要なAu膜を除去して、ステップS106で不要なTiW膜を除去する。ステップS107で、不要なTiW膜が除去された領域に残留するヨウ素を除去する。

(もっと読む)

半導体装置

【課題】金属抵抗素子の形成位置を画定するための写真製版技術における露光時にレジスト膜中に定在波が発生するのを防止して金属抵抗素子の寸法バラツキを低減する。

【解決手段】金属抵抗素子27の下地絶縁膜23は、金属抵抗素子27の長手方向において、金属抵抗素子27の接続孔25,25間における上面の40%以上の部分を占める上側に凸の1つの曲面を備えている。金属抵抗素子27はその長手方向において下地絶縁膜23の曲面に起因して、コンタクト、コンタクト間における上面及び下面の40%以上の部分を占める上側に凸の1つの曲面を備えている。金属抵抗素子27の形成位置を画定するための写真製版技術における露光時に、金属抵抗素子27を形成するための金属膜の上面及び下面で露光光の反射光は上記曲面により散乱されるので、反射光と入射光によるレジスト膜中での定在波の発生が防止される。

(もっと読む)

半導体装置の製造方法

【課題】高価な製造装置を設置することなく、銅を含む配線層の腐食が発生せず、配線層を構成する銅とポリイミド前駆体との反応による配線層の劣化を防止することができる半導体装置の製造方法を提供する。

【解決手段】少なくとも銅を含有する配線層6を形成する工程と、配線層6上にポリイミド層7を形成する工程を有する半導体装置の製造方法であり、ポリイミド層7を形成する工程は、ポリイミド層7を不活性ガス中で重合することを特徴としている。

(もっと読む)

半導体装置およびその製造方法

【課題】最下層配線に埋め込み配線を有する半導体装置の信頼性を向上させる。

【解決手段】

半導体基板1の主面にMISFETQn,Qpが形成され、その主面上に絶縁膜10,11が形成されている。絶縁膜10,11にはコンタクトホール12が形成されてプラグ13が埋め込まれている。プラグ13が埋め込まれた絶縁膜11上には、絶縁膜14,15,16が形成され、絶縁膜14,15,16に開口部17が形成されて配線20が埋め込まれている。絶縁膜15は、開口部17を形成するために絶縁膜16をエッチングする際のエッチングストッパ膜であり、シリコンと炭素を含有する。絶縁膜11は吸湿性が高く、絶縁膜15は耐湿性が低いが、それらの間に絶縁膜14を介在させ、絶縁膜14を絶縁膜11よりもSi(シリコン)原子の数密度が大きな膜とすることで、電気的に弱い界面が形成されるのを防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】 トランジスタ回路とブリーダー抵抗回路とを備えた半導体装置において、ブリーダー抵抗の抵抗値変動を抑制することを目的とする。

【解決手段】 トランジスタ構造の上に層間絶縁膜107を介して金属膜としてバリアメタル膜104及び配線膜103を積層してなるトランジスタ回路と、ポリシリコン膜よりなるブリーダー抵抗102の上に層間絶縁膜107を介して金属膜として配線膜103を積層するか、ブリーダー抵抗102と接合する部分のみをバリアメタル膜104としたブブリーダー抵抗回路とを備えるので、ポリシリコン膜であるブリーダー抵抗102に及ぶ応力が少なくなり、ブリーダー抵抗102の抵抗値変動を抑えることができる。また、トランジスタ回路の配線として用いられる金属膜についてはバリアメタル膜が存在するので、配線の信頼性を損なう事もない。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】高温処理を行った場合でも素子の信頼性の劣化を抑制する。

【解決手段】磁気ランダムアクセスメモリは、磁化方向が固定された固定層11と磁化方向が反転可能な記録層13と固定層及び記録層の間に設けられた非磁性層12とを有する磁気抵抗効果素子MTJを具備するメモリセルアレイであって、磁気抵抗効果素子の下方に配置された前記メモリセルアレイ内の全ての導電層2、4、5は、W、Mo、Ta、Ti、Zr、Nb、Cr、Hf、V、Co、Niからなる群の中から選択された元素を含む材料で形成されている。

(もっと読む)

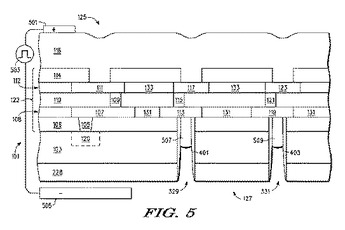

電気メッキを利用した導電ビア形成

導電ビアを形成する方法について説明され、そして該方法は、シード層を半導体基板(103)の第1面(125)に形成する工程であって、該半導体基板が該第1面を第2面(127)の反対側に含む、前記シード層を形成する工程と、ビアホール(329)を、該半導体基板の該第2面側の半導体基板中に形成する工程であって、該ビアホールが該シード層を露出させる、前記ビアホールを形成する工程と、そして電気メッキ法で導電ビア材料(601,603)を該ビアホールに、該材料が該シード層上に堆積するように充填する工程と、を含む。一つの実施形態では、連続導電層(116)を該シード層の上に形成し、かつ該シード層に電気的に接続する。該連続導電層は、電気メッキ法で導電ビア材料を充填する際の電流供給源として機能することができる。  (もっと読む)

(もっと読む)

141 - 160 / 366

[ Back to top ]