Fターム[5F033JJ13]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Au、Au合金 (649)

Fターム[5F033JJ13]に分類される特許

81 - 100 / 649

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

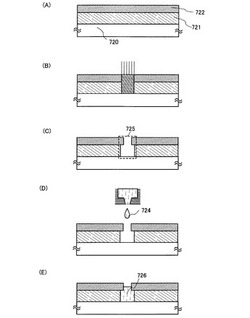

ビアホールの製造方法およびビアホールを有する半導体素子の製造方法

【課題】内部への埋め込み材料を増量させて放熱性向上効果を得ることが可能なビアホール構造を、ビアホール形成のための半導体基板へのエッチングの回数を少なくしつつ製造することのできるビアホールの製造方法およびビアホールを有する半導体素子の製造方法を提供する。

【解決手段】メタルマスク8は、メタルマスク10の開口23により露出させられた部分8aを有する。メタルマスク10は、メタルマスク8よりも厚く形成する。メタルマスク10の厚さは、開口23内のエッチングが半導体デバイス形成層4にほぼ到達すると同時に、開口22のエッチングがソース電極1に到達する厚さに設定する。

(もっと読む)

半導体装置

【課題】 製造が容易でかつ絶縁性に優れ、平坦な上面(表面)を持つパッシベーション構造を備えた配線構造を、低コストかつ短リードタイムで形成する、半導体装置を提供する。また、配線抵抗が小さくボンディング耐性が高い配線構造を提供する。

【解決手段】 所望の素子領域の形成された基板表面に形成された配線層と、前記配線層表面を覆う層間絶縁膜と、前記層間絶縁膜表面全体を覆うように形成された窒化シリコン膜と、前記窒化シリコン膜の上層に形成された最上層メタルとしての金層からなるメタル配線層と、前記窒化シリコン膜と前記メタル配線層との間に形成されたバリア層と、前記メタル配線層上に形成されたポリイミドからなる平坦化絶縁膜とを含み、前記バリア層と前記配線層は、前記窒化シリコン膜と前記層間絶縁膜に形成されたスルーホールを通じて接続されており、前記平坦化絶縁膜が一部領域で除去せしめられ、前記メタル配線層にボンディングがなされていることを特徴とする。

(もっと読む)

半導体装置

【課題】超高周波帯におけるシリコン基板による損失を低減すると共に、貫通配線のインダクタンス成分の影響を小さくした半導体装置を実現できるようにする。

【解決手段】半導体装置は、回路素子105が形成された半導体基板100と、半導体基板100の主面の上に形成された第1の誘電体層121と、第1の誘電体層121の上に形成された第2の誘電体層131と、第1の誘電体層121を貫通し、回路素子105と接続された第1の貫通配線122と、第2の誘電体層131を貫通し、第1の貫通配線122と接続された第2の貫通配線132とを備えている。第2の貫通配線132は、第1の貫通配線132よりもインダクタンスが小さい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】再配線のパターン形成後のレジストパターンの剥離性を確保しつつ、再配線のパターン形成前のレジストパターンとその下地との密着性を向上させる。

【解決手段】半導体チップ上に形成されたメタル膜5の表層には、レジスト膜6との密着性を上げる表面改質層16が形成され、表面改質層16を介してメタル膜5上に再配線7a〜7cが形成される。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】低伝導度領域ができるだけ少なくなるグラフェン配線構造が可能な半導体装置を提供する。

【解決手段】半導体装置は、触媒金属膜220と、グラフェン膜230と、コンタクトプラグ240と、調整膜250と、を備える。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対してコンタクトプラグと接続する領域と同方向に調整する。

(もっと読む)

半導体装置

【課題】本発明は、接続不良を抑制したコンタクト形成方法を備える半導体装置を提供するものである。

【解決手段】半導体装置は、配線層を備える第1の回路領域と、第1の回路領域の上に形成された絶縁膜と、絶縁膜の上に形成され、シリサイド膜を備える第2の回路領域と、配線層上に設けられ、配線層と電気的に接続された下部コンタクトと、下部コンタクト上に設けられ、下部コンタクトと前記シリサイド膜とを電気的に接続する上部コンタクトとを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】再配線間のリークを抑制しつつ、再配線のピッチを微細化するとともに、再配線上のビア開口時のマージンを上げる。

【解決手段】緩衝層4上には再配線7bが形成され、再配線7b上には表面層8bが形成されている。表面層8bは、再配線7bから幅方向にはみ出すようにして再配線7bに沿うように配置され、再配線7bよりもエッチング耐性が高い。

(もっと読む)

半導体デバイス

【課題】ストレスによる半導体回路の特性変動・劣化を抑制した半導体デバイスを提供する。

【解決手段】縦導体3は、半導体回路に隣接して半導体層1の厚み方向に設けられ、少なくとも一つは、半導体層1と対面する領域に、等軸晶領域を有するか、または、凝固点と融解点との温度差が50℃以上である。

(もっと読む)

半導体デバイス

【課題】応力による半導体回路の特性劣化を抑制した半導体デバイスを提供する。

【解決手段】縦導体は、半導体基板の厚み方向に設けられた微細孔を満たし、第1結晶組織301と第2結晶組織302とを含むナノコンポジット結晶構造を有する。ナノコンポジット結晶構造において、第1結晶組織301及び第2結晶組織302の少なくとも一方は、ナノサイズである。

(もっと読む)

半導体装置及び製造方法

【課題】 ビアホール上にオーミック電極が形成された半導体装置において、装置の小型化を図ること。

【解決手段】 本半導体装置は、基板10と、基板10上に形成された半導体層12と、半導体層上12に形成されたソースまたはドレイン電極を構成するオーミック電極20と、を備え、基板10及び半導体層12には、基板10及び半導体層12を貫通するビアホール30が形成され、ビアホール30は、少なくとも半導体層を貫通する第1ビアホール32と、第1ビアホール32下の基板10に形成された、第1ビアホール32より開口断面積が大きい第2ビアホール34と、を含み、オーミック電極20は、第1ビアホール32の上に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】基板に形成されたビアホール内のメタライズを改善すること。

【解決手段】本半導体装置の製造方法は、SiCを材料とする基板10を備える半導体装置100の製造方法であって、フッ化炭素を含むエッチングガス及びマスク14を用いて基板10の裏面をエッチングし、基板10の裏面から表面に向かって開口面積が次第に小さくなるテーパ形状を有する第1領域22を形成する第1工程と、次いで、フッ化硫黄を含むエッチングガス及びマスク14を用いて第1領域22の内側をエッチングし、第2領域24を形成する第2工程とを有し、基板10の表面に対する第2領域24の内壁面の傾斜角は、基板10の表面に対する第1領域22の内壁面の傾斜角より大きいことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】金属マスクを形成する工程を含む半導体装置の製造方法において、金属片が支持基板に付着することを防止する。

【解決手段】この製造方法は、支持基板10の表面10aに貼付された半導体ウェハ12上にネガレジストを塗布し、該ネガレジストを露光することにより所定のパターンを有するレジスト18を形成するレジスト形成工程と、半導体ウェハ12上にメッキ処理を施すことにより金属マスク20を形成したのちレジスト18を除去する金属マスク形成工程と、金属マスク20を介して半導体ウェハ12にエッチングを施すことにより、貫通孔12dを形成するエッチング工程と、金属マスク20を除去したのち、貫通孔12dの内面及び半導体ウェハ12の裏面12bに金属膜26を形成する金属膜形成工程と、半導体ウェハ12を支持基板10から取り外す取外し工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】基板に形成されたビアホール内のメタライズを改善すること。

【解決手段】本半導体装置の製造方法は、SiCを材料10とする基板を備える半導体装置の製造方法であって、フッ化炭素を含むエッチングガス及びマスク14を用いて基板10の裏面をエッチングし、基板10の表面から裏面に貫通するビアホール20を形成する工程を有し、ビアホール20成する工程は、基板10の裏面から表面に向かって開口断面積が次第に小さくなるテーパ形状を形成する工程であり、かつエッチング条件は、誘導結合プラズマ方式のドライエッチングを含み、ガス流量が、フッ化炭素=10〜200sccm、ガス圧力が、Press=0.1〜10.0Pa、誘導結合プラズマパワーが、ICP=100〜5000W、バイアスパワーが、Bias=10〜1000W、であることを特徴とする。

(もっと読む)

半導体装置及び製造方法

【課題】 基板及び表面層にビアホールが形成された半導体装置において、表面層の剥離及び破壊を抑制すること。

【解決手段】 本半導体装置は、基板10と、基板10上に設けられた基板10と異なる材料からなる表面層20と、表面層20上に設けられた電極パッド50と、を備え、基板10及び表面層20にはビアホール30が形成され、ビアホール30内には、電極パッド50と電気的に接続された金属層32が設けられ、ビアホール30の開口部の周囲には、ビアホール30を囲むように表面層20に溝22が形成されている。

(もっと読む)

半導体装置

【課題】ディッシング及び埋め込み不良のないパッド構造を短時間で安定して形成する。

【解決手段】基板100上に形成された第1の絶縁膜108Bに、複数のパッド配線109pを含むパッドが形成されている。第1の絶縁膜108B上に、前記パッドの少なくとも一部分の上に位置する開口部を有する第2の絶縁膜110が形成されている。複数のパッド配線109pのうち互いに隣り合う配線同士を電気的に接続するように配線接続部109qが設けられている。各パッド配線109pの幅W1は、各パッド配線109pの高さよりも小さく且つ配線接続部109qの幅W3よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

81 - 100 / 649

[ Back to top ]