Fターム[5F033MM08]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | 積層 (3,773) | 3層以上 (1,359)

Fターム[5F033MM08]に分類される特許

201 - 220 / 1,359

半導体装置

【課題】 パッド内での過度の電流集中を抑制することが可能なパッド構造を有する半導体装置を提供する。

【解決手段】 半導体基板の上に、絶縁性材料からなる第1の絶縁膜が形成されている。第1の絶縁膜の上に、導電材料からなるパッド部が形成されている。パッド部に電気的に連続し、第1の幅W1を有する配線部が形成されている。第1の絶縁膜の上であって、パッド部の外周線から第2の幅W2より内側の第1の領域に、複数の第2の絶縁膜が配置されている。配線部とパッド部との境界線に最も近い第2の絶縁膜を連ねる直線のうち、配線部をパッド部内に延長した領域と重なる部分が、パッド部の導電材料と交差する長さをL3としたとき、W1≦2×W2+L3を満たす。

(もっと読む)

半導体装置およびその製造方法

【課題】 デュアルダマシン法による配線構造の製造において、接続プラグ用のホールを通じて下層配線の表面に凹部をエッチング形成するとき、上層配線用の溝の底部が過剰エッチングされないようにする。

【解決手段】 TaNなどからなり、接続プラグに対応する開口を有する導電性膜パターン112をSiOCなどからなる層間絶縁膜111と113との間に設けた後、配線溝114、ホール115を形成する。次にTaN、Taなどからなる積層導電性膜116を堆積し、ホール115の底部の積層導電性膜116を除去し、さらに下層配線を構成するCu膜109を掘り込むエッチングを行う。このとき、導電性膜パターン112があるために配線溝114の底部の下にある層間絶縁膜111のエッチングを防止できる。その後、配線溝114およびホール115内にCuなどの導電性膜117を埋め込む。

(もっと読む)

トランジスタ及びその製造方法

【課題】Siチヤネルを有するNMOSとSiGeチャネルを有するPMOSで、NMOSには引張り歪みを与える、PMOSには、表面のダングリングボンドを減少させることができる半導体装置を提供する。

【解決手段】単結晶シリコン基板50の一部領域にシリコンゲルマニウムチャネル膜54aを形成し、PMOSトランジスタを、シリコン膜60aを形成し、NMOSトランジスタを形成する。単結晶シリコン基板、シリコンゲルマニウムチャネル膜、PMOSトランジスタ、NMOSトランジスタの表面上に、反応ガス、雰囲気ガス及び水素ガスを含む蒸着ガスを用いて、シリコン窒化膜82を形成し、PMOSトランジスタは、シリコンゲルマニウムチャネル膜表面のダングリングボンドの除去により、ホールスキャタリングが抑制され、NMOSトランジスタには引張り歪みを与えることにより動作特性の改善ができる。

(もっと読む)

半導体装置およびその製造方法

【課題】MIM容量素子形成時に生じる異常放電による容量絶縁膜の絶縁破壊を抑えることができて、高容量密度のMIM容量素子を得る。

【解決手段】半導体基板2上に、下部電極4−容量絶縁膜5−上部電極6からなるMIM容量素子1を有する半導体装置であって、上部電極4を構成する上部電極用金属膜は容量絶縁膜5との界面が、有機金属気相成長法(MOCVD)によりプラズマを用いないで堆積したアモルファス状のTiN膜などの金属窒化膜で構成されている。

(もっと読む)

電子デバイスの製造方法

【課題】接合熱処理温度が低くて済み、凝固後は高い融点を確保し得る高耐熱性の電子デバイス及びその製造方法の提供。

【解決手段】複数枚の基板WF1〜WFrのそれぞれは、縦導体31と、接続導体4とを有している。複数枚の基板WF1〜WFrのうち、隣接する基板WF1、WF2は、一方の基板WF2の接続導体(縦導体)31が、他方の基板WF1の接続導体4と、接合膜5によって接合されている。接合膜5は、第1金属または合金成分と、それよりも融点の高い第2金属または合金成分とを含み、凝固後の溶融温度が第1金属または合金成分の融点よりも高くなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】3次元デバイスのような多層配線を有する半導体装置をより簡単な工程で作製する製造方法を提供する。

【解決手段】第1層10と第2層20とを、それぞれのTSV6が略一直線上になるように積層する半導体装置の製造方法で、基板の上面に入出力回路を構成するトランジスタ3を形成し、トランジスタ3を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第1層の製造工程と、基板20を準備し、基板の上面に論理回路を構成するトランジスタ13を形成し、トランジスタ13を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第2層の製造工程と、第1層のTSV6と第2層のTSV6とが略一直線上になるように、第1層と第2層の、基板の反対側面を接続する接続工程と、第1層の基板1を除去する工程とを含む。

(もっと読む)

半導体装置

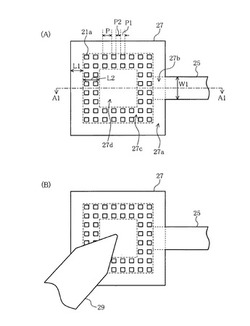

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

半導体装置とその製造方法、及び半導体ウエハ

【課題】半導体装置とその製造方法、及び半導体ウエハにおいて、個片化後の半導体チップがもとの半導体ウエハのどこに位置していたかを容易に特定すること。

【解決手段】複数のチップ領域Rcとスクライブ領域Rsとを有するシリコン基板20と、複数のチップ領域Rcの各々に対応する複数のモニタ素子Mと、スクライブ領域Rsに形成され、複数のモニタ素子Mの各々を電気的に接続する配線2とを有し、スクライブ領域RsにおけるダイシングラインX1〜X7、Y1〜Y7の位置をずらしたときに、配線2の異なる部分がダイシングされるようにして、配線2と複数のモニタ素子Mとの結線状態をダイシングラインX1〜X7、Y1〜Y7の位置に応じて可変にした半導体ウエハWによる。

(もっと読む)

半導体装置およびその製造方法

【課題】応力が加わった場合であっても、抵抗値が変動しない構造を備える半導体装置およびその製造方法を提供することにある。

【解決手段】半導体装置内のパッシベーション膜SN12と最上層アルミ配線Mとの間の領域に、金属抵抗素子層Rmを形成している。これにより、パッケージング工程以降のモールド応力による抵抗値の変動が少ない高精度抵抗素子が実現でき、高精度なアナログ回路を形成することができる。

(もっと読む)

積層回路材料

【課題】特性インピーダンスを小さくできるために、超高周波又は超高速信号の伝送時においても反射や放射が少なく、かつ低損失である回路材料を提供する。

【解決手段】単一元素からなる原子層が単層若しくは複数層で構成する導体層と、導体層を構成する元素同士間の原子間結合よりもより安定な結合を形成する単一又は復数の元素からなる原子層が単層若しくは複数層で構成する拘束層とからなり、前記導体層と拘束層の原子同士が原子的整合状態(ヘテロ構造)で積層することを特徴とする回路材料の電気抵抗低下方法。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜のストレスに耐え、絶縁膜からの酸素や水分の影響を抑制しつつ、エレクトロマイグレーションの耐性や配線間の耐圧も改善することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、(a)凹部102が形成された絶縁膜101上に、TaN膜103を成膜する工程と、(b)TaN膜103上に、Taよりも熱膨張係数が大きいTiを主成分とするTi膜104を成膜する工程と、(c)Ti膜104上に、Tiよりも熱膨張係数が大きいCuを主成分とするCu膜105を成膜する工程と、(d)Cuを、電解めっきにより、凹部102内に埋め込む工程とを含む。

(もっと読む)

EM保護が施された半導体ダイを形成する方法

【課題】電磁(EM)妨害あるいはEMIに対してある程度の保護を具備し半導体装置において、半導体ウエハからダイを低コストで形成する方法を提供する。

【解決手段】半導体ダイ12,13,14は、傾斜したサイドウォール35,36,37を有するように輸送テープあるいはキャリヤ・テープ38上に形成される。この傾斜サイドウォール上、および、底部表面上に導体40が形成される。導電材料である導体40は、ダイ12−14に対しEMIからの保護を提供する。

(もっと読む)

EM保護が施された半導体ダイを形成する方法

【課題】電磁(EM)妨害あるいはEMIに対してある程度の保護を具備した半導体装置において、低コストで、半導体ウエハからEM保護の施されたダイを形成する方法を提供する。

【解決手段】半導体ダイ12,13,14は、傾斜したサイドウォール35,36,37を有するように形成される。この傾斜サイドウォール上、および、半導体ダイの底部表面上に導体40が形成される。導電材料である導体40は、ダイ12−14に対しEMIから保護する。

(もっと読む)

ダマシンインターコネクトのエレクトロマイグレーション抵抗を向上させる界面層

【課題】、ダマシンインターコネクトのエレクトロマイグレーション特性を向上させるべく銅線内に保護キャップを形成する方法を提供する。

【解決手段】a)酸化物を含まない銅または銅合金107の露呈領域と誘電体の露呈領域とを含む基板100を、アルミニウムを含む化合物に、少なくとも約摂氏350度の基板温度で曝して、前記誘電体および前記銅または銅合金の層の両方の上にアルミニウムを含む第1の層を形成する工程と、(b)前記第1の層の少なくとも一部を化学的に修正して、アルミニウムを含むパッシベーション層109を形成する工程と、(c)前記パッシベーション層の上に誘電体層111.を堆積させる工程とを備える方法。

(もっと読む)

半導体装置の製造方法

【課題】金属配線に用いられるAlにCuを添加した合金導電膜の膜質を改善して、ストレスマイグレーション耐性を向上させること。

【解決手段】本発明の実施形態に係る半導体装置の製造方法は、Al−Cu膜の成膜後に予め決められた温度変化で冷却する工程が存在する。これにより、Al−Cu膜は、結晶粒と粗密差が生じる領域が従来例よりも狭くなってヒロックの発生が抑制される膜質に改善される。その後に続く製造工程における熱履歴によってヒロックの発生が抑制され、その結果、このAl−Cu膜を有する配線層から形成された配線のストレスマイグレーション耐性が向上する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体ウエハの裏面側を研削する工程において、主面側が汚染されることを抑制する。

【解決手段】裏面2b側を研削する半導体ウエハ20のスクライブ領域1bの交差部に、デバイス領域1aに積層される配線層5を構成する絶縁層(第1絶縁層)3と同様に主面2a上に複数の絶縁層3を積層する。また、デバイス領域1aに形成される複数の配線層5のうち最上層に配置される配線層(最上層配線層)5cに形成された配線(最上層配線)と同層に金属パターン10を形成する。さらに、この最上層配線を覆う絶縁層(第2絶縁層)9を、金属パターン10の上面にもこれを覆うように形成する。

(もっと読む)

半導体装置

【課題】低誘電率誘電体材料などからなる層間絶縁膜を用いた多層配線構造を有する半導体装置において、機械的ストレス又は熱的ストレスに起因する層間絶縁膜のクラック又は剥離等を確実に防止する。

【解決手段】半導体基板のチップ領域の外周部にシールリング4が設けられていると共に、当該チップ領域におけるシールリング4の近傍にチップ強度強化用構造体5が設けられている。チップ強度強化用構造体5は複数のダミー配線構造(例えばダミー配線構造5A〜5E等)から構成されている。各ダミー配線構造5A〜5E等はそれぞれ、最下層及び最上層の配線層のいずれか一方のみを含むか又はいずれも含まない2層以上の配線層に亘ってビア部を介して連続的に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

電子デバイスの製造方法および該方法により製造された電子デバイス

GaAs半導体基板(HS)を備えた電子デバイスにおいて、基板前面には半導体素子(BE)が、基板背面には多層の背面金属化部(RM)が設けられている。このような電子デバイスのために、背面金属化部の有利な積層体構造が提案される。たとえば背面金属化部は固着層としてAu層を有している。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】内部接続端子にクラックを生じさせない、信頼性を高めたパッケージの製造方法を提供する。

【解決手段】電極パッドを有する半導体集積回路を含む半導体チップが複数配置された半導体基板と、半導体基板上の再配線層とを有する半導体装置の製造方法であって、半導体集積回路の領域の間に位置するスクライブ領域の中に溝部を加工するため、溝部以外の領域を保護する保護マスクを半導体基板に張り付ける、保護マスク張り付け工程(S101)と、溝部を加工する溝部加工工程(S102)と、保護マスクを第1絶縁層の形成のためのスクリーンマスクとして使用して、溝部を覆うように第1絶縁層を形成する、第1絶縁層形成工程(S103)とを有することを特徴とする半導体装置の製造方法。

(もっと読む)

201 - 220 / 1,359

[ Back to top ]