Fターム[5F033MM28]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 膜厚の異なる複数の配線を有するもの (89)

Fターム[5F033MM28]に分類される特許

41 - 60 / 89

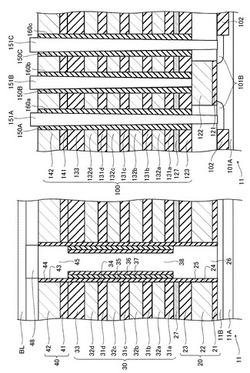

不揮発性半導体記憶装置及びその製造方法

【課題】安定した動作の積層型不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】電気的に書き換え可能なメモリセルが複数形成されるメモリセル領域と、メモリセルを制御する周辺回路を構成するトランジスタが形成される周辺回路領域とを備え、メモリセル領域には、半導体基板11上に対し垂直方向に、ソース側選択トランジスタ層20、メモリトランジスタ層30、及びドレイン側選択トランジスタ層40が積層されて形成される。メモリホール34内には、ブロック絶縁層(第1絶縁層)35、電荷蓄積層(特性変化層)36、トンネル絶縁層37、及びメモリ柱状半導体層38が形成される。周辺回路領域には、p−型領域101Aにプレーナ型トランジスタのソース/ドレイン領域101Bが形成され、メモリセル領域の複数の導電層の各々と同一平面上に形成され、且つ導電層と電気的に分断される複数のダミー配線層100が形成される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置70には、積層形成される配線膜6及び10から構成される配線層が設けられる。キャップ膜3上に形成される層間絶縁膜4の第1の開口部には、配線膜6が埋設される。配線膜6の底部及び側面部にはバリアメタル膜5が設けられる。層間絶縁膜4及び配線膜6上に形成されるキャップ膜7及び層間絶縁膜8の第2の開口部には、配線膜10が埋設される。配線膜10の底部及び側面部にはバリアメタル膜9が設けられる。層間絶縁膜8及び配線膜10上に形成される。配線膜10は配線膜6上に設けられ、配線膜10の端部は配線層6の端部よりも内側に設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】チップサイズを縮小することにより、LCDドライバの製造コストを低減させることのできる技術を提供する。

【解決手段】第1金属膜からなるバンプ6が形成されない領域のパッシベーション膜9上に、第2金属膜からなる容量素子7C、抵抗素子7Rまたはインダクタンス素子7L等の受動素子を形成する。第1金属膜は金膜、第2金属膜は金膜、ニッケル膜または銅膜であり、あるいは第1金属膜は下層をニッケル膜または銅膜とし上層を金膜とする積層膜、第2金属膜はニッケル膜または銅膜である。さらに、第1金属膜の厚さは第2金属膜の厚さと同じか、あるいは第2金属膜の厚さよりも厚く形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】金属ナノ微粒子を用いた、電極、配線形成方法では、金属ナノ微粒子溶液を塗布、印刷後抵抗値を落とすために200℃程度の熱処理が必要である。プラスチックなどのフレキシブル基板では、耐熱性が150℃程度であるため、この熱処理により基板の変形が出てしまう。

【解決手段】本発明は、ハロゲンを有するガスに金属ナノ微粒子を所望の形状に印刷した後に暴露する事によって、なんら過熱焼成することなく、金属電極、配線を形成できる。

(もっと読む)

半導体装置、電気光学装置、及び電子機器

【課題】構造を複雑化させることなく安定した特性が得られ、さらには抵抗素子を含む回路の高集積化を実現できる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、基板本体(基板)10Aと、基板本体10A上に形成された半導体素子(インバータINV1,INV2)と、半導体素子に接続された配線121,122と、配線121,122に形成された抵抗素子R1,R2とを備えており、配線121,122が、積層された複数の導電層131,132を有しており、異なる抵抗値を有する複数の抵抗素子R1,R2が、複数の導電層のうち少なくとも一部の導電層を用いて配線121,122に形成されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】外部接続用のパッドが形成される表層より一層下の配線層の配線密度を下げることなく、パッド下の層間絶縁膜のクラックを防止できる半導体装置を提供する。

【解決手段】表層より一層下の層に形成された配線のうち、パッド1の領域下を通過する配線3aの厚さを、パッド1の領域下から外れて配置される配線3bの厚さよりも薄くする。

(もっと読む)

半導体装置の製造方法

【課題】歩留りが高く、且つ、配線間容量を十分に低減できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板上に絶縁膜を形成する工程と、絶縁膜の内部に複数の配線溝を形成する工程と、複数の配線溝の内部に複数の配線を形成する工程と、絶縁膜及び複数の配線の上に、複数の配線間の領域のうち選択的に領域を露出する開口部を有するレジストマスクを形成する工程と、レジストマスクを用いたエッチングにより、複数の配線間の領域のうち選択的に露出した領域の絶縁膜を除去してエアギャップ溝を形成する工程と、レジストマスクを除去した後に、複数の配線上を覆うように層間絶縁膜を堆積することによってエアギャップを形成する工程とを含む。

(もっと読む)

半導体回路装置

【課題】 半導体回路装置の面積を増大させることなく、電源電圧安定化のための十分な容量を確保することができる半導体回路装置を実現する。

【解決手段】 トランジスタセル1の一方の端部は、グランド線6、絶縁層9、電源線7の順に半導体基板8の一の面に積層されてなるため、グランド線6および電源線7の配線方向の長さに対応した容量C1を形成することができるので、電源安定化に必要な十分な容量を確保することができる。また、グランド線6の上方に電源線7が積層されているため、容量を形成するための領域をトランジスタセル1間に確保する必要がない。さらに、グランド線6および電源線7を配置するために必要な面積を、グランド線6および電源線7を並列して配置する構造よりも小さくすることができる。

(もっと読む)

パターン形成方法および半導体装置の製造方法

【課題】 一回のエッチングで、深さの異なる複数のパターンを形成することができる、反射防止膜を用いてパターンを形成する工程を含む半導体装置の製造方法を提供すること。

【解決手段】 パターン形成方法は、被加工膜上にエッチング調整層からなるパターンを形成する工程と、前記調整層パターンを少なくとも覆うように反射防止膜を形成し、レジスト塗布、露光現像によりレジストパターンを形成する工程とを有し、前記被加工膜のエッチング条件下で、前記エッチング調整層がエッチングされることにより、前記エッチング調整層の有無で、異なる深さのパターンが形成されることを特徴とする。

(もっと読む)

アレイ基板及び配線形成方法

【課題】 2層配線を有するアレイ基板において、第1配線層上に形成される層間絶縁膜に加わる歪み(ストレス)を解消するとともに段差の形成を抑制し、層間絶縁膜におけるクラックの発生や第2配線層のエッチング残りを抑制する。

【解決手段】 表示部と、その周囲に配される額縁部とを有するアレイ基板である。少なくとも第1配線層と、第1配線層上に層間絶縁膜を介して形成される第2配線層とを有する。第1配線層の側壁の傾斜角度θ1は第2配線層の側壁の傾斜角度θ2よりも小さい。第1配線層の側壁の傾斜角度θ1は65°以下であり、第2配線層の側壁の傾斜角度θ2は70°以上である。また、第1配線層の膜厚d1は第2配線層の膜厚d2よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレイン領域のサイズが増大することがない局所配線構造を備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極22及び半導体基板11におけるゲート電極22の両側方にそれぞれ形成された第1のソースドレイン領域29A及び第2のソースドレイン領域29Bを有するトランジスタ12と、半導体基板11の上における第1のソースドレイン領域29Aを挟んでゲート電極22と反対側に形成されたゲート配線42と、ゲート配線42と第1のソースドレイン領域29Aとを接続する局所配線構造60とを備えている。局所配線構造60は、第1のソースドレイン領域29A及びゲート配線42の上面に跨って形成されたSiGe層61によって構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】FEOLレベルから正負とも低電圧の範囲で拡散工程中のチャージアップから被保護素子を保護し、且つ、拡散工程完了後は被保護素子の駆動に必要な正負両極性の高電圧を被保護素子に印加することが可能な半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11に形成され、被保護素子電極22を有する被保護素子21と、半導体基板11と電気的に接続された基板接続電極42を有する基板接続部41と、被保護素子電極22と基板接続電極42との間に形成されたヒューズ素子電極32を有するヒューズ素子部31とを備えている。ヒューズ素子電極32は、所定の電流を流すことにより切断可能に形成され、ヒューズ素子電極32が切断されていない状態において、被保護素子電極22、基板接続電極42及びヒューズ素子電極32は、一体に形成された導電膜15からなる。

(もっと読む)

半導体素子及びその製造方法

【課題】平坦化工程またはエッチング工程でのパターン依存性に起因した工程不良を改善する効果に優れたダミーパターンを含む半導体素子及びその製造方法を提供する。

【解決手段】基板に形成されたデバイスパターンと、前記デバイスパターンの一側に互いに異なる大きさの垂直断面積を有して複数個形成されたダミーパターンとを含んで半導体素子を構成する。

(もっと読む)

半導体装置

【課題】 内部回路素子のESD破壊を防止するために、できる限り多くの割合の静電気パルスをオフトランジスタに引き込みつつ内部回路素子には伝播させない、あるいは早く大きな静電気パルスを遅く小さな信号に変化させてから伝えるようにすることができる半導体装置を得る。

【解決手段】 外部接続端子と内部回路領域との間にESD保護素子を有する半導体装置において、外部接続端子からESD保護素子に至る間の配線の抵抗値が、ESD保護素子から内部素子に至る間の配線の抵抗値よりも小さくなるように、外部接続端子からESD保護素子に至る間の配線を複数層のメタル配線により形成し、ESD保護素子から前記内部素子に至る間の配線は、外部接続端子からESD保護素子に至る間の配線に用いられた複数層の配線数と等しいあるいはより少ない層数のメタル配線により形成した。

(もっと読む)

気相成長を介して連続的な銅薄膜を形成する方法

【課題】多層基材を調製するための方法を提供する。

【解決手段】本方法は、バリア領域と銅領域を含む第1層を提供する工程と、該第1層上に銅を含む第2層を堆積する堆積工程とを含み、該堆積工程が、前記バリア領域上に約20Å〜約2,000Åの第1の厚さと、前記第1層の前記銅領域上に約0Å〜約1,000Åの第2の厚さとを含む第2層を提供し、該第1の厚さが該第2の厚さよりも大きい、第1層と第2層を含む多層基材を提供する。

(もっと読む)

基板の製造方法、液晶表示装置、液晶表示装置の製造方法、及び電子機器

【課題】ゲート配線部及びソース配線部の配線厚みはスイッチング素子部の性能劣化が生じない範囲内でしか厚くすることができない。よって、配線部の電気抵抗値を十分に小さくすることができないため、液晶表示装置の消費電力が大きいという課題がある。

【解決手段】スイッチング素子部30に形成されたゲート電極部41の電極厚みd3に比べ、Al膜14で厚膜化されたゲート配線部40の配線厚みd4が厚い。また、ソース電極部43及びドレイン電極部44の電極厚みd5に比べ、Al膜17で厚膜化されたソース配線部42の配線厚みd6が厚い。配線厚みd4,d6が厚いことにより、ゲート配線部40及びソース配線部42の断面面積が大きくなる。このことから、ゲート配線部40及びソース配線部42の電気抵抗値を小さくすることができる。よって、液晶表示装置100の低消費電力化ができる。

(もっと読む)

半導体装置及びその製造方法並びに半導体製造装置

【課題】プログラムされた情報のセキリュティが高く、半導体チップ毎に異なる情報をプログラムすることを簡単に可能とすること。

【解決手段】本発明は、半導体ウエハ内に配列された複数の半導体チップとなるべき領域12内にそれぞれ設けられたOTP−ROMセル配列21に対応するプログラムドット配列を有するプログラムヘッド80を、複数の半導体チップとなるべき領域12のうち1つの領域内のOTP−ROMセル配列21に合わせる工程と、プログラムヘッド80を用いOTP−ROMセル配列21を、複数の半導体チップとなるべき領域12ごとに異なるパターンでプログラムする工程と、を有することを特徴とする半導体装置の製造方法である。

(もっと読む)

融合金属層を使用しているオン抵抗の低い電力用FET

【課題】追加金属層を使用してFETのオン抵抗を下げるための高電力用電界効果トランジスタ(FET)を提供する。

【解決手段】或る実施形態では、高電力用FETの上に載っている比較的薄いが幅の広いバス条片が形成され、ソース及びドレインの幅の狭い金属条片に電流を導電している。不動態化層は、FETの表面を覆って形成され、不動態化層は、エッチングされてバス条片の上面全体の殆どを露出させる。銅のシード層が、ウェーハの表面を覆って形成され、更にマスクが形成されて、バス条片上のシード層のみが露出される。次に、バス条片上のシード層に、銅又は金電気メッキが施されて、非常に厚い金属層が堆積され、これが下層の金属の層と効果的に融合して、オン抵抗を低下させる。メッキ金属は、その厚さと幅の広いライン/空間のために、不動態化を施す必要は無い。露出したバス条片を覆って厚い金属を堆積するのに、他の技法を使用することもできる。

(もっと読む)

高周波回路装置、及びレーダ装置

【課題】 十分な接合強度が得られるように超音波振動の出力レベルを設定して超音波接

合を実施した場合であっても、半導体チップに形成された多層配線部の導体部分の断線を

防止することができ、また、製造工程における部品の管理コストの削減や製造部品の歩留

まりを改善することができる高周波回路装置を提供すること。

【解決手段】 高周波回路が形成されたMMICチップ2と、MMICチップ2の一方の

面に有機材料を用いて形成された多層配線部13と、多層配線部13の最表層面のバンプ

形成部4に形成されたバンプ6とを備え、超音波振動を与えて基板20と接合する場合に

、バンプ6とバンプ形成部4との接合部分の変形を抑える補強手段(補強用導体層5d)

が、多層配線部13に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】有機絶縁膜にコンタクトホールを形成して導電層と電極層とを接続させる半導体装置において、有機絶縁膜に起因する品質または性能の低下が生じにくい半導体装置を得る。

【解決手段】導電層2,5と、導電層2,5の上に設けられる有機絶縁膜20と、有機絶縁膜20の上に設けられる第1の電極層21と、導電層2,5上の有機絶縁膜20及び第1の電極層21を貫通して形成されるコンタクトホール23,24と、第1の電極層21の上に設けられ、かつコンタクトホール23,24を通り、導電層2,5と接続するように設けられる第2の電極層22とを備えることを特徴としている。

(もっと読む)

41 - 60 / 89

[ Back to top ]