Fターム[5F033QQ01]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971)

Fターム[5F033QQ01]の下位に属するFターム

反射防止に関するもの (535)

Fターム[5F033QQ01]に分類される特許

421 - 436 / 436

半導体装置の製造方法

【課題】パターン寸法のバラツキの少ない、配線容量の低減されたデュアルダマシン配線を、高い歩留まりで形成可能な半導体装置の製造方法を提供する。

【解決手段】基板20上に、有機系絶縁膜4を形成する工程と、有機系絶縁膜上に、無機材料を含む第1および第2のハードマスク5,6を形成する工程と、第2のハードマスクに凹部を形成する工程と、凹部が形成された第2のハードマスク上に、下層膜12、中間層13およびレジスト膜14を順次形成する工程と、レジスト膜をパターン露光する工程とを具備する方法である。前記下層膜は、前記第2のハードマスク上に第1の有機膜9を形成し、第1の有機膜を、スラリーを用いて化学的機械的に研磨して第2のハードマスクの表面を露出し、凹部に前記第1の有機膜を選択的に残置し、第2のハードマスクおよび第1の有機膜上に、第2の有機膜11を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 層間絶縁膜に低誘電率絶縁膜を用いた半導体作製の時、ハードマスクを用いて微細加工を行う製造方法を提供する。

【解決手段】 半導体に低誘電率絶縁膜13を適用して低誘電率絶縁膜13とその下層のエッチングストッパー膜12を加工する時、まずレジスト15aをマスクとしたハードマスク膜14のエッチングを行い、続いてレジスト15aをH2とHeの混合ガスで200℃より高い高温、1Torr付近の圧力の条件でアッシングを行う。このようにすればレジスト除去においてハードマスク膜14aにダメージを与えることなく続く低誘電率絶縁膜13のエッチングにおいてファセットの少ないハードマスクによる微細加工が可能となる。

(もっと読む)

半導体装置の製造方法

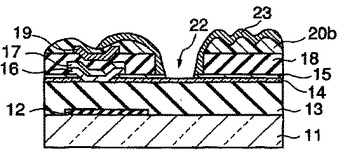

【課題】半導体装置の製造方法において、ネガレジスト層及び配線層のパターニング工程における信頼性の向上を図る。

【解決手段】 半導体基板10の裏面に開口部10wを形成した後、それらの上に配線層18及び第3のレジスト層19を形成する。次に、開口部10wの底部のダイシングラインDLの上方にマスク20を配置する。次に、開口部10wの側壁から当該底部に反射する光がマスク20に対応する第3のレジスト層19を固着させない光エネルギーを以って、第3のレジスト層19を露光する。次に、現像によりマスク20に対応する第3のレジスト層19を除去する。次に、第3のレジスト層19の全面を再び露光する。この第3のレジスト層19をマスクとして配線層18のエッチングを行う。最後に、ダイシングラインDLに沿って、半導体基板10を複数の半導体チップにダイシングする。

(もっと読む)

半導体装置の製造方法,半導体装置、エッチング条件の設定方法、導電膜除去条件の設定方法、及びレチクル

【課題】 導電膜が正常にパターニングされて配線が形成されていることを、少ない労力で確認することができるようにする。

【解決手段】 層間絶縁膜8上に導電膜を形成する工程と、前記導電膜をパターニングすることにより、チップ領域1aに配線10a〜10cを形成すると共に、スクライブライン1b上に、複数のダミー配線31〜33を互いに平行に形成する工程と、複数のダミー配線31〜33相互間の抵抗値を測定する工程とを具備する。最外側に位置するダミー配線31,33それぞれに接続するパッド34,35を形成し、このパッド34,35に抵抗計の端子を接触させてもよい。

(もっと読む)

導線近傍にスキャッタリング・バーを配置させてなる半導体デバイス

【課題】

疎密のパターンを備える半導体デバイス100のリソグラフィー技術を改善する方法を提供する。

【解決手段】

スキャッタリング・バー108aおよび108bを孤立した導線106bの両側に配置することによりリソグラフィーの結果を改善する半導体デバイス100の製造方法である。このスキャッタリング・バー108aおよび108bは、半導体デバイスパターニング時における孤立した導線106bの焦点深度を向上させるに十分な幅を有し、かつ、該導線106bの焦点深度を向上させるに十分な距離だけ該孤立した導線106bから離間させて配置される。半導体デバイス100の製造が終了した後にも、このスキャッタリング・バー108aおよび108bは残したままとする。

(もっと読む)

エッチング条件の設定方法、半導体装置の製造方法、及び半導体装置

【課題】 少ない労力でビアホール等を形成するときのエッチング条件が適切か否かを確認できるようにする。

【解決手段】 基準部、該基準部より低地である低地部、及び前記基準部より高地である高地部を有する半導体基板1上に、導電膜2及び層間絶縁膜3を形成し、層間絶縁膜3の表面を平坦化する。層間絶縁膜3をエッチングすることにより、低地部の上方に位置する第1及び第2の接続孔3a、前記基準部の上方に位置する第3の接続孔3b、及び高地部の上方に位置する第4の接続孔3cを同時に形成する。第1〜第4の接続孔3a〜3cそれぞれに、第1〜第4の導電体4a〜4cを埋め込む。層間絶縁膜3上に、第1の導電体3a、第3の導電体4b及び第4の導電体4cを互いに接続する上部電極5bを形成し、上部電極5bと、第1の導電体3aとの間の抵抗を測定する。

(もっと読む)

半導体パターン形成方法

【課題】 半導体パターン形成方法を提供する。

【解決手段】 この方法は無機ハードマスク膜、有機マスク膜、反射防止膜及びシリコン含有フォトレジスト膜が積層された多層のマスク層を形成し、O2プラズマで前記反射防止膜及び有機マスク膜を乾式エッチングしてパターンを形成することによって無機ハードマスク膜の損傷を防止することができる。

(もっと読む)

金属エアブリッジ

エアブリッジ(10)を形成するリソグラフィック方法は、一連の下端レジスト層(2)、シールド層(3)、及び上端レジスト層(4)を設けるステップと、ブリッジスパンの領域で上端レジスト層(4)を除去した後にシールド層(3)を除去するステップと、ブリッジのピラーの領域で下端レジスト層(2)を除去するステップと、一連の層の上に金属層(8)を形成するステップと、シールド層部分(3)及び金属コーティング部分(9)と共にレジスト層(2、4)を除去して、エアブリッジを形成するステップとを備える。 (もっと読む)

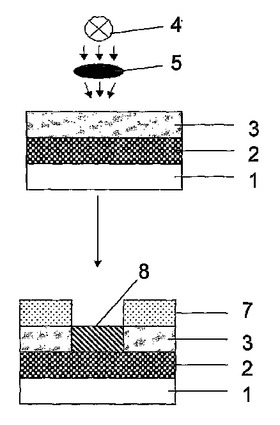

金属被着

レーザによりパターン化された基板上に金属を無電解メッキする方法。基板上に熱画像形成層および触媒層がともに被着される。レーザ・ビームで露光すると、熱画像形成層において十分なレベルの放射が熱に変換され、それによって、隣接する触媒層の露光領域が不活性になる。次いで、レーザによりパターン化された基板を反応溶液に暴露し、それによって、触媒層の非露光領域上で金属被膜の成長が開始される。  (もっと読む)

(もっと読む)

液晶表示装置の製造方法

アクティブマトリクス型液晶表示装置の薄膜トランジスタにおける下地電極上の絶縁膜上にフォトエンボッシング材料を用いて凹凸を有する有機膜を形成し、この有機膜にドライエッチングを施して有機膜の膜厚を減少させてコンタクトホール形成領域の絶縁膜を露出させる。その後、露出した絶縁膜にドライエッチングを施してコンタクトホールを形成すると共に下地電極を露出させ、得られた構造上に反射電極を形成して、露出した下地電極と反射電極とを接続する。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

多層配線構造およびそれを用いた電子部品

【課題】小型化および低背化対応した多層構造の電子部品において、電子部品を構成する絶縁層の上下層に構成された配線部を電気的に接続する信頼性の高い電子部品を提供する。

【解決手段】第一の絶縁層1、第二の絶縁層2および第三の絶縁層3により構成される多層配線構造において、第一の絶縁層1上に設けられた第一の配線部と第二の絶縁層2上に設けられた第二の配線部との電気的な接続を、第二の絶縁層2に設けられた、一部に傾斜部4を有する貫通孔5に形成された導通配線部6により行なう。傾斜部4は、凸部15の上面に囲われる構成となる。

【効果】傾斜部4およびそれに繋がる第二の絶縁層2上に設けられらた導通配線部6が、凸部15の上面に保護されることで、信頼性の高い配線形成ができる。。また、信頼性の高い小型化および低背化に対応した電子部品を提供することが可能となる。

(もっと読む)

配線構造およびその製造方法

【課題】感光性絶縁膜を用いたダマシン配線法により、微細で信頼性の高い多層配線構造を形成する。

【解決手段】感光性ポリシラザンを主成分とした感光性絶縁膜で第1ビアホール6を有するビアホール用絶縁膜7を形成し、全面にスピン塗布法で第2の感光性絶縁膜8を形成する。そして、フォトリソグラフィ法による露光/現像のみで上記第1ビアホール6の上部に配線溝9あるいは第2ビアホール10を形成する。そして、この配線溝9および第2ビアホール10に導電体材料を埋め込んでデュアルダマシン配線を形成する。ここで、感光性絶縁膜の下層に反射防止機能を有しそのまま層間絶縁膜として使用できる絶縁膜を形成する。

(もっと読む)

絶縁層及び接続孔の形成方法、配線構造及びその形成方法

【課題】 絶縁層及びヴィア形成において、形成された絶縁層の表面が非常に平滑となり、薄膜素子等を信頼性及び歩留り良く、高い自由度を以って形成でき、さらには微小なヴィア形成が可能である絶縁層及びヴィア(接続孔)の形成方法、及びそれを用いた多層配線基板並びにモジュール基板等の配線構造及びその形成方法を提供する。

【解決手段】 台座20を介してマスク基板21を配置し、この基板21とコア基板1との間に感光性エポキシ樹脂などの感光性絶縁材料3Aを介在させ、これをパターン露光して現像してヴィアホール7を形成する。この現像により、微小なヴィアホール7を形成できると同時に、マスク基板21のコア基板対向面21aによって絶縁材料(従って、絶縁層3)を平坦かつ滑らかな表面に、しかも常に設定された厚みに形成することができる。

(もっと読む)

配線構造及び配線形成方法

【課題】 電気的特性のみならず耐環境性にも優れた配線を実現し、ひいては当該配線を内装した半導体装置や配線基板等の信頼性の向上に寄与することを目的とする。

【解決手段】 絶縁層11,13に形成されたビア・ホールを介して下層の導体層12に電気的に導通するように絶縁層13と下層の導体層12とを覆って形成された金属薄膜14上に形成された配線層17の表面を、耐環境性に優れた材料からなる被覆層18で覆うように構成する。この被覆層18を構成する耐環境性に優れた材料としては、好適には、ニッケル/金、ニッケル/パラジウム、又はニッケル/パラジウム/金が用いられる。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

421 - 436 / 436

[ Back to top ]