Fターム[5F033QQ78]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱窒化 (63)

Fターム[5F033QQ78]に分類される特許

21 - 40 / 63

半導体装置及びその製造方法、並びに表示装置

【課題】高融点バリアメタル層を形成すること無く、Si膜又はSiを主成分とする膜と良好なコンタクト特性を実現するAl合金膜を提供する。

【解決手段】半導体デバイス(TFT)は、チャネル部11を形成する様にSi半導体膜7上に配設された被酸化のオーミック低抵抗Si膜8と、オーミック低抵抗Si膜8と直接に接続し、且つ、接続界面近傍に、少なくともNi原子、N原子及びO原子を含むアルミニウム合金膜から成る、ソース電極9及びドレイン電極10とを有する。

(もっと読む)

半導体装置

【課題】無線通信機能を有する半導体装置に振幅の大きい信号が供給された場合においても正常に動作し、且つ信頼性の高い半導体装置を提供する。

【解決手段】半導体装置は、交流電圧を生成するアンテナ101と、交流電圧を整流し、内部電圧Vinを生成する整流回路102と、第1の保護回路107と、第2の保護回路108と、を有する。第1の保護回路107は、第1のダイオード201と、第2のダイオード202と、を有し、第2の保護回路は、容量素子203と、トランジスタ204と、を有する。第1の保護回路は、アンテナ101で生成される交流電圧の絶対値がある値よりも大きい場合に、その余剰分をカットし、第2の保護回路108は、整流回路102で生成された内部電圧Vinが大きい場合に機能し、共振周波数をずらすことにより、半導体装置に入力される信号を減少させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】金属配線部から、金属が層間絶縁膜に拡散することを抑制するためのシリコン窒化膜等から窒素や水素が拡散することによる影響を軽減した信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上に形成された半導体素子部100と、半導体素子部100の上部に形成された銅配線225と、半導体素子部100と銅配線225とを電気的に接続するプラグ電極216と、このプラグ電極216が酸化しないようにするシリコン酸化膜223と、半導体素子部100の上部に形成されたアモルファスシリコン膜217と、アモルファスシリコン膜217の上部に形成されたCu拡散防止膜218と、を有した半導体装置1とする。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】シリコン基板1上に強誘電体キャパシタ37を形成する際、下部電極膜25の上に、アモルファス又は微結晶の酸化導電膜26を形成する。酸化導電膜26を熱処理により結晶化した後、強誘電体膜27の初期層27Aの形成時に酸化導電膜26を還元することにより、結晶粒が小さく且つ配向が整った第2の導電膜26Aを形成する。強誘電体膜27は、MOCVD法により形成し、その初期層27Aは第2の導電膜26Aの結晶配向に倣って成長する。これにより、強誘電体膜27の表面モフォロジが良好になる。

(もっと読む)

強誘電体メモリ装置の製造方法

【課題】コンタクトプラグ上に直接形成される下地層の結晶配向性を良好にし、さらにこの下地層の平坦性をも良好にすることで、下部電極や強誘電体膜の結晶配向性の改善を図った強誘電体メモリ装置の製造方法を提供する。

【解決手段】基板の上方に導電性の下地層を形成する工程と、下地層の上方に第1電極と強誘電体膜と第2電極とを積層する工程と、を含む強誘電体メモリ装置の製造方法である。下地層の形成工程は、プラグ20を含む層間絶縁膜26上に、自己配向性を有する導電材料からなる導電層411を形成する工程と、導電層411を窒素雰囲気中で熱処理し、窒化導電層412とする工程と、窒化導電層412を、シリコン酸化膜研磨用のスラリーを用いたCMP法によって低研磨速度で平坦化処理し、プラグ20を含む層間絶縁膜26上を覆った状態の平坦化窒化チタン層41とする工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの開口が容易であり、歩留まりが改善され、キャパシタ特性が向上した強誘電体メモリ等の半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に層間絶縁膜6を形成する工程と、層間絶縁膜6を貫通し半導体基板表面を露出する第1のホール及び第2のホールを形成する工程と、第1のホール及び第2のホールにそれぞれ導電膜を埋め込んで第1のプラグ10及び第2のプラグ10を形成する工程と、層間絶縁膜6上に第1のプラグ10と接続し、順に積層された導電性バリア膜、下部電極、誘電体膜、及び上部電極を有するキャパシタCを形成する工程と、キャパシタC、層間絶縁膜6、及び第2のプラグ10を覆うように少なくとも1つのAlON層を有する水素バリア膜20を形成する工程と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】コンタクトプラグ材料の基板への拡散を抑制する半導体装置及び半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、半導体基板200と導通するコンタクトプラグとなるCu膜260と、Cu膜260の少なくとも底面側に、半導体基板200と接触して配置された柱状結晶構造をもつTiN膜242と、Cu膜260の少なくとも底面側に、TiN膜242と接触して配置された、TiNのアモルファス膜244と、Cu膜260の底面側と側面側に、少なくとも一部がアモルファス膜244とCu膜260とに接触して配置された、TiN膜242材と同じ材料で柱状結晶構造をもつTiN膜246と、Cu膜260の側面側に配置されたSiO2膜220と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜に開口された接続孔の内部に導電性材料を埋め込む接続部において、接続孔の底部に存在するシリサイド層の表面の自然酸化膜を除去することのできる技術を提供する。

【解決手段】層間絶縁膜(第1及び第2絶縁膜19a,19b)に接続孔20を開口して、接続孔20の底部にニッケルシリサイド層18の表面を露出させた後、半導体ウエハの主面上にHFガス及びNH3ガスを含む還元ガスを供給し、還元反応により生成物を形成してニッケルシリサイド層18の表面の自然酸化膜を除去する。このときのHFガスとNH3ガスとの流量比(HFガス流量/NH3ガス流量)は1より大きく5以下とする。また半導体ウエハの温度を30℃以下とすることが好ましい。その後、半導体ウエハに150から400℃の加熱処理を施すことにより、半導体ウエハの主面上に残留する生成物を除去し、続いてバリアメタル膜21を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】内部に貫通電極を容易に形成することができ、製造歩留を向上させることのできる半導体装置を提供する。

【解決手段】半導体シリコン層上に、導電性ポリシリコンから構成される第1コンタクトパッドを有する第1絶縁層、第2コンタクトパッドを有する第2絶縁層を形成する。この後、貫通電極用のビアホールを、少なくとも半導体シリコン層および第1コンタクトパッドを貫通して第2コンタクトパッドに到達するまで形成する。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタを備えた半導体装置の歩留まりを改善することが可能な半導体装置の製造方法を提供すること。

【解決手段】シリコン基板20の上方に第1層間絶縁膜31を形成する工程と、第1層間絶縁膜31の上に、下部電極41a、強誘電体材料よりなるキャパシタ誘電体膜42a、及び導電性酸化物よりなる上部電極43aをこの順に積層してなるキャパシタQを形成する工程と、キャパシタQを覆う第2層間絶縁膜54を形成する工程と、上部電極43aの上の第2層間絶縁膜54に、該上部電極43aが露出するホール54aを形成する工程と、ホール54a内に、上部電極43aと接続された導電性窒化物よりなる単層のグルー膜58をスパッタ法で形成する工程と、グルー膜58をアニールする工程と、ホール54a内のグルー膜58上に導電性プラグ59aを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

単一チャンバーで半導体素子を製造する装置及び方法

【課題】単一のチャンバーで多様な工程を行うことができる半導体製造装置を提供する。

【解決手段】1つ以上のパターンを有する半導体基板に対して、互いに異なる多数の工程が行われる工程チャンバー600、各工程を行うための工程ガスを工程チャンバーの内部に独立して提供されるガス供給部710、ガス供給部と連結され工程チャンバーの上部に配置される多数の上部電極720及び上部電極と一対一で対応するように工程チャンバーの下部に配置され上面に前記基板が搭載される多数の下部電極730及び上部電極に電源を供給する第1電源及び下部電極に電源を供給する第2電源を具備する電源供給部740を含む。このような構成を採用したことにより、真空断絶なしに互いに異なる工程を行うことにより工程欠陥を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ビア抵抗の上昇を抑制できる構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板100上のビアホール105bを有する絶縁膜105と、ビアホール105bの底部及び壁部に沿うように形成されたIVa族、Va族又はVIa族元素の金属窒化膜106と、金属窒化膜106の上に、ビアホール105bの底部及び壁部に沿うように形成されたTa膜107と、Ta膜107の上に、ビアホール105bを充填するように形成された導電膜よりなるビア109bとを備える。ビアホール105bの底部における金属窒化膜106の膜厚は、4nm以上であって且つ8nm未満である。

(もっと読む)

半導体装置の製造方法

【課題】反射防止膜としてTiN膜を用いる場合において、アッシング工程にてTiN膜がAl合金配線から剥離するのを抑制できるようにする。

【解決手段】シリコン基板上に形成されるAl合金配線層の反射防止膜としてのTiN膜13f、16fの結晶粒界に充填物質13g、16gを充填する。このようにすれば、Al−Cu膜13c、16cへの酸素(O2)ラジカルの進入を防ぐことが可能となる。従って、酸素(O2)ラジカルとAl−Cu膜13cとが反応してAlxOyが形成されることが防止され、ポリマー除去時にAlxOyがフッ素ラジカルによって還元され、反射防止膜13f、16fがAl−Cu膜13cから剥離することもない。

(もっと読む)

半導体装置及び当該半導体装置の作製方法

【課題】集積回路部上にアンテナを作り込んで設ける場合であっても、接続不良やコンタクト抵抗の増加を抑制することを課題とする。

【解決手段】基板上に第1の導電膜を有する集積回路部を形成し、集積回路部上に絶縁膜を形成し、絶縁膜上にアンテナとして機能する第2の導電膜を選択的に形成し、絶縁膜及び第2の導電膜に開口部を形成して第1の導電膜を露出させ、メッキ処理により開口部及び第2の導電膜の上面に第3の導電膜を形成することにより、第1の導電膜及び第2の導電膜とを電気的に接続する。

(もっと読む)

半導体装置とその製造方法

【課題】歩留まりを向上させることが可能な半導体装置とその製造方法を提供すること。

【解決手段】第1ホールの21a内面と、該第1ホール21aに露出する金属シリサイドパターン(導電パターン)17aの上面に、高融点金属よりなる第1バリアメタル膜22aを形成する工程と、第1バリアメタル膜22aの上に、高融点金属の窒化物よりなる第2バリアメタル膜22bを形成する工程と、第2バリアメタル膜22bをアニールする工程と、アニールの後に、第2バリアメタル膜22bの上にプラグ用導電膜23を形成する工程と、プラグ用導電膜23、及び第1、第2バリアメタル膜22a、22bを第1ホール21a内に第1導電性プラグ24として残す工程とを有する半導体装置の製造方法による。

(もっと読む)

窒化アルミニウムを使用することによる微細構造デバイス内の銅系メタライゼーション構造の信頼性向上

自己制限プロセスシーケンスによって窒化アルミニウム層(106)を形成することにより、銅系メタライゼーション層の界面特性を大幅に改善できる一方で、層スタックの全体的な誘電率を低いレベルに保つことができる。  (もっと読む)

(もっと読む)

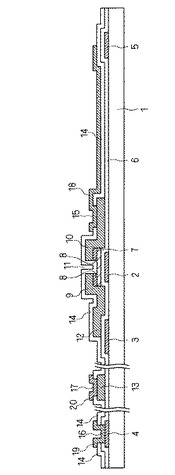

薄膜トランジスタ基板、および表示デバイス

【課題】バリアメタル層を省略しても優れたTFT特性を発揮し得、ソース−ドレイン配線をTFTの半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】薄膜トランジスタの半導体層33と、ソース−ドレイン電極28,29とを有する薄膜トランジスタ基板において、ソース−ドレイン電極28,29は、窒素を含有する窒素含有層、または窒素及び酸素を含有する酸素窒素含有層28a、29aと、純Cu又はCu合金の薄膜28b、29bとからなっている。窒素含有層を構成する窒素の一部若しくは全部、または、酸素窒素含有層を構成する窒素または酸素の一部若しくは全部は、薄膜トランジスタの半導体層33のSiと結合している。また、純CuまたはCu合金の薄膜28b、29bは、窒素含有層または酸素窒素含有層28a、29aを介して薄膜トランジスタの半導体層33と接続している。

(もっと読む)

配線パターンの形成方法及び形成装置、並びにデバイスの製造方法

【課題】機能液の液滴で基板の表面に所望の配線パターンを形成できる配線パターンの形成方法を提供する。

【解決手段】基板の表面の第1方向に延びる第1ラインパターンと、基板の表面において第1方向と異なる第2方向に延び、第1ラインパターンの一端と接続される一端を有し、第1ラインパターンよりも短い第2ラインパターンとを含む配線パターンの形成方法は、基板の表面に、配線パターンの設計データに応じた配線パターン形成領域を設定するとともに、配線パターン形成領域を、液滴の大きさに応じた複数のピクセルでマトリクス状に区画する工程と、複数のピクセルのうち、所定のピクセルに液滴を吐出して、基板の表面に配線パターンを形成する工程と、を含む。配線パターン形成領域を区画する複数のピクセルのうち、第2ラインパターンに対応するピクセルの少なくとも1つは、液滴が吐出されないピクセルに設定される。

(もっと読む)

半導体装置の製造方法

【課題】W層で形成されたビット線等の配線の上に、シリコン酸化膜による層間絶縁膜を生成する際、W層の配線の上に酸化防止膜として窒化シリコン膜を形成する場合、配線抵抗の増加の原因となるWN層の形成を抑制することにより、従来例に比較して歩留まりを向上させる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に絶縁膜を形成する絶縁膜形成工程と、第1の絶縁膜の上にタングステン膜を有する配線パターンを形成する配線パターン形成工程と、ジクロルシランとプラズマにてラジカル化されたアンモニアとを用いたALD法にて堆積される窒化シリコン膜により、前記配線パターンの露出部を被覆する配線パターン被覆工程と、層間絶縁膜を形成する層間絶縁膜形成工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を確保しながら、高い信頼性を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】PZT膜24上にスパッタ法により厚さが50nmのIrOX膜25を形成する。xの値は、2未満とする。即ち、不飽和のイリジウム酸化膜を形成する。次に、RTAを行うことにより、PZT膜24を完全に結晶化させる。その後、IrOX膜25上にスパッタ法により厚さが50nm〜100nmのIrOY膜26を形成する。IrOYの組成はIrOXの組成よりもIrO2の化学量論組成に近い組成(X<Y≦2)とする。これは、このような組成とすることにより、水素に対する触媒作用が抑えられ、PZT膜24が水素ラジカルにより還元されるという問題が抑制され、強誘電体キャパシタの水素耐性が向上するからである。次に、IrOY膜26上にスパッタ法により厚さが20nm程度でアモルファス状態のSrXRuYO3膜27を形成する。

(もっと読む)

21 - 40 / 63

[ Back to top ]