Fターム[5F033TT08]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038) | 電極、配線の側壁 (1,106)

Fターム[5F033TT08]に分類される特許

1,021 - 1,040 / 1,106

半導体集積回路装置の製造方法

【課題】半導体集積回路装置の高速化を図り、また、エレクトロマイグレーションやストレスマイグレーションの発生を抑え、配線寿命を長くする技術を提供する。

【解決手段】半導体基板1上に形成された酸化シリコン膜23および窒化シリコン膜22中の配線溝内を含む酸化シリコン膜23上にバリア層26aおよび銅膜26bを順次形成後、前記配線溝外部のバリア層26aおよび銅膜26bを除去することによって配線26を形成し、配線26上にタングステンを選択成長もしくは優先成長させることにより、配線26上にタングステン膜26cを形成する。

(もっと読む)

半導体装置の製造方法

【課題】 MOSトランジスタとバイポーラトランジスタとで構成されるアナログ/デジタル混載半導体装置の製造コストを低減する。

【解決手段】 n型エミッタ電極23bを形成するためのn型不純物のイオン注入と、nチャネル型MOSトランジスタのソース、ドレインを形成するためのn型不純物のイオン注入とを同時に行い、p型エミッタ電極23cを形成するためのp型不純物のイオン注入と、pチャネル型MOSトランジスタのソース、ドレインを形成するためのp型不純物のイオン注入とを同時に行うことにより、イオン注入工程およびフォトマスクの枚数を減らす。

(もっと読む)

半導体装置の製造方法

【課題】 エッチング工程で生成される反応生成物による配線信頼性の低下を防ぐ半導体装置の製造方法を提供する。

【解決手段】 配線と、配線に接続されるプラグとを有する半導体装置の製造方法であって、配線上に絶縁膜を形成する工程と、プラグを形成するためにドライエッチングにより絶縁膜に開口を形成する工程と、水素単体ガスまたは窒素を含むガスによるプラズマ放電により上記ドライエッチングにより生じた反応生成物を除去する工程とを有するものである。

(もっと読む)

半導体装置及び半導体装置のパターン設計方法

【課題】半導体チップ全体でのパターン占有率を一定にすることにより、プロセス制御性を向上させる。

【解決手段】 導体チップ10内の論理演算に寄与する第1領域11に固定サイズの第1ダミーパターンを形成する。第1ダミーパターンは、水平方向及び垂直方向に隣接する信号配線から0.5μm以上離間して形成する。半導体チップ10全体でのパターン占有率が製品毎及び同一製品内の配線層毎で一定値になるように、半導体チップ10内の論理演算に寄与しない第2領域12に第2ダミーパターンを形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 良質でかつ良好な形状のサイドウォールを備えた半導体装置を形成する。

【解決手段】 ゲート電極側壁のサイドウォールを炭素含有シリコン窒化酸化膜を用いて形成する。炭素含有シリコン窒化酸化膜は、BTBASと酸素を原料に用い、BTBAS流量/酸素流量比を適当に設定すると共に、例えば約530℃等の低成膜温度のCVD法で成膜することができる。炭素含有シリコン窒化酸化膜を用いてサイドウォールを形成することで、窒素原子や炭素原子の寄与により、HF耐性向上やフリンジ容量低減を図れる。また、低温条件で成膜することにより、半導体基板内に導入されている不純物の不要な拡散が抑えられるようになる。これにより、トランジスタ特性を高めかつ安定化させ、半導体装置の高性能化、高品質化を図れるようになる。

(もっと読む)

パターン形成方法、電子デバイス製造方法、及び電子デバイス

【課題】高精度な微細パターンを安定的に形成できるようにする。

【解決手段】基板1上の被加工層4の表面に薄膜5を形成し、リソグラフィ工程(レジスト塗布、パターン露光、現像等)により薄膜5の表面に第1のパターン6を形成する。この第1のパターン6は被加工層4に最終的に形成すべき開口パターンにダミーパターンを付加した周期密集パターンであり、露光時にこれに最適な変形照明等の超解像技術を用いる。次に、第1のパターン6をマスクとして薄膜5をエッチングし、第1のパターン6を除去する。その後、薄膜5の表面にリソグラフィ工程により所望のパターンを包含する第2のパターン11を形成する。最後に、薄膜5と第2のパターン11とをマスクとして被加工層4をエッチングすることにより、被加工層4に所望のパターン16を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体措置で発生した熱を放熱しやすくすることによってESD耐圧に優れた半導体装置およびその製造方法を提供する。

【解決手段】 拡散層領域3に形成されたチャネル11の上には、ゲート絶縁膜7を介してゲート電極8が設けられている。また、ゲート電極8の側壁部には、サイドウォール9が形成されている。そして、ゲート電極8上とソース・ドレイン領域5上の一部とに、ゲート電極8およびサイドウォール9を被覆するようにしてシリサイドプロテクション膜10が形成されている。シリサイドプロテクション膜10が設けられていないソース・ドレイン領域の上には、シリサイドプロテクション膜10に隣接して金属シリサイド膜6が形成されている。ここで、シリサイドプロテクション膜10は、SiC膜およびSiOC膜の少なくとも一方からなるものとする。

(もっと読む)

半導体装置及びその製造方法

【課題】 層間絶縁膜の膜剥がれ及び周辺への銅の拡散を防止しつつ、層間絶縁膜のより一層の低誘電率化を図ることができる半導体装置及びその製造方法を提供するものである。

【解決手段】 絶縁性保護膜10で覆われた基板101を形成する工程と、絶縁性保護膜10上にプラズマCVD法により形成された絶縁膜で囲まれた第1の多層配線501を形成する工程と、第1の多層配線501を残して絶縁性保護膜10上の絶縁膜をすべて除去する工程と、絶縁膜を除去した後の空間に、塗布法により第1の塗布絶縁膜を充填する工程とを有する。

(もっと読む)

延伸スペーサを利用した半導体デバイスおよびその形成方法

【課題】延伸スペーサを利用した半導体デバイスおよびその形成方法を提供する。

【解決手段】半導体デバイスは、半導体基板110を覆うゲートと、ゲートの側壁上にある誘電体ライナー150とを含む。この半導体デバイスは、誘電体ライナー150に隣接して誘電体ライナー150を越えるように半導体基板110に沿って横向きに延伸された延伸スペーサ170を含む。半導体デバイスは、半導体基板110の上面の下方に位置し、ゲート下のチャネル領域145に隣接するソース/ドレインをさらに含む。ソース/ドレインは、誘電体ライナー150および延伸スペーサ170下で延伸される。半導体デバイスは、ソース/ドレインの一部上を覆い、半導体基板110に沿って横向きに延伸するシリサイド領域190をさらに含む。従って、延伸スペーサ170はソース/ドレインの一部上において誘電体ライナー150とシリサイド領域190との間に形成される。

(もっと読む)

半導体装置の製造方法

【課題】ターゲット等、光学的に位置検出するための大きな面積のパターン領域での表面平坦性を向上する。

【解決手段】ウェハのスクライブ領域SRに形成されるターゲットT2領域の下層に大面積ダミーパターンDLを形成する。また、製品領域PRおよびスクライブ領域SRの素子として機能するパターン(活性領域L1,L2,L3、ゲート電極17等)のパターン間スペースが広い領域に下層の小面積ダミーパターンと上層の小面積ダミーパターンDs2を配置する。このとき、上層の小面積ダミーパターンDs2は、下層の小面積ダミーパターンに対してハーフピッチシフトさせて形成する。

(もっと読む)

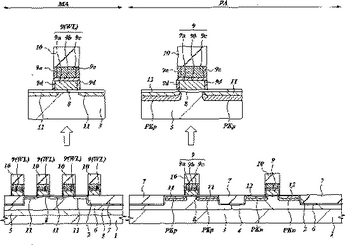

半導体集積回路装置およびその製造方法

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】光近接効果に起因するトランジスタのゲート長ばらつきを抑制しうる半導体装置を提供する。

【解決手段】ゲート電極5A〜5Fを同一形状であり、ゲート電極5A〜5Fの突き出し部は、素子分離領域を越えて基板コンタクト用の拡散領域上まで延びている。ゲート電極5BおよびP型拡散領域と1層目配線M1Hとはシェアードコンタクト9A1で接続され、ゲート電極5EおよびN型拡散領域7A6と1層目配線M1Iとはシェアードコンタクト9A2で接続される。これにより、ゲート電極5A〜5Fのうちコンタクトパッド部をMOSトランジスタの活性領域から離すことができる。その結果、ハンマヘッドによるゲート長太り及びゲートフレアリングによるゲート長太りの効果が抑制され、TrA〜TrFの仕上がりゲート長をほぼ一定値にすることが可能となる。

(もっと読む)

非対称パターンを形成するためのフォト工程の実行方法及びそれを用いた半導体装置の形成方法

【課題】非対称パターンを形成するためのフォト工程の実行方法及びそれを用いた半導体装置の形成方法を提供する。

【解決手段】準備した半導体基板の素子分離膜は複数の活性領域を孤立形成する。半導体基板全面上に平坦化層間絶縁膜及びフォトレジスト膜を順に形成する。フォトレジスト膜にフォトマスクによる半導体パターンを転写させその膜にフォトレジストパターンを形成する。それは、活性領域及び素子分離膜の上部位置の平坦化層間絶縁膜上の所定領域に配置される。フォトレジスト膜に他のフォトマスクを有する他の半導体パターンを引き続いて転写させてその膜に他のフォトレジストパターンを形成する。それは素子分離膜上部に位置した平坦化層間絶縁膜上の異なる所定の領域にそれぞれ配置される。フォトレジストパターン及び他のフォトレジストパターンをエッチングマスクとして用いて平坦化層間絶縁膜にエッチング工程を実行して半導体基板を露出する。

(もっと読む)

半導体装置およびその製造方法

【課題】 洗浄工程において、配線を形成する材料がピンホールを介して消失することを防止できる半導体装置およびその製造技術を提供する。

【解決手段】 酸化シリコン膜37に埋め込むように配線41を形成する。続いて、配線41上を含む酸化シリコン膜37上に炭窒化シリコン膜43を形成する。ここで、炭窒化シリコン膜43は、ピンホール43aが貫通しない程度の膜厚で形成する。次に、炭窒化シリコン膜43を加工して、酸化シリコン膜37上の炭窒化シリコン膜43の膜厚を配線41およびその近傍領域上に形成された炭窒化シリコン膜43の膜厚よりも薄くする。

(もっと読む)

絶縁膜の成膜方法及びその絶縁膜を備えた半導体装置

【課題】絶縁膜の成膜方法において、シリコン原子を堆積させる第1ステップと、シリコン原子を窒化する第2ステップとを有するALD法を用い、フラットバンド電圧及び界面準位の小さい好適な特性を有する薄い絶縁膜の成膜方法を提供する。

【解決手段】第1及び第2ステップでの成膜温度と圧力を同一とし、成膜温度を510℃以下の低温とし、圧力を70Pa以下、RFパワーを0.1KW以上とすることでフラットバンド電圧及び界面準位の小さい好適な特性の絶縁膜が得られる。これらの好適な絶縁膜を備えた半導体装置が得られる。

(もっと読む)

半導体装置の製造方法

【課題】測定対象の収縮等が生じやすい条件下でも高い精度で測長を行うことができる半導体装置の製造方法を提供する。

【解決手段】Si基板上にレジスト膜を形成した後、レジスト膜に半導体集積回路用の回路パターン、第1のL字型測長用パターン3a,3b及び十字型のアライメント用モニタパターン4a,4bを形成し、これらのパターンに基づいて、Si基板をパターニングする。その後、Si基板の上方に、ポリSi膜を形成し、ポリSi膜上にレジスト膜を形成する。レジスト膜に半導体集積回路用の回路パターン、第2のL字型測長用パターン13a,13b及び十字型のアライメント用モニタパターン15bを形成する。このとき、第2のL字型測長用パターンが平面視で第1のL字型測長用パターンを180度回転させた方向を向くようにする。そして、これらのパターンをマスクとして、ポリSi膜をパターニングすることにより、ゲート電極を形成する。

(もっと読む)

半導体装置、その製造方法及び製造装置

【課題】多層配線構造の層間絶縁膜を、析出異物の問題なく、また電気特性を損なうことなく、平坦性高く形成する。

【解決手段】不純物含有シリコン酸化膜を準常圧領域でCVD法により形成するCVD工程(ステップ1〜5)と、形成された不純物含有シリコン酸化膜をリフローするリフロー工程とを含み、前記CVD工程は、有機シリコン系ガスと不純物含有有機系ガスと酸化性ガスとを材料ガスとして、不純物を高濃度に含有したシリコン酸化膜を成膜する第一のCVD工程(ステップ2〜4)と、不純物含有有機系ガスを前記第一のCVD工程よりも低量に制御して、微量の不純物を含有したシリコン酸化膜を成膜する第二のCVD工程(ステップ5)とで構成される方法。

【効果】第一と第二のCVD工程で不純物濃度を制御することでリフロー性を向上させ、高濃度不純物に起因する吸湿、析出異物の問題を回避することができる。

(もっと読む)

半導体装置

【課題】

新たに見出した経時的配線不良率の知見に基づき、長期間の高信頼性を実現できる銅配線を有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、前記半導体基板に形成され、多電圧で駆動される回路を含む複数の回路領域と、前記半導体基板上方に形成された層間絶縁膜と、前記層間絶縁膜に埋め込んで形成された銅配線であって、同一層内で隣接する配線間の最小配線間隔が、印加される電圧差によって配線間に生じる電界が0.4MV/cm以下になるように選定されている銅配線と、前記銅配線の上面を覆って、層間絶縁膜上に形成された銅拡散防止膜と、を有する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】CMP法により研磨される絶縁膜の平坦性を向上する。

【解決手段】半導体基板1の主面上に形成されたMISFETQ1を覆う層間絶縁膜9の上層に配線10を形成するとともに、その配線10間の間隔が広い領域にダミー配線11を配置する。また、ダミー配線11はスクライブ領域にも配置される。さらに、ダミー配線11は、ボンディングパッドの周辺領域およびマーカの周辺領域には、配置されない。また、MISFETのゲート電極と同層にダミーゲート配線を設ける。また、浅溝素子分離領域にダミー領域を向ける。これらダミー部材を設けた後に、CMP法で絶縁膜を平坦化する。

(もっと読む)

半導体装置とその製造方法

【課題】 周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】 第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

1,021 - 1,040 / 1,106

[ Back to top ]