Fターム[5F033XX08]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 低抵抗化 (1,713)

Fターム[5F033XX08]の下位に属するFターム

コンタクト抵抗の低減 (898)

シート抵抗の低減 (573)

Fターム[5F033XX08]に分類される特許

161 - 180 / 242

半導体装置

【課題】信号ラインの直列抵抗成分を充分に下げると共に、高周波信号を伝送する場合であっても高周波抵抗を下げることができ、例えば大電力用MMICで採用しても電力利得をさらに上げることが可能な半導体装置を提供する。

【解決手段】所定の素子が形成された半導体基板上に、層間膜と上下2層配線構造の信号ラインを含むマイクロストリップライン線路300が形成される半導体装置であって、下層配線306上には、下層配線306を開口する複数のコンタクトホール310を有する層間膜が形成され、上層配線312は、コンタクトホール310の側面及び底面を含む全表面に形成される。

(もっと読む)

半導体製造装置、半導体装置の製造方法及び記憶媒体

【課題】絶縁膜の凹部に沿って成膜した銅及び添加金属例えばMnの合金層を利用してバリア膜と銅膜とを形成し、その後銅配線を埋め込むにあたって、銅膜中のMnの量を低減し、配線抵抗の上昇を抑えること。

【解決手段】ウエハキャリアに対してウエハの受け渡しをするローダモジュールに真空搬送モジュールをロードロック室を介して接続し、この真空搬送モジュールに、有機酸である蟻酸の蒸気をウエハに供給する蟻酸処理モジュールとCuを例えばCVDにより成膜するモジュールとを接続して半導体製造装置を構成し、前記合金層を形成し例えば続いてアニール処理が行われたウエハWをこの装置内に搬入して、蟻酸処理を行ってからCuの成膜を行うようにする。

(もっと読む)

半導体装置の製造方法

【課題】プラズマダメージの影響を抑止するシール層を用いて、ビア抵抗を増大させることなく信頼性不良を低減することを可能とする。

【解決手段】層間絶縁膜11に凹部(ビアホール13、配線溝14)を形成する工程と、前記凹部の内面にアルキル基を有するシラン系のガスをプリカーサとして用いたシール層15を形成する工程と、前記シール層15に対して電子線キュアもしくは紫外線キュアを行う工程と、前記凹部に導電体17を埋め込む工程とを備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ウェハ間や同一ウェハ内において、配線抵抗の増加や、コンタクト抵抗の増加等を抑制することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に第1絶縁膜と第2絶縁膜とを含む積層膜が形成された被処理基板を、エッチング装置内に配置し、前記第1絶縁膜と前記第2絶縁膜を同一エッチング装置内においてエッチングする工程を有し、

前記第1絶縁膜が窒素含有膜からなり、前記第2絶縁膜がSiOCH膜等からなり、前記工程において、前記第1絶縁膜のエッチングガスおよび前記第2絶縁膜のエッチングガスとしていずれも、CxFyで表されるフルオロカーボンを含むガスを用いることを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】LSIプロセスによる制約のない最上位配線層を提供することで長距離配線における信号遅延を低減可能な半導体集積回路装置の製造方法を提供する。

【解決手段】

半導体集積回路基板を提供する過程は、半導体集積回路用ベース基板11上に、半導体集積回路及び該半導体集積回路用の最上位配線層を含まない配線層12を形成する過程と、半導体集積回路用ベース基板の配線層上に、該配線層に接続される接続パッド13を形成する過程とからなる。配線基板を提供する過程は、配線基板用ベース基板1上に、半導体集積回路用の最上位配線層となる厚膜配線層3をメッキ形成する過程と、厚膜配線層上に、該厚膜配線層に接続される接合バンプ6を形成する過程とからなる。そして、半導体集積回路基板の接続パッドが形成される面と配線基板の接合バンプが形成される面とを対向させ接続パッド及び接合バンプを位置合わせして接合する。

(もっと読む)

半導体メモリ素子のビットライン形成方法

【課題】低抵抗タングステンを用いてコンタクトとビットライン金属配線を形成することにより、ビットラインの面抵抗値を減少させ、工程を簡素化してTATを改善させる方法を提供する。

【解決手段】層間絶縁膜101にコンタクトホールを形成し、バリアメタル102を形成後、全体構造上にCVD法によりタングステン膜を形成する。このときの核生成工程において、B2H6またはSiH4をドーピングし、タングステン膜のグレインサイズを増大させる。この後、CMPによりタングステン膜の表面粗さを緩和し、エッチングにより低抵抗タングステンからなるビットラインパターン103を形成する。

(もっと読む)

半導体装置およびそれを備える液晶表示装置

【課題】低い配線抵抗および高い歩留まりならびに低いコストを実現できる半導体装置およびそれを備える液晶表示装置を提供する。

【解決手段】半導体装置100は、ゲート電極5aおよびゲート配線5bと、ソース/ドレイン電極7aおよびソース/ドレイン配線7bと、画素電極線9とを備えている。接続孔10は、断面矩形状であり、ゲート絶縁膜4およびパッシベーション膜8を貫通しゲート配線5bおよびソース/ドレイン電極線7それぞれの端部を露出させるように、1個が設けられている。画素電極線9は、少なくとも接続孔10に沿って設けられ、その底面の一部はゲート配線5bに他の一部はソース/ドレイン電極線7にそれぞれ接している。

(もっと読む)

半導体装置の製造方法

【課題】合金層(シード層)中の自己形成バリア膜の生成に寄与しない余剰なMnを除去することで、配線抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】まず、基板11上に設けられた層間絶縁膜15に配線溝16を形成する。次に、配線溝16の内壁を覆う状態で、CuMnからなる合金層17を形成する。次いで、合金層17が設けられた状態の基板11の表面に、Cuに対してMnを選択的に溶解する洗浄液を供給し、自己形成バリア膜の形成に寄与しない合金層17中のMnを、洗浄液に溶解させて選択的に除去する。続いて、熱処理を行い、合金層17中のMnを層間絶縁膜12、15の構成成分と反応させて、合金層17と層間絶縁膜12、15の界面に、Cuの拡散防止性を有するMn化合物からなる自己形成バリア膜を形成する。続いて、自己形成バリア膜が設けられた配線溝16にCuを主成分とする導電層を埋め込む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線材とバリアメタル層の密着性を向上させる。

【解決手段】第1の基板温度で、表面に凹部が形成された層間絶縁膜中及びその表面の酸

化種を放出させ、その後、前記第1の基板温度より低い第2の基板温度で、前記層間絶縁

膜の少なくとも一部と接触するようにして、Ti及びNを含み、酸素(O)及び貴金属成分を除く全成分におけるTi含有量が50at%を超える層を形成する。次いで、前記層上にCu金属層を形成して半導体装置を製造する。

(もっと読む)

カーボンナノチューブを用いた半導体素子の層間配線およびその製造方法

【課題】カーボンナノチューブを用いた半導体素子の層間配線およびその製造方法を提供する。

【解決手段】下部電極と、前記下部電極と電気的に連結されるように設けられるカーボンナノチューブ成長用の触媒層と、前記触媒層表面から上方に成長する多数のカーボンナノチューブで構成され、上端部の個数密度が下端部の個数密度より高いカーボンナノチューブ束と、前記カーボンナノチューブ束を取り囲む層間絶縁層と、前記層間絶縁層上に前記カーボンナノチューブ束の上端部と電気的に連結されるように配置される上部電極と、を備えることを特徴とする、カーボンナノチューブを用いた半導体素子の層間配線およびその製造方法である。

(もっと読む)

半導体集積回路の配線構造及び配線形成方法

【課題】Cu拡散防止機能のバリア性を維持しつつ、より低抵抗の半導体集積回路の配線構造及び配線形成方法を提供する。

【解決手段】基板11上の層間絶縁膜12下層にコンタクト領域である拡散層13が形成されている。この拡散層13が露出する開孔14及び配線溝15が形成されており、主にCu配線部材16により配線材料が埋め込まれた構成となっている。図において、少なくとも層間絶縁膜12下層のコンタクト領域である拡散層13に接触するバリアメタル層BMTLが形成されている。バリアメタル層BMTLはTi/TiN積層や、TaN、WNその他様々考えられる。さらに、上記Cu配線部材16とバリアメタル層BMTLの間にAlを含む薄膜161が介在している。

(もっと読む)

集積回路及びこれを備えるアセンブリ

高周波数で用いるのに適しており、且つ、入力と出力を有する第1のキャパシタ及びグランド接続を備える集積回路であって、キャパシタは、該キャパシタの出力とグランド接続との間の抵抗を介してESD保護され、抵抗は、グランド接続のRF性能への実質的な影響を阻止するように充分に高い抵抗値を有する、集積回路。  (もっと読む)

(もっと読む)

半導体メモリ素子の製造方法

【課題】金属配線の速い電荷伝達を妨げる要因を除去し、また、金属配線の表面の損傷を防止し、半導体メモリ素子の高速動作を実現することができるNANDフラッシュメモリ素子等の半導体メモリ素子の製造方法を提供する。

【解決手段】半導体メモリ素子の製造方法は、基板30上にコンタクトプラグ40、42、43、及びコンタクトプラグ40、42、43を囲む第1の層間絶縁膜39と第2の層間絶縁膜41を形成するステップと、パターニングされたTi/TiN膜による拡散防止膜46及びタングステン膜による金属配線47を含み、コンタクトプラグ40、42、43の上に重なる金属配線構造Mを形成するステップと、金属配線47の表面を酸化させ、金属配線47の表面に保護膜49を形成するため、H2SO4、H2O2、脱イオン水及びHFを混合して得られた洗浄ケミカルを利用するステップとを含む。

(もっと読む)

デバイス、方法(MIMキャパシタおよびその製造方法)

【課題】MIMキャパシタ・デバイスおよびMIMキャパシタ・デバイスの製造方法を提供すること。

【解決手段】このデバイスは、1つまたは複数の導電層を含み、上面、下面および側壁を有する上プレートと、1つまたは複数の導電層を含み、上面、下面および側壁を有するスプレッダ・プレートと、1つまたは複数の誘電層を含み、上面、下面および側壁を有する誘電ブロックとを含み、誘電ブロックの上面は上プレートの下面と物理的に接触し、誘電ブロックの下面はスプレッダ・プレートの上面の上にあり、上プレートと誘電ブロックの側壁は本質的に共面である。

(もっと読む)

半導体装置、電気光学装置、電子機器及び半導体装置の製造方法

【課題】使用するアクティブマトリクス方式の表示器に使用される有機半導体装置においてゲート駆動信号を伝搬するゲート線(ゲート信号線)の抵抗値を下げることを可能とした半導体装置、電気光学置及び電子機器を提供する。

【解決手段】基板上(101)に形成された有機半導体トランジスタと、有機半導体トランジスタのソース又はドレイン電極(105)と接続されるデータ線(107)と、データ線と交差するように配置されて有機半導体トランジスタのゲート電極(110)に接続されるゲート線と、を備え、ゲート線は、ゲート電極(110a)、ゲート電極に信号を伝搬する第1のゲート線(102)、及びデータ線と層間絶縁層(109)を介して交差する第2のゲート線(110b)を含み、上記ゲート電極、上記第1及び第2のゲート線は互いに直列に接続され、第1のゲート線(102)の導電率がゲート電極(110a)及び第2のゲート線(110b)の導電率よりも高い、ことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を減少しつつ、2つの配線層間を電気的に接続すること。

【解決手段】2つの配線11C、11D間の下層部にて、数珠繋ぎ形状に形成されるとともに、2つの配線11C、11Dを電気的に接続するコンタクトプラグ9cを備える。2つの配線11C、11Dは、互いに離間して同一の層に形成されている。コンタクトプラグ9cは、配線4bに接続されるコンタクトプラグ9bと、ソース/ドレイン領域6に接続されるコンタクトプラグ9aと同時に形成される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置においてシリサイドの低抵抗化を阻害することなくゲート電極を狭幅化できるようにする半導体装置の製造方法を提供する。

【解決手段】シリコン半導体基板1の表面領域の全面にポリシリコン膜4を形成し、このポリシリコン膜4をパターニングして、フィールド酸化膜2におけるポリシリコン膜4'の線幅が素子形成領域におけるポリシリコン膜4の線幅よりも大きくなるようにする。次いで、MOSFETのゲート幅を規定する1層目のポリシリコン膜4,4'の上、及び、側壁SiN膜6の上にSiO2膜8を介して、ポリシリコン膜4,4'よりも幅広の2層目のポリシリコン膜を形成し、その2層目のポリシリコン膜をシリサイド化して、チタンシリサイド層12を形成する。

(もっと読む)

銅配線用洗浄剤

【課題】銅配線の腐食抑制効果(銅腐食抑制効果)が優れ、かつ接触抵抗に影響を及ぼさない銅配線用洗浄剤を提供することを目的とする。

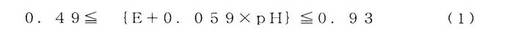

【解決手段】銅腐食抑制剤(RE)及び水(W)を含有してなり、25℃でのpHが3〜14であり、かつ式(1)を満たしてなることを特徴とする銅配線用洗浄剤を用いる。

【数1】

{式中、Eは25℃での酸化還元電位(V、vsSHE)、pHは25℃でのpHを表す。}

また、上記の銅配線用洗浄剤を半導体基板又は半導体素子に連続的又は断続的に供給して、銅配線を有する半導体基板又は半導体素子を洗浄することを特徴とする半導体基板又は半導体素子の洗浄方法を用いる。

なし

(もっと読む)

半導体装置の製造方法

【課題】ニッケルシリサイド層の電気的特性のばらつきを低減することにより、半導体素子の信頼性および製造歩留まりを向上させる。

【解決手段】成膜装置のドライクリーニング処理用のチャンバ27に備わるウエハステージ27a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド27cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ27から熱処理用のチャンバへ真空搬送した後、そのチャンバにおいて150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

(もっと読む)

半導体装置の製造方法

【課題】MISFETのゲート電極、ソース領域およびドレイン領域にニッケルシリサイド膜を形成した場合に、このニッケルシリサイド膜の高抵抗化および凝集を抑制できる一方で、層間絶縁膜中に含まれる水素や水分を充分に除去できる技術を提供する。

【解決手段】MISFETのゲート電極6a、6b、ソース領域およびドレイン領域にニッケルシリサイド膜16を形成する。その後、半導体基板1上に窒化シリコン膜17を形成する。続いて、半導体基板1に対してスパイクアニールを実施する。スパイクアニールは、例えば、レーザアニール装置を用いて行ない、温度を700℃以上1300℃以下にし、かつ、加熱時間を1マイクロ秒以上1ミリ秒以下にする条件で実施する。

(もっと読む)

161 - 180 / 242

[ Back to top ]