Fターム[5F033XX08]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 低抵抗化 (1,713)

Fターム[5F033XX08]の下位に属するFターム

コンタクト抵抗の低減 (898)

シート抵抗の低減 (573)

Fターム[5F033XX08]に分類される特許

121 - 140 / 242

半導体集積回路装置

【課題】

ビルディングブロック方式では、電源ライン及びグランドラインの配置によって、半導体集積回路装置の微細化が困難であった。

【解決手段】

アナログ信号処理機能を担う電子回路ブロックが集積化された半導体集積回路装置であって、電源ラインは、電子回路ブロックを構成する半導体素子上の領域を含んで配置され、グランドラインは、電子回路ブロック間に位置する分離領域上に形成され、グランドラインは、コンタクト孔において分離領域とコンタクトされる。

(もっと読む)

導電性の構造物を含む半導体構造および形成方法

半導体構造(300)は、半導体基板(301)を有する。前記半導体基板(301)の上に電気絶縁材料の層(304)が形成されている。前記電気絶縁材料の層(304)に導電性の特徴(312)が形成されている。前記導電性の特徴(312)と前記電気絶縁材料の層(304)の間に第1の半導体材料の層(320)が形成されている。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】駆動能力を向上させた半導体装置を提供する。

【解決手段】半導体装置には、ゲート幅方向に断続的に深さの変化する凹部を設けるためのトレンチ部3が形成されており、ゲート絶縁膜6を介して、トレンチ部3の内部及び上面部にゲート電極7が形成されている。ゲート電極7のゲート長方向の一方の側にはソース領域9が形成されており、他方の側にはドレイン領域10が形成されている。ソース領域9とドレイン領域10の少なくとも一部では、ゲート電極7の形成前にトレンチ部3の内壁からイオン注入を用いて不純物添加をおこなった後、拡散および活性化の熱処理を施すことによって、トレンチ部3の表面から底部にかけて深く形成させることを可能とする。これにより、ゲート電極7の凹部上面に集中して流れていた電流がトレンチ部3の全体に一様に流れるようになり、ゲート幅方向に深さが変化するように形成された凹部の実効的なゲート幅が広がる。このため、半導体装置のオン抵抗が低下し、駆動能力が高まる。

(もっと読む)

半導体集積回路

【課題】配線の低抵抗化を図り、電圧ドロップを抑制できる配線構造を備えた半導体集積回路を提供する。

【解決手段】半導体集積回路の電源配線構造は、第1の方向に延伸して形成された複数の配線1D及び1Sからなる配線層1と、配線層1の上に、第1の方向に対して垂直な方向である第2の方向に延伸して形成された複数の配線2D及び2Sからなる配線層2と、配線層2の上に、第2の方向と同じ方向に延伸して形成された複数の配線4D及び4Sからな配線層4とを備える。

(もっと読む)

基板配線用導電性組成物、回路基板及び電子デバイス

【課題】貫通電極又は回路パターンの凝固収縮に起因する問題を解決しえる基板配線用導電性組成物、回路基板、及び、電子デバイスを提供すること。

【解決手段】50wt%以上のビスマス(Bi)と、30wt%以下のインジウム(In)と、30wt%以下の錫(Sn)と、1〜5wt%の範囲で選択された銅(Cu)とを含有する導電性組成物によって、貫通電極3及び回路パターン2を形成する。Biの体積膨張特性を利用することにより、課題を解決することができる。

(もっと読む)

半導体パッケージとその製造方法

【課題】絶縁樹脂層を介して第一配線と第二配線とが重ねて配され、局所的にそれらの重なり方向から見て交差部が存在する構造とした半導体パッケージにおいて、交差部の前後でビアやパッドを必要とせず、ひいては省スペース化が図れる構造とした半導体パッケージを提供することを第一の目的とする。

【解決手段】基板1の一面に配した絶縁樹脂層3内にあり、絶縁樹脂層3を介して下から順に配される第一配線2bと第二配線2aは、その重なり方向から見て交差部を形成する半導体パッケージであって、前記交差部を除いた第一配線2bの上面と、第二配線2aの上面とは、絶縁樹脂層3から露呈し、かつ、第一配線2bは、その厚み方向にシード層を2つ以上有することを特徴とする。

(もっと読む)

透明導電性基板

【課題】不純物を含まずカーボン粒子同士の密着性が強く、ひいては容易に剥がれず、腐食に強く、長期安定性に優れた透明導電性基板を提供する。

【解決手段】本発明に係る透明導電性基板1は、透明基材2と、該透明基材の一方の面に配された透明導電膜3と、前記透明導電膜上に載置されたカーボンナノチューブからなる配線部4と、を少なくとも備え、前記カーボンナノチューブは、バインダーを含有せずに前記透明導電膜上に載置されていることを特徴とする。

(もっと読む)

貫通導電体を有する半導体装置およびその製造方法

【課題】 より簡単な方法(プロセス)で且つより低い製造コストで製造できる、貫通導電体を有する半導体装置とその製造方法を提供する。

【解決手段】

SiO2膜(第1絶縁膜)23は、シリコン基板11の貫通孔14の内側面とシリコン基板11の裏面を覆うと共に、表面電極15の裏面に達する透孔31を貫通孔14の内部に持つ。配線膜24は、SiO2膜23上に所定パターンで形成されると共に、貫通孔14の内部で透孔31を介して表面電極15の裏面に接触せしめられている。外部電極25は、配線膜24上に形成されていて、貫通孔14の内部で配線膜24の内側に残存する空隙を充填する充填部25aを持ち、配線膜24の貫通孔14の内部にある部分と充填部25aとが、貫通導電体として機能する。

(もっと読む)

積層構造およびその製造方法

【課題】酸化物透明導電膜とAl合金膜との接触電気抵抗を増加させることなくAl合金が直接接続し、配線抵抗が小さく、現像液などの電解質液中でガルバニック腐食が生じにくい積層構造およびその製造方法を提供する。

【解決手段】酸化物透明導電膜とAl合金膜とが直接接続されてなる積層構造を製造する方法であって、基板上に前記酸化物透明導電膜を形成する第1の工程と、該酸化物透明導電膜上にアルミニウムよりもイオン化傾向の小さい合金成分を含有するAl合金膜を形成する第2の工程と、前記Al合金膜をアルミニウムと前記合金成分よりなる金属間化合物の析出温度以上に加熱する第3の工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜に開口された接続孔の内部に、チタン膜上に窒化チタン膜が形成された積層構造のバリアメタル膜を介して金属膜を埋め込んだ接続部における不具合を回避する。

【解決手段】コンタクトホールC1を形成して、その底部にニッケルシリサイド層14を露出させた後、TiCl4ガスを用いた熱反応により熱反応Ti膜21aを形成し、TiCl4ガスを用いたプラズマ反応によりプラズマ反応Ti膜21bを形成し、H2ガスを用いたプラズマ処理を施して、プラズマ反応Ti膜21bの塩素濃度を低減すると同時に、ニッケルシリサイド層14の表面の酸化膜を還元し、NH3ガスを用いた熱窒化処理及びNH3ガスを用いたプラズマ処理を施して、プラズマ反応Ti膜21bの表面に窒素リッチTiN膜21cを形成すると同時に、ニッケルシリサイド層14の表面の酸化膜を還元する。

(もっと読む)

半導体装置

【課題】 Cu配線から低誘電率材料(Low−k材料)絶縁膜へのCuの拡散を防止することができるとともに、Cu配線の抵抗の増大を防止することができる半導体装置を提供すること。

【解決手段】 半導体装置1では、SiOCからなる層間絶縁膜5には、配線溝8が形成されている。配線溝8の内面(ビアホール6の側面6Bおよびトレンチ7の側面7B)には、SiO2からなる第1バリア膜9が形成されている。配線溝8の内面(第1バリア膜9の表面、トレンチ7の底面7Aおよび第1Cu配線2の露出面)には、第2バリア膜10が形成されている。配線溝8には、Cu配線部19が埋設されている。Cu配線部19の配線溝8との対向面(Cu配線11の底面11Aおよび側面11B、ならびに接続ビア18の底面18Aおよび側面18B)は、第2バリア膜10で被覆されている。

(もっと読む)

半導体集積回路用インダクタ及びその製造方法

【課題】広大な断面積が得られ、抵抗値を著しく低下させることができてQ値を向上させることができると共に、膜厚の均一性が高い半導体集積回路用インダクタ及びその製造方法を提供する。

【解決手段】ダマシン法により形成された多層配線層の最上層配線層18上に、スパイラルインダクタ40が形成されている。このインダクタ40は、最上層配線29が形成された絶縁膜17a上に、この最上層配線29に接触するようにしてバリアメタル層をパターン形成し、その後、全面に保護絶縁膜を形成した後、この保護絶縁膜におけるバリアメタル層上の部分を開口し、その上に更にバリアメタル層を全面に形成し、このバリアメタル層をメッキ電極としてCu膜をメッキにより厚く形成し、このCu膜を湿式エッチングすることにより、形成する。このため、膜厚が厚く、線幅が広いインダクタ40を形成することができる。

(もっと読む)

半導体装置のAl系合金配線形成方法

【課題】電気抵抗率が低く、膜の緻密性や絶縁膜との密着性に優れているといった高品質を安定して発揮する信頼性の高い半導体装置用の配線の形成方法を提供する。

【解決手段】基板上に形成された凹部3を有する絶縁膜2の表面に、AlまたはAl合金(以下「Al系金属」という)よりなる薄膜5をスパッタリング法で形成した後、高温高圧処理を施して該Al系金属を上記凹部内に充填して半導体装置の配線を形成する方法であって、上記スパッタリングを下記条件で行なうことを特徴とする半導体装置の配線形成方法。スパッタリングガス圧:0.5〜1.1mTorr、放電パワー密度:3〜15W/cm2、基板温度:100〜300℃

(もっと読む)

拡散バリアフィルムを含む半導体素子の形成方法

【課題】電気抵抗が低く、下部導電体と上部導電体間の拡散を防止する、拡散バリアフィルムの形成方法を提供する。

【解決手段】下部導電体102を含む基板100上に層間絶縁膜104を形成する。これに形成された開口部106に補助拡散バリア膜108を形成する。この上に拡散バリアフィルム120を形成する。この膜は、金属有機化学気相蒸着法による金属窒化物で形成され、部分的にプラズマ処理される。この結果、プラズマ処理された層とプラズマ処理されない層の積層膜となる。これにより、拡散バリアフィルムの比抵抗を減少させると共に、優れたバリア特性を有することができる。さらにこの上に粘着金属層122、第1アルミニウム膜130、第2アルミニウム膜132を形成する。これらの膜をパターンニングして上部導電体とプラグとする。

(もっと読む)

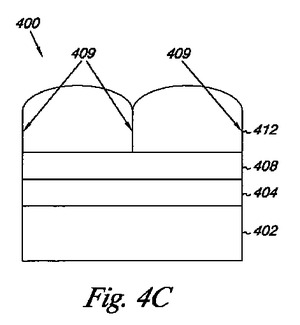

タングステンディジット線、その形成方法及び動作方法

タングステンディジット線を使用するための、及び、形成するための、方法、デバイス、及び、システムが記載されている。本開示の実施例に従って形成されたタングステンディジット線は、窒化タングステン(WNX)基板(402)上のタングステン(W)単分子層(404)と、W単分子層上のホウ素(B)単分子層(308)と、B単分子層上のバルクW層(412)とで形成されうる。バルクW層は、100nmから600nmの間の粒子サイズを有する。ディジット線は50nm未満の幅となりえる。従って、ディジット線のキャパシタンス及び抵抗は減少する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】貫通電極に空洞部が形成されることを防止する。

【解決手段】第1半導体基板1の表面および貫通孔2の内壁面を保護膜3で覆った状態で導体にて構成されたパッド8の表面に導体膜11を結晶成長させる。この導体膜11にて、貫通電極4を形成する。このように、パッド8の表面に主に結晶成長させ、保護膜3には結晶成長がほとんど起こらない選択成長によって貫通電極4を形成しているため、空洞の無い、良好な貫通電極4とすることができる。このため、断線・配線抵抗の増加を防止できると共に、EM耐性の低下等も防止することが可能となる。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】配線を形成するトレンチ幅が70nm以下になっても配線の抵抗率が大幅に増加せず、国際半導体技術ロードマップに開示されている値を満たす銅配線を実現する。

【解決手段】銅配線の配線幅が70nm以下で、トレンチの側面と平行な面における平均結晶粒径Dと配線幅Wの比D/Wを1.3以上にする。

(もっと読む)

半導体装置およびその製造方法

【課題】パワー素子と他の半導体デバイスとの複合型の半導体装置において、多層配線によって半導体デバイスの電極を最上層まで引き伸ばすに際し、多層配線のうちパワー素子における配線抵抗を小さくしつつ、多層配線の配線層にクラックを生じさせないようにする。

【解決手段】積層配線20のうち第1領域11におけるパワーMOSトランジスタのソース電極32、ドレイン電極31を積層配線20の2層目の配線層22より上層の配線層23〜25において、複数の微細なビアホールを用いずに1つの電極としてそれぞれ形成する。

(もっと読む)

金属薄膜配線

【課題】 密着性の確保と抵抗値の上昇を抑制した下地膜あるいはカバ−膜を有する金属薄膜配線を提供する。

【解決手段】 Ag膜、Cu膜、Au膜あるいはこれらを主体とする合金膜の下地膜として、Tiを2〜50原子%含有し、残部Moおよび不可避的不純物からなるMo合金膜が積層されてなる金属薄膜配線である。また、Ag膜、Cu膜、Au膜あるいはこれらを主体とする合金膜のカバー膜として、Tiを2〜50原子%含有し、残部Moおよび不可避的不純物からなるMo合金膜が積層されてなる金属薄膜配線である。

(もっと読む)

半導体装置およびその製造方法

【課題】接地インダクタンスを低減化した半導体装置およびその製造方法。

【解決手段】半絶縁性基板11の第1表面に配置され,複数のフィンガーを有するゲート電極、ソース電極およびドレイン電極と、第1表面と反対側の第2表面に配置された接地導体26と、ゲート電極、ソース電極およびドレイン電極ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極14、ソース端子電極18およびドレイン端子電極12と、ゲート電極、ソース電極およびドレイン電極の下部の半絶縁性基板11上に形成された動作層と、動作層近傍の小口径VIAホール30と接地導体26近傍の大口径VIAホール20とからなる多段VIAホールと、多段VIAホールの内壁面および第2表面に形成され、ソース端子電極18に対して第2表面側から接続された接地電極23とを備える半導体装置およびその製造方法。

(もっと読む)

121 - 140 / 242

[ Back to top ]