Fターム[5F033XX08]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 低抵抗化 (1,713)

Fターム[5F033XX08]の下位に属するFターム

コンタクト抵抗の低減 (898)

シート抵抗の低減 (573)

Fターム[5F033XX08]に分類される特許

41 - 60 / 242

半導体装置の製造方法

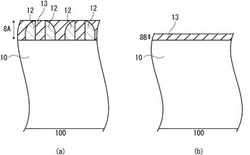

【課題】 メモリセルアレイ領域と周辺回路領域との配線溝の深さを最適化する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、レジストパターンをマスクとして芯材膜を加工する工程と、前記芯材膜上に被加工膜とエッチング選択比がある側壁膜を形成する工程と、前記側壁膜を異方性エッチング工程により加工する工程と、前記芯材膜を前記側壁膜と選択的に除去する工程と、第1領域の前記側壁膜上および前記被加工膜上に絶縁膜を第1の膜厚を有するように形成し、第2領域の前記被加工膜上に前記絶縁膜を第2の膜厚を有するように形成する工程と、を備えている。さらに、前記第2領域においてフォトリソグラフィ工程によりレジストパターンを形成する工程と、前記第1領域における前記側壁膜と前記第2領域における前記レジストパターンとをマスクとして前記絶縁膜および前記被加工膜を加工し、前記被加工膜に配線溝を形成する工程と、を備えている。

(もっと読む)

低誘電率材料形成用原料

【課題】 耐水性に優れた低誘電率材料を得る。

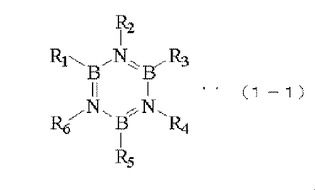

【解決手段】 化学式(1―1)

【化1】

で示されるボラジン系原料を有機溶媒に分散または溶解させたものを低誘電率材料形成用原料とする。式中のホウ素原子もしくは窒素原子が備える手が結合手となってボラジン環が結ばれたボラジン骨格系構造を形成し、上記ボラジン骨格系構造が繰り返されたオリゴマーまたはポリマーとして低誘電率材料を生成する。ただし式中、上記結合手以外のR1〜R6は、水素原子、炭素原子数1〜2のアルキル基の少なくともいずれかであって、少なくとも1つは水素原子ではなく、少なくとも1つは水素原子である。

(もっと読む)

半導体チップ及びそれを搭載した半導体モジュール

【課題】半導体チップに安定した電源電流を供給したり、電源から信号系へ混入する雑音を低くするための、半導体デバイスの電源流入及び電源流出端子の端子数の低減と、前記半導体チップを搭載した実装面積の低減を可能とする半導体モジュールを提供する。

【解決手段】半導体チップ20の両面に電源系と信号系の電気的接続端子を振り分けて配置する。大電流が流れる流路の許容電流値を大きくする構成により、少ない端子数でも安定な電源供給が可能、信号系への雑音混入を低減、ピン数の低減による実装面積の低減、放熱効果の増大などが可能となる。また、この半導体チップ20を搭載した半導体モジュールにより、大電流が流れる高速動作でも安定した特性を実現できる。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】Cuを主要な成分とする再配線に設けられた外部接続用Auパッドの剥離を抑制する。

【解決手段】Cu膜15aの上部にNi膜15bを積層した2層膜からなる再配線15の表面には、ワイヤが接続されるパッド18が形成されている。パッド18は、Ni膜19aの上部にAu膜19bを積層した2層膜からなり、再配線15の上面および側面を覆うように一体形成されている。これにより、再配線15とパッド18の接触面積が大きくなるので、パッド18が再配線15から剥がれ難くなる。

(もっと読む)

半導体装置

【課題】大画面化しても低消費電力、歩留まり及び信頼性の向上を実現するための半導体

装置の構造及びその作製方法を提供する。

【解決手段】画面で使われる画素薄膜トランジスタを逆スタガ型薄膜トランジスタで作製

する。その逆スタガ型薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上

に作製する。また、ソース配線と逆スタガ型薄膜トランジスタ、画素電極と逆スタガ型薄

膜トランジスタをつなぐ金属配線を同一工程で作製する。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積の増加を抑制しつつ、ウェハ状態でのスクリーニング時に電源電圧低下(IRドロップ)を抑えることができる半導体装置を提供する。

【解決手段】本発明の一形態に係る半導体装置50は、半導体チップ100と、半導体チップ100上面の中央部のチップ中央領域120に形成された複数の外部接続用パッド102及び複数の検査用パッド104と、複数の外部接続用パッド102上に形成されたバンプ105とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に伴うLERやLWRに起因する配線の抵抗率の増大を抑制し得る手法を提供する。

【解決手段】半導体装置は、基板101と、基板上において同一の配線層内に形成された複数の配線111と、配線間に埋め込まれるよう形成された複数の絶縁膜112とを備える。そして、これら複数の配線は、両側面のLER(Line Edge Roughness)の相関係数が正である配線が、連続して2N本(Nは4以上の整数)以上並んだ配線群を含む。

(もっと読む)

配線構造物及びその製造方法

【課題】短時間で、配線母体の内部に、種々のトポロジーの貫通配線や連結配線を埋め込むことが可能な配線構造物を提供する。

【解決手段】配線母体11と、配線母体11の内部に設けられた複数の穴部の内部にそれぞれ配置された、配線子連続体(Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1n)からなる複数の貫通配線部とを備える。複数の配線子連続体のそれぞれをなす複数の配線子Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1nのそれぞれは、コア部と、コア部を被覆し、コア部より融点の低い導電体からなるシェル部Qi,shell,Qi+1,shellを有する。複数の配線子は、それぞれのシェル部を互いに溶融することにより金属学的に接合される。

(もっと読む)

半導体装置の製造方法

【課題】バリア金属膜の膜厚を薄膜化でき、金属配線やビア内にボイドの無い配線を形成可能な半導体装置の製造方法を提供する。

【解決手段】半導体構造は、相互接続トレンチ又はビア305に薄いバリア金属層307が、トレンチやビアの開口が相互接続トレンチやビアへの銅の配置を疎外する張り出しにより妨害されないように形成される。銅の相互接続配線314を形成するための材料は、銅とマンガンを含んでいる。アニールにより、銅の拡散に対してバリア特性を有する酸化マンガン層315が形成される。

(もっと読む)

ドライバー集積回路チップの電源連結構造

【課題】本発明は、ドライバー集積回路チップの電源連結構造に関し、より詳細には、ドライバー集積回路チップ内部のルーティングパターンをLOGと並列で配置して、チップの両端に配置された電源を連結することで配線を簡素化してライン抵抗を減少させることができるドライバー集積回路チップの電源連結構造を提供する。

【解決手段】本発明によるドライバー集積回路チップの電源連結構造によると、ドライバー集積回路チップの入出力端子の配線数を減少させて配線を簡素化して、これによりチップサイズを減らして及び製造費用を減少させることができる効果があり、チップ内部のルーティングパターンとLOGを並列で連結することでライン抵抗が減少されて、信号の遅延を減らすことができる長所がある。

(もっと読む)

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

高電圧スイッチング回路

【課題】高電圧処理能力および改善された実行能力を有する効率的なスイッチング回路を提供する。

【解決手段】第1および第2のIII−V族トランジスタを有し、第2のIII−V族トランジスタは、第1のIII−V族トランジスタよりも大きな降伏電圧を有する。さらに、第1のIII−V族トランジスタと並列に配置されるシリコンダイオードを有し、この並列配置は、第2のIII−V族トランジスタと直列に接続、効率的な3端子デバイスであり、第1端子は第2のIII−V族トランジスタのゲート、第1のIII−V族トランジスタのソースおよびシリコンダイオードのアノードに結合する。第2端子は第1のIII−V族トランジスタのゲートと結合し、第3端子は第2III−V族トランジスタのドレインと結合する。

(もっと読む)

半導体デバイス障壁層

【課題】本発明は、半導体デバイス要素のメタライゼーション及び誘電体材料の不活性化に使用される障壁層に関する。

【解決手段】半導体デバイスメタライゼーション要素用の障壁層は、要素くぼみ中に形成されたシリコン窒化物薄膜とシリコン窒化物薄膜上に形成された耐熱性金属薄膜を供する。デバイス要素は誘電体材料及び誘電体中に形成されたくぼみを含む。くぼみ内の誘電体材料の表面は、制御されたパラメータ下で窒素に露出される。くぼみの内部に隣接した誘電体材料の部分は、シリコン窒化物に変換される。

耐熱性金属は次に、くぼみの側壁に沿って、適合して堆積される。次に、耐熱性金属薄膜上にシード層が堆積され、次にくぼみ内に導電性金属が堆積される。次に、くぼみの外の過剰の金属を除去し、デバイスを平坦化するため、デバイスを研磨する。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

シリコンおよびIII−V族のモノリシック集積デバイス

【課題】シリコン基板上にIII−V族半導体で形成されたHEMTとシリコン面に形成されたショツトキーダイオードのモノリシック集積デバイスを開示する。

【解決手段】少なくとも1つのビアは、III−V族半導体を通じて延在して、III−V族トランジスタの少なくとも1つの端子をシリコン基板に形成されたシリコンデバイスに結合させる。シリコンデバイスはショットキーダイオードと、III−V族トランジスタはGaNHEMTとすることができる。ショットキーダイオードのアノードは、一実施形態においては、シリコン基板202に形成され、他の実施形態においては、シリコン基板上の低濃度にドープされたエピタキシャルシリコン層204に形成される。HEMTはGANで構成されたチヤネル層212、AlGaNで構成された電子供給層214より構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の表皮効果の抑制と低抵抗化を図る。

【解決手段】第1配線部41と、その第1配線部41の周りを被覆する、高融点金属窒化物を含む第2配線部42とを含む配線40aを形成する。このような配線40aにおける第2配線部42は、第1配線部41側から外周に向かって窒素含有率が高くなる部分を有するように形成する。これにより、配線40aにおける表皮効果が抑制されると共に、配線40aの低抵抗化が図られるようになる。

(もっと読む)

はんだ濡れ性の前面金属部を備えるIII族窒化物パワーデバイス

【課題】外部回路接続に棒はんだを用いる、複数の相互接続金属層およびはんだ濡れ性の前面金属部構造を備えるHEMTを含むIII族窒化物パワーデバイスの、いくつかの典型的な実施形態を提供する。

【解決手段】はんだ濡れ性の前面金属部140aおよび140bの構成は、TiNiAgのようなトリメタルからなり、HEMTのソースおよびドレインコンタクトを交互の細長いデジットまたはバーとして露出するように設けられる。また、単一のパッケージは、前面金属部構造140aおよび140bが交互の相互嵌合したソースおよびドレインコンタクトを露出する、こうしたHEMTを多数集積し、これはIII族窒化物デバイスを用いるDC‐DCパワー変換回路設計に有利となり得る。外部回路接続に棒はんだを用いることにより、横方向の導電が可能となり、これによりデバイスのオン抵抗Rdsonを低減する。

(もっと読む)

電子デバイス及びその製造方法

【課題】絶縁基板2に形成した貫通電極6の導電率及び熱伝導率を向上させる。

【解決手段】電子デバイス1は、表面に窪み4を有し、この窪み4の底面から裏面に貫通する貫通孔3が形成された絶縁基板2と、貫通孔3に充填され、ナノ金属粒子と10μm以下の平均粒径導電性フィラーを混合した金属ペーストの熱処理により形成された貫通電極6と、窪み4に収納され、貫通電極6に電気的に接続される電子部品7と、この電子部品7を封止する封止部9とを備えており、貫通電極6の導電率及び熱伝導率を向上させた。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストの増加および歩留まりを低下させることなく、配線抵抗を下げることのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板100上の絶縁膜104上にマスク材料膜106を形成した後、第1のトレンチ形成用開口と第2のトレンチ形成用開口とを有するマスクパターン109をマスク材料膜106に形成する工程と、マスク材料膜106上に、第1のトレンチ形成用開口を露出する第3のトレンチ形成用開口112を有し、且つ、第2のトレンチ形成用開口部を覆うレジストパターン113を形成する工程と、レジストパターン113及びマスクパターン109を用いて、絶縁膜104内に第1のトレンチ115を形成する工程と、レジストパターン113を除去した後、マスクパターン109を用いて、絶縁膜104内に第2のトレンチを形成する工程とを備えている。

(もっと読む)

半導体集積回路

【課題】少なくともロジック回路ブロックを含む半導体集積回路において、半導体集積回路の電源用パッドとロジック回路ブロックの電源ラインとを接続する電源配線、及び/又は、半導体集積回路のグランド用パッドとロジック回路ブロックのグランドラインとを接続するグランド配線の抵抗値を下げる。

【解決手段】この半導体集積回路は、半導体基板と、半導体基板上にそれぞれの層間絶縁膜を介して形成され、半導体基板に形成された複数のトランジスタに接続されて複数のトランジスタと共に少なくともロジック回路ブロックを構成する複数の配線層と、複数の配線層が形成された半導体基板上に層間絶縁膜を介して形成され、複数の配線層における最大膜厚の5倍〜20倍の膜厚を有する最上層の配線層とを具備する。

(もっと読む)

41 - 60 / 242

[ Back to top ]