Fターム[5F033XX08]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 低抵抗化 (1,713)

Fターム[5F033XX08]の下位に属するFターム

コンタクト抵抗の低減 (898)

シート抵抗の低減 (573)

Fターム[5F033XX08]に分類される特許

61 - 80 / 242

配線基板の製造方法

【課題】スループットが向上し、且つ少ない液滴量でも第1の電極と第2の電極とを導通性を確保する。

【解決手段】基体10の表面10aに形成された微細穴2の底部2aとなる下面電極3と、基体10の表面10aであって微細穴2の内壁部2bの上端近傍に配置された上面電極5とを導通させる導電層12を形成する。この導電層12の形成において、まず、金属ナノ粒子11を分散させるためのクリアインク8を微細穴2に充填する。次に、微細穴2に金属ナノ粒子11を含有する液滴を供給し、金属ナノ粒子11を微細穴2内のクリアインク8で分散させる。次に、微細穴2内のクリアインク8を揮発させることで、微細穴2の底部2a及び内壁部2bに析出した金属ナノ粒子膜11Aを有する導電層12を形成する。

(もっと読む)

半導体装置

【課題】電子回路の小型化を実現する。

【解決手段】MOSトランジスタ20が、格子状に形成されたゲート電極22と、ゲート電極22で囲まれたソース領域23およびドレイン領域24と、ゲート電極22の格子の一方向に沿って配置され、ソース領域23およびドレイン領域24とコンタクトを介して接続するソース用メタル配線27およびドレイン用メタル配線28を有する。ソース領域23およびドレイン領域24のそれぞれは、各メタル配線の長さ方向に長辺を有する長方形状に形成される。ソース用メタル配線27およびドレイン用メタル配線28は、その長さ方向にジグザグ形状に形成されて、それぞれソース用コンタクト25およびドレイン用コンタクト26に接続する。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

導電性バリア膜形成材料、導電性バリア膜形成方法、及び配線膜形成方法

【課題】溝や穴の開口部と深さとの比(開口部/深さ)が1/5〜1/7のような条件を要求されても、又、厚さが10nm以下であっても成膜が可能で、かつ、銅の拡散防止(バリア性)に優れ、更には電気抵抗が小さく、銅膜との密着性にも優れた導電性バリア膜形成材料を提供する。

【解決手段】ケミカルベーパーデポジションにより銅膜の下地膜として導電性Ta−Zr系バリア膜を形成する為の材料であって、Taを持つ金属有機化合物と、Zrを持つ金属有機化合物とを含むことを特徴とする導電性バリア膜形成材料、および、前記Ta有機化合物、前記Zr有機化合物の一方または双方を溶解する溶媒とを含むことを特徴とする導電性バリア膜形成材料。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体素子の電極パッド間の距離の縮小や半導体素子のサイズを拡大することなく多ピン化への対応が可能となり、回路コア部の電源の出力電圧が降下するIRドロップ現象を防止することができる半導体装置を提供する。

【解決手段】半導体素子3の回路形成領域4の外周部に外周部電極パッド5が形成され、各外周部電極パッド5に外周部バンプ10が形成され、回路形成領域4の範囲内に内部電極パッド14が形成され、内部電極パッド14に内部バンプ16が形成され、フリップチップ実装により、半導体素子3と半導体基板との間にエポキシ系樹脂材を介在させて、各外周部および内部バンプ10,16と半導体基板の各配線電極部とが接続される。

(もっと読む)

貫通電極基板及び貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板は、表裏を貫通する貫通孔を有する基板と、前記貫通孔内に充填され、金属材料を含む導通部と、を備え、前記導通部は、結晶粒径が29μm以上の金属材料を少なくとも含み、前記導通部の一端は、前記導通部の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部は、面積重み付けした平均結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

透明電極パターンの形成方法

【課題】表面荒れが少なく、光の透過率の高い透明電極パターンを容易に形成できる技術を提供する。

【解決手段】本発明の透明電極パターンの形成方法によれば、基材の一面に透明電極層を形成する透明電極層形成工程と、前記透明電極層の一部を覆い、前記透明電極層の他部を露出するようにパターニングされたマスクを形成するマスク形成工程と、前記マスクおよび前記透明電極層の表面に金属膜を成膜する金属膜成膜工程と、エッチングにより前記金属膜の一部を残し金属配線を形成し、前記マスクの一部と前記透明電極層の前記他部の一部を露出させる第1エッチング工程と、前記第1エッチング工程で露出した前記透明電極層を前記マスクの一部をマスクとしてエッチングすることにより透明電極のパターンを形成する第2エッチング工程と、を有する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

インダクターおよび集積回路装置

【課題】 インダクター配線のインピーダンスの低減と、インダクター配線と基板等との間に形成される寄生容量の低減とを共に実現する。

【解決手段】 多層配線を利用して基板上に構成されるインダクターは、第n層の導体層ME(n)により形成される第1インダクター配線100と、第1インダクター配線100と電気的に接続される、第(n+α)層(αは、1以上の整数)の導体層ME(n+1)により形成される第2インダクター配線200と、を有し、第1インダクター配線100にはスリットが設けられておらず、第2インダクター配線200には、第2インダクター配線の延在方向に沿う少なくとも一つのスリットSL1が設けられている。

(もっと読む)

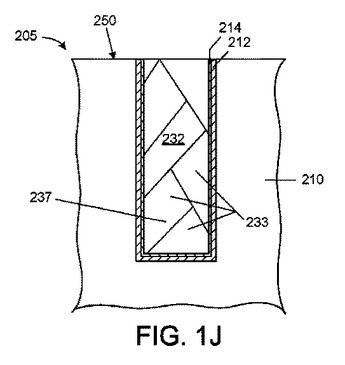

切欠構造のなかで長尺状ルテニウム膜上に多段階式銅鍍金を行う方法。

先端の集積回路にみられる切欠構造(206,207,208,209,211,213,264,275a,275b)において、長尺のルテニウム金属膜(214)に多段階で銅鍍金を行う方法である。長尺のルテニウム金属膜 (214)を利用すると、銅金属がトレンチ(266)及びビア(268)のような高アスペクト比の切欠構造(206,207,208,209,264,275a,275b)を充填するあいだ、不要な微細気泡が形成を防ぎ、前記ルテニウム金属膜(214)上に長尺の銅金属層(228)を含むサイズの大きい銅粒(233)が鍍金形成される。銅粒(233)は銅が充填された切欠構造(206,207,208,209,211,213,275a,275b)の電気抵抗を低下させ、集積回路の信頼性を向上させる。  (もっと読む)

(もっと読む)

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】本発明の半導体素子の形成方法は、基板上に半導体構造物及び絶縁パターンを形成し、絶縁パターンの一面によって定義される側壁と半導体構造物の底によって定義される底を有するオープニングを形成し、オープニングを満たす第1金属膜を形成し、第1金属膜を湿式エッチングしてオープニングの側壁を少なくとも一部露出させ、第1金属膜上に第2金属膜を選択的に形成することを含む。

(もっと読む)

半導体装置の作製方法

【課題】電界メッキ法やCMP法を使わないことで製造コストを落として配線を形成する半導体装置の作製方法を提供する。

【解決手段】絶縁膜を形成する工程と、絶縁膜上にマスクを形成する工程と、選択的にエッチングして絶縁膜に開口部を形成する工程と、マスク上および開口部に第1導電膜を形成する工程と、液滴吐出法により開口部の第1導電膜上に導電材料を含む液滴を滴下する工程と、レーザー光を選択的に照射して導電材料を加熱して第2導電層を形成する工程と、マスク上および第2導電層上に第3導電膜を形成する工程と、マスクを除去すると同時にマスク上に形成された第1導電膜および第3導電膜を除去し、第1導電層および第3導電層を形成する工程とを有する半導体装置の作製方法を提供する。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の一端は、導通部106の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部106は、結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

半導体装置

【課題】パワーMISFETのゲート抵抗を低減し、装置の特性の向上を図る。

【解決手段】チップ領域CAのY方向にストライプ状に形成された複数の溝の内部の多結晶シリコン膜よりなるゲート部と電気的に接続されるゲート電極GEを、前記ストライプ状の溝の間に形成されるソース領域と電気的に接続されるソース電極SEと同層の膜で形成し、さらに、ゲート電極GEを、チップ領域CAの周辺に沿って形成されたゲート電極部G1と、チップ領域CAをX方向に2分割するよう配置されたゲートフィンガー部G2とで構成し、ソース電極SEを、ゲートフィンガー部G2の上部に位置する部分と、下部に位置する部分とで構成し、ゲート電極GEおよびソース電極SEをバンプ電極を介してリードフレームと接続する。

(もっと読む)

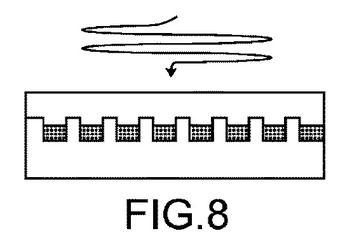

金属結晶領域、特に集積回路における金属結晶領域を生成する方法

本方法は、例えば相互接続ラインを形成するために、薄い結晶(8)のシートを、基板(1)のトレンチに堆積される、このシートと同一のタイプであるが、アモルファスであるか小さな粒径である金属(6)に固定することを含む。焼鈍しは、このラインにシートの結晶構造を徐々に与える。結晶(8)が除去されると、高度の導電結晶ラインが得られる。それは、その粒径が非常に拡大されているからである。金属は、銅、銀及びアルミニウムから選択される。  (もっと読む)

(もっと読む)

置換ゲート構造体を有するFET及びその製造方法

【課題】 マルチゲート型FETの置換ゲート構造体及びマルチゲート型FETの置換ゲート構造体の製造方法を提供する。

【解決手段】 MUGFET及びMUGFETを製造する方法が示される。MUGFETを製造する方法は、複数の活性領域の周りに一時的スペーサ・ゲート(図3の16)を形成することと、複数の活性領域の間を含む、一時的スペーサ・ゲートの上に誘電体材料(18a及び空間20内)を堆積させることとを含む。この方法は、誘電体材料(空間20内)の部分をエッチングして一時的スペーサ・ゲート(16)を露出させることと、一時的スペーサ・ゲートを除去して、活性領域と誘電体材料の残りの部分(18a)との間に空間を残すこととをさらに含む。この方法はさらに、活性領域と誘電体材料の残りの部分(18a)との間の空間(22)及び誘電体材料の残りの部分の上方をゲート材料で充填することを含む。

(もっと読む)

半導体装置

【課題】局所的な電圧降下を効果的に抑制できる電源配線構造を有した半導体装置を提供する。

【解決手段】第1配線層は複数の第1配線ブロック10を含み、当該各第1配線ブロック10には、第1電位を持ち且つ少なくとも二方向以上に延びる第1配線11と、第1電位と異なる第2電位を持ち且つ少なくとも二方向以上に延びる第2配線12とが配置されている。第2配線層は、隣り合う一対の第1配線ブロック10における第1配線11同士を電気的に接続する第3配線21と、当該一対の第1配線ブロック10における第2配線12同士を電気的に接続する第4配線22とを含む。

(もっと読む)

低損失多層オンチップインダクタ

【課題】多層構造のオンチップインダクタ素子において、インダクタの表皮効果を低減してQ値を向上させる。

【解決手段】単一のインダクタ配線1から構成される、又は複数のインダクタ配線1を上下に積層して並列接続したものから構成されるインダクタ配線層を3層以上有し、各インダクタ配線層は上下に積層されて直列接続されており、最上層と最下層のインダクタ配線層を除く中間層の各インダクタ配線層の実効的な膜厚が、該最上層及び最下層のインダクタ配線層の実効的な膜厚よりも大きいことを特徴とする、半導体基板上絶縁膜中のオンチップインダクタである。

(もっと読む)

半導体装置及びその製造方法

【課題】消費電流及び抗折強度に優れる半導体装置の製造方法を実現する。

【解決手段】

半導体装置の製造方法は、第1面の表面部に設けられた拡散領域12を備える半導体基板11を準備する工程(a)と、半導体基板11の第1面上に第1金属配線14a及び14bを形成する工程(b)と、半導体基板11を厚さ方向に貫通する貫通孔15を形成する工程(c)と、貫通孔15内に、第1金属配線14bの裏面から半導体基板11の第2面にまで延びる貫通電極16を形成する工程(d)と、半導体基板11の第2面に凹部17を形成する工程(e)と、凹部17内に、貫通電極16と電気的に接続された第2金属配線18を形成する工程(f)とを備える。

(もっと読む)

61 - 80 / 242

[ Back to top ]