Fターム[5F033XX08]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 低抵抗化 (1,713)

Fターム[5F033XX08]の下位に属するFターム

コンタクト抵抗の低減 (898)

シート抵抗の低減 (573)

Fターム[5F033XX08]に分類される特許

81 - 100 / 242

半導体装置の設計方法

【課題】配線層の溶出、および酸化を抑制する半導体装置、およびその設計方法を提供する。

【解決手段】接続コンタクトに接続される金属配線の配置を決定するステップと、接続コンタクトを設けるためのスルーホールの配置を決定するステップとを具備する半導体装置に設計方法を適用する。ここで、金属配線の配置を決定するステップは、(a)スルーホールによって露出する金属配線の領域を特定するステップと、(b)金属配線に付帯する容量を特定するステップと、(c)容量が蓄える電荷が、領域を介して金属配線から極性溶媒に移動したときの領域の損傷を抑制するように、金属配線の配置を決定するステップとを含むものとする。

(もっと読む)

グラフェンと金属電極との電気的接合デバイス、それを用いた電子デバイス,電子集積回路及び光/電子集積回路

【課題】グラフェンと金属電極との間の接触抵抗を低減する。

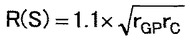

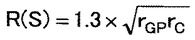

【解決手段】グラフェンの単位面積あたりの電気抵抗をrGP[Ω/μm2]、グラフェンと金属電極との単位面積当たりの界面抵抗をrC[Ωμm2]とすると、接触面積をSとして、接触抵抗は

と計算できる。rGPを10Ω/μm2、rCを10Ωμm2とした場合の計算結果を示し、接触面積を

にすることにより、接触抵抗を収束値の10%増し、あるいは30%増しの値にまで、低減することができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】側壁転写加工技術を用いる場合に、転写用のマスクが非対称な形状となることに起因した不具合を極力防止する

【解決手段】半導体基板1上に形成したシリコン酸化膜4にコンタクトプラグ5を形成し、シリコン窒化膜6、シリコン酸化膜7を積層し、芯材用膜を積層して芯材パターンに加工する。上面に非晶質シリコン膜を形成してスペーサ加工をしてマスクパターンを形成する。このとき、マスクパターンは、芯材パターンを挟んで対向するペア部の間隔に対して隣接部の間隔が小さくなるように形成される。芯材パターン除去の後、マスクパターンをマスクとしてシリコン酸化膜7、シリコン窒化膜6を加工して配線溝パターンを形成し、内部に導体膜8,9を埋め込み、埋め込み配線10a、10bを形成する。埋め込み配線10bは、上部で配線幅が広く形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】フリップチップ実装構造の半導体装置では、半導体基板(半導体チップ)裏面に抵抗を低減するための厚い金属層が設けられる。しかし、半導体チップの薄化が進むと、厚い金属層との応力の差により、半導体基板に反りが発生し、歩留まりが悪化する原因となっていた。

【解決手段】第1主面に動作領域が設けられ、第2主面に金属層が設けられる半導体基板(半導体チップ)の、少なくとも動作領域と一部重畳する第2主面側の半導体基板に凹部を設ける。これにより周辺部において第1の厚みを有し、凹部において第1の厚みより薄化された第2の厚みを有する半導体チップとする。周辺部が第1の厚みを有するため、第2主面側に厚い金属層を形成しても、半導体チップの反りを防止できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】含境界部分における金属シリサイド層の厚さに関係なく、金属シリサイド層の抵抗値を自由に調整することができる半導体装置を提供する。

【解決手段】半導体基板12に形成されたNチャネル型トランジスタ形成領域14と、Pチャネル型トランジスタ形成領域16と、Nチャネル型トランジスタ形成領域14とPチャネル型トランジスタ形成領域16とに跨って延在し、Nチャネル型トランジスタ形成領域14とPチャネル型トランジスタ形成領域16との境界線Lを含む領域に形成された含境界部分および境界線を含まない領域に形成された無境界部分を有すると共に、導電性シリコン層28と、導電性シリコン層28表面に形成され、含境界部分における厚さおよび無境界部分における厚さが異なる金属シリサイド層30(30A,30B)と、を備えるゲート電極と、を備えた半導体装置。

(もっと読む)

半導体装置

【課題】オン抵抗の増大を抑制しつつ、ゲート抵抗を低減して高速スイッチング化が図れる半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体層10におけるソース領域14が設けられた表面上に設けられソース領域14と接続された第1の主電極40と、ベース領域13に対して絶縁膜17を介して対向し第1の方向Xに延在するゲート電極16と、ゲート電極16と接続され半導体層10の表面上で第1の方向Xに交差して設けられた第1のゲート配線31と、第1のゲート配線31上に設けられ第1のゲート配線31と接続されたゲートコンタクト部32と、第1のゲート配線31上に設けられ、ゲートコンタクト部32を介して第1のゲート配線31と接続され、第1のゲート配線31よりも幅が広く且つ低抵抗な材料からなる第2のゲート配線32とを備えている。

(もっと読む)

半導体装置

【課題】ゲート電極の抵抗を低減しつつ、寄生容量やチップ面積の増大を抑制して、高周波特性を向上できる半導体装置を提供する。

【解決手段】実施形態の半導体装置は、ソース拡散層110とドレイン拡散層120とゲート電極100とにより構成された単位電界効果トランジスタを電気的に並列接続したマルチフィンガー構造の電界効果トランジスタと、この電界効果トランジスタの上部に電気的に接続した多層配線構造とを備え、ソース拡散層110の第2の配線(M1配線150)およびドレイン拡散層120の第3の配線(M1配線150)より上層にゲート電極100の第1の配線(M2配線160)を設けるものである。

(もっと読む)

表示装置用基板およびそれを備えた液晶表示装置

【課題】配線の低抵抗化を実現することができ、かつ配線と導電層との密着性を向上させることができる表示装置用基板およびそれを備えた液晶表示装置を提供する。

【解決手段】絶縁性基板10、絶縁性基板10上に設けられた配線4、配線4における絶縁性基板10の反対側に設けられた導電層12、並びに、配線4および導電層12を覆うように絶縁性基板10上に設けられた層間絶縁膜15を備えており、導電層12が金属ナノ粒子を含有し、配線4における導電層12との接触面にはスリット21が形成されている。

(もっと読む)

表示装置

【課題】 高抵抗である透明電極から低抵抗配線にコンタクトする場合のコンタクトホールにおいて、電力損失を低減しつつ、狭額縁化を図ることを目的とする。

【解決手段】 表示装置において、基板上に少なくとも薄膜トランジスタ、平坦化膜及び複数の発光素子が形成されており、発光素子には、少なくとも発光層と、第1の電極及び第2の電極を有している。この第1の電極と、第1電極よりも抵抗値の低い配線(GND配線又は電源配線)とを接続させるために、表示領域よりも外側の平坦化膜には複数の第1のコンタクトホール及び複数の第2のコンタクトホールが設けられており、第2のコンタクトホールは、表示領域から第1のコンタクトホールまでの距離に比べて遠距離に配置され、かつ第1のコンタクトホールよりも開口面積が小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】Q値の高いモノリシックインダクタ素子を備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置50は、半導体基板1と、半導体基板1上に設けられた層間絶縁膜6と、層間絶縁膜6の上部に埋め込むように設けられ、スパイラルパターンを有する第1インダクタ配線層7と、層間絶縁膜6上及び第1インダクタ配線層7上を覆うように設けられ、第1インダクタ配線層7に沿って延びる少なくとも一つの溝状接続孔10を有するバリア絶縁膜9と、バリア絶縁膜10上に、第1インダクタ配線層7に沿って延びるように形成されると共に、溝状接続孔10を埋め込んで第1インダクタ配線層7に電気的に接続された第2インダクタ配線層11とを備える。第2インダクタ配線層11は、その長さ方向に延びるように上面側に設けられた少なくとも一つの溝状凹部12を有する。

(もっと読む)

パターン形成基板

【課題】標的となる領域に液滴を塗布することができ、かつ、配線抵抗の増加を極力抑制することができるパターン形成基板を提供する。

【解決手段】本発明に係るパターン形成基板1bは、液滴が吐出されることによって、所定のパターンが形成されるものであり、上記液滴が接触したときの接触角が第1接触角である第1領域2と、上記液滴が接触したときの接触角が第2接触角であって、上記第1領域2に囲まれた第2領域3と、上記液滴が接触したときの接触角が第3接触角であって、第2領域3に囲まれた第3領域6とを有し、第2接触角は第1接触角および第3接触角よりも小さく、第3領域6と、第2領域3における液滴が吐出される塗布領域4と、液滴が吐出されない非塗布領域5とは互いに隣接するように形成されていることを特徴とする。

(もっと読む)

配線基板の製造方法及び表示装置

【課題】工程数の増加を抑制しながら配線抵抗を低下させることができる配線基板の製造方法及び表示装置を提供する。

【解決手段】基板上に配線を備える配線基板の製造方法であって、上記製造方法は、上記基板上に上記配線を形成し、上記基板から上記配線を凸状に突出させる工程と、導電粒子を含むインクを吐出し、上記配線の上面の幅全体に連続して広がるインク滴を上記配線上に配置する工程と、上記インク滴を焼成し、上記配線上に導電層を形成する工程とを含む配線基板の製造方法である。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106は、面積重み付けした平均結晶粒径が13μm以上の金属材料を少なくとも含む。また、導通部106は、結晶粒径が29μm以上の金属材料を含む。

(もっと読む)

半導体装置

【課題】接続不良を低減した半導体装置を提供する。

【解決手段】半導体装置100は、ワイヤ40にて外部電極と電気的に接続可能に構成されている。半導体装置100は、基板10と、その基板10上に形成され基板10とワイヤ40により電気的に接続される半導体チップ20とを備える。半導体チップ20は、ワイヤ40と電気的に接続された配線層23と、配線層23上に形成された保護層24を有する。配線層23は、保護層24が上層に形成される一方、下層において他の層と電気的に接続される配線部231Aと、保護層24が上層に形成されず露出した表面においてワイヤ40の一端が接続されるボンディング部231Bと、配線部231Aとボンディング部231Bとを結ぶ接続部231Cとを備える。接続部231Cは、配線層23を彫り込んで形成されたエッチング部60を備える。

(もっと読む)

Ti膜の成膜方法および成膜装置、ならびに記憶媒体

【課題】CVDによりTi膜を成膜する際に、より低抵抗でかつ抵抗のばらつきが小さいTi膜を成膜することができ、プラズマダメージを小さくすることができるTi膜の成膜方法を提供すること。

【解決手段】チャンバ内にシリコンウエハを配置し、TiCl4ガスおよびH2ガスを含む処理ガスを導入しつつチャンバ内にプラズマを生成し、そのプラズマにより処理ガスの反応を促進してシリコンウエハ上にTi膜を成膜するにあたり、チャンバ内にシリコンウエハが配置された状態でTiCl4ガスを導入した後、チャンバ内にプラズマを生成する。

(もっと読む)

銅配線、銅配線の形成方法および半導体装置

【課題】銅配線本体の開放表面に形成されるマンガンを含むバリア層に最適な内部構成を持たせて、そのバリア機能を充分に発揮させることができる半導体素子の製造方法を提供する。

【解決手段】銅配線1は、電気絶縁層3に銅からなる配線本体8を備える。配線本体の外周81は、電気絶縁層に対向している第1の外周8aと電気絶縁層との間に形成された第1のバリア層7aと、配線本体の外周のうち電気絶縁層に対向していない第2の外周8bに接して形成された第2のバリア層7bとを備える。第1および第2のバリア層はそれぞれマンガンを含む酸化物層からなるとともに、各バリア層内の厚さ方向でマンガンの原子濃度が極大となる位置を有する。

(もっと読む)

透明薄膜トランジスタ及び画像表示装置

【課題】配線抵抗を低下させて、均一かつ確実に動作させる透明薄膜トランジスタ及び画像表示装置を提供すること。

【解決手段】実質的に透明な基板と、基板上に実質的に透明な導電材料の第1の薄膜と金属材料の第2の薄膜とを2層以上積層して形成されたゲート配線と、ゲート配線上に形成された実質的に透明なゲート絶縁膜と、ゲート絶縁膜上に形成された実質的に透明な半導体活性層と、実質的に透明な半導体活性層を挟んで離間して形成された実質的に透明な導電材料の第5の薄膜と金属材料の第6の薄膜とを2層以上積層して形成されたソース配線と、実質的に透明な半導体活性層を挟み、ソース配線に離間して実質的に透明な導電材料の第7の薄膜で形成されたドレイン電極と、を備えることを特徴とする透明薄膜トランジスタ。

(もっと読む)

半導体装置およびその製造方法

【課題】Cu配線パターンとキャップ層との界面を伝うCuの拡散を抑制し、同時にCu配線パターンの抵抗の増大を抑制するCuダマシン配線の製造法を提供する。

【解決手段】基板41上に側壁面と底面とにより画成された凹部を有する絶縁膜45を形成する。側壁面のうち、上端部を含む上側の第1の部分Dを覆い、凹部の底面と下側の第2の部分においては前記絶縁膜が露出するように覆う、金属膜47を形成する。凹部の側壁面と底面とを連続的に覆う導電性拡散障壁膜48を形成する。銅を充填し銅配線パターン49A、49B、49Cとする。絶縁膜上と銅配線パターンの表面を覆う絶縁性拡散障壁膜49を形成する。熱処理により、銅配線パターンと絶縁性拡散障壁膜との界面に、金属元素の濃集領域49Dを形成する。金属元素の濃集領域では、金属膜を構成する金属元素の濃度が、銅配線パターン中よりも高い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】酸化処理や酸化剤への耐性を向上させ、かつビット線の低抵抗化を可能とする半導体装置及びその製造方法を提供する。

【解決手段】酸化処理により、第1ポリシリコン層14の側壁及び露出した基板10の底面に第3酸化膜17を形成する。次いで、ビット線16を、溝15の底面に形成し、溝15の側壁に第1窒化膜19を形成する。次いで、ビット線16上にのみ所望の厚さのタングステン層18を形成する。次いで、溝15を埋めるように第2窒化膜20を形成する。これにより、タングステン層18が第1窒化膜19及び第2窒化膜20で覆われることになり、この後に行われる熱処理や薬液処理からタングステン層18を保護することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】素子の微細化及び高集積化を妨げることなく、PN接合境界領域における金属シリサイド膜の断線を防止して、配線の高抵抗化を回避できるようにする。

【解決手段】半導体装置は、半導体基板10の上に形成され、導電性を有するシリコンからなるゲート電極と、該ゲート電極の上に形成されたニッケルシリサイド膜17とを有している。ゲート電極は、少なくとも、N型の導電性を示す第1のゲート電極14と、P型の導電性を示す第2のゲート電極15と、第1のゲート電極14及び第2のゲート電極15の間に形成された第3のゲート電極14aとを有している。第3のゲート電極14aは第1のゲート電極14と接続されると共に、第3のゲート電極14aの不純物の濃度は、第1のゲート電極14のN型不純物の濃度よりも低い。

(もっと読む)

81 - 100 / 242

[ Back to top ]