Fターム[5F038AV04]の内容

半導体集積回路 (75,215) | 可変インピーダンス (2,334) | 可変素子(自身のインピーダンスを使用) (1,002) | ダイオード (96)

Fターム[5F038AV04]に分類される特許

1 - 20 / 96

半導体装置

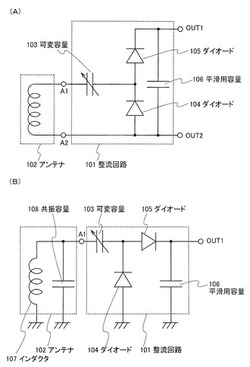

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

バンドギャップリファレンス回路

【課題】温度に対し高精度なリファレンス電圧の発生を実現する。

【解決手段】ダイオード接続されたトランジスタのベース−エミッタ間電圧を用いた、温度に対して負の特性を持つ電圧に、絶対温度に比例する正の特性を持つ電圧を加えて1次の温度補償を行うとともに、さらに前記トランジスタのベース−エミッタ間電圧に含まれる例えば2次の温度特性成分を打ち消す温度補償信号を発生するN次温度補償信号発生回路105を設け、ベース−エミッタ間電圧に、N次温度補償信号発生回路105からの温度補償信号Vcompを加えることにより、ベース−エミッタ間電圧に含まれる2次の温度特性成分による変動を抑制する。

(もっと読む)

半導体装置

【課題】半導体素子が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断できる半導体装置を提供すること。

【解決手段】半導体装置100を構成するパワー半導体素子を小さな半導体素子1に分割し、この小さな半導体素子1にそれぞれ1本のボンディングワイヤ17を接続する。小さな半導体素子1が短絡破壊したとき、破壊した小さな半導体素子1に接続するワイヤ17(ヒューズの役割をさせる)を溶断し、且つ、制御回路30からオフ信号を健全な半導体素子1に与える。このようにして、半導体装置100が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断することができる。

(もっと読む)

半導体装置

【課題】半導体装置の定格温度(−50℃〜+150℃)において高精度の温度検出を行うことのできる半導体装置を提供すること。

【解決手段】n型基板1の第1主面に、p型ベース領域3と該ベース領域3表面層のn型エミッタ領域4と、前記基板1からなるn型ドリフト層1表面と前記エミッタ領域4表面とに挟まれるp型ベース領域3表面上にゲート酸化膜7を介して設けられるゲート電極8と、前記エミッタ領域4表面と前記ベース領域3表面に共通に接触するエミッタ電極6と、第2主面のp型コレクタ層2とを有するIGBTと、該IGBTに離間して第1主面に形成されるn型ウェル領域15表面層にn型カソード領域11とp型アノード領域12を有する温度センサダイオードを備え、前記n型ウェル領域15がp型ウェル領域16の表面層に形成され、前記温度センサダイオードのライフタイムが1μs以下に設定されている半導体装置とする。

(もっと読む)

半導体集積回路装置の検査方法及び半導体集積回路装置

【課題】複数の集積回路層が厚さ方向に積層されて成る半導体集積回路装置の層間接続不良の有無を、一層積層する毎に短時間で検査することが可能な検査方法及び半導体集積回路装置を提供する。

【解決手段】互いに積層される集積回路層10及び20に、複数の検査用整流素子部15及び25をそれぞれ形成する。複数の検査用整流素子部15(25)は、複数の接続用端子14(24)のそれぞれと正電源配線13a(23a)及び接地配線13b(23b)との間に接続され、整流素子15a,15b(25a,25b)を含み電流により発光する。複数の接続用端子14及び24を互いに電気的に接続したのち、正電源配線13a(又は接地配線13b)と接地配線23b(又は正電源配線23a)との間にバイアス電圧を印加し、検査用整流素子部25の発光に基づいて、接続用端子14及び24の接続状態を検査する。

(もっと読む)

ダイオード回路

【課題】十分な逆方向耐圧を有し、順方向電圧が0Vに近い理想的なダイオード特性を有するダイオード回路を提供する。

【解決手段】アノード端子A及びカソード端子Kを有するアクティブダイオード100であって、ゲート端子111と、アノード端子A及びカソード端子Kの一方に接続されたドレイン端子112と、アノード端子A及びカソード端子Kの他方に接続されたソース端子113とを有するトランジスタ110と、トランジスタ110の閾値電圧に等しくなるように調整されたゲート電圧を、ゲート端子111に供給するゲート電圧発生回路120とを備える。

(もっと読む)

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】スタンバイ時における半導体装置の消費電力を低減する。

【解決手段】電源線VDDTL,VSSTL間に接続された回路ブロック10Aと、電源線VDDTL,VSSL間又は電源線VDDL,VSSTL間に接続された回路ブロック10Aの出力信号を受ける論理回路10B−1と、電源線VDDL,VSSL間に接続された論理回路10B−1の出力信号を受ける回路ブロック20と、を備える。電源線VDDTL,VSSTL間には、アクティブ状態においては第1の電圧、スタンバイ状態においては第1の電圧よりも低い第2の電圧が供給され、電源線VDDL,VSSL間には、アクティブ状態及びスタンバイ状態のいずれにおいても第1の電圧が供給される。これにより、サブシュレッショルド電流低減を維持しつつ、クリティカルパスの高速化を実現することが可能となる。

(もっと読む)

半導体集積回路装置

【課題】半導体プロセスを用いて、雰囲気温度から駆動電圧を得る半導体集積回路装置を提供する。

【解決手段】ダイオード接続された整流素子(トランジスタ3)と、一端が前記整流素子の一端に接続され、他端が接地電位に接続された電圧発生源としての抵抗素子(抵抗1)と、から構成される駆動電圧発生回路(単位セル31)から成り、前記抵抗素子(抵抗1)が発生する電圧を駆動電圧として前記整流素子(トランジスタ3)の他端に出力することを特徴とする半導体集積回路装置。

(もっと読む)

半導体駆動回路、及びそれを用いた半導体装置

【課題】ノーマリオフの接合型FETは閾値が低いため、ノーマリオフの接合型FETを用いた半導体駆動回路では高精度な電圧制御,高速な入力容量の充電,誤動作等の課題を有していた。

【解決手段】ツェナーダイオードによる高精度なゲート電圧生成方式やスピードアップコンデンサによるターンオン損失の低減,ゲート・ソース間のコンデンサの接続やソース端子の最適実装方式による誤動作の防止回路を適用することで、ノーマリオフの接合型FETに最良な半導体駆動回路を提案する。

(もっと読む)

半導体装置

【課題】半導体装置が形成された後においても、定常損失とスイッチング損失を調整することができる半導体装置を提供する。

【解決手段】第1導電型の第1半導体層、及び該第1半導体層における一方の主面側の表層に形成された少なくとも1つの第2導電型の第2半導体層を有する半導体基板と、第1半導体層における他方の主面に形成された第1電極と、第1半導体層における一方の主面に形成された第2電極と、を備え、第1電極と第2電極との間に電流が流れるダイオードを有する半導体装置であって、第1半導体層における一方の主面側に、第1半導体層に流入するキャリアの注入量を制御する制御信号を入力するための制御パッドと、該制御パッドと電気的に接続された制御電極と、該制御電極と第2電極、及び制御電極と半導体基板を絶縁する絶縁部材と、が形成されている。

(もっと読む)

電源システム

【課題】内部電源端子と外部電源端子を出力端子へつなぎ替えの際に電圧が不安定にならずにスムーズに電圧を切り替えることができる電源システムを得る。

【解決手段】P形半導体基板上にN型ウェルが設けられ、前記N型ウェル内にP型MOSFETから成る第1のスイッチ素子と第2のスイッチ素子が設けれたダイオードOR回路により内部電源端子と外部電源端子を出力端子へつなぎ替えて出力端子に電源電圧を供給する電源システムであって、前記N型ウェル内に一列に順番に、第1のスイッチ素子の第1のP型拡散層と、第1のゲート電極端子と、第2のP型拡散層と、前記N型ウェルの電位を供給するN型拡散層と、第2のスイッチ素子の第4のP型拡散層と、第2のゲート電極端子と、第3のP型拡散層の順に拡散層を配列し、前記第1のゲート電極端子と前記第2のゲート電極端子を前記N型ウェルの領域を横切るパターンに形成する。

(もっと読む)

パワースイッチング素子の温度検出装置

【課題】パワースイッチング素子Swの温度を感温ダイオードSDによって検出する際に、感温ダイオードSDに接続された電子機器の個体差等に起因して検出誤差が生じること。

【解決手段】感温ダイオードSDのカソードには、調節用抵抗体20を介して定電流源14の電流が入力される。感温ダイオードSDのアノード電圧は、調節用抵抗体20を介してPWMコンパレータ16に取り込まれる。PWMコンパレータ16は、感温ダイオードSDのアノード電圧とキャリアとの大小に基づき、感温ダイオードSDのアノード電圧に応じた時比率信号を生成して出力する。調節用抵抗体20は、感温ダイオードSDの搭載されるパワーカードPCに対して外付けされており、PWMコンパレータ16の出力信号を調節するために用いられる。

(もっと読む)

電界効果トランジスタ、及び電界効果トランジスタの製造方法

【課題】電界効果トランジスタの局所的な温度を測定することが可能な電界効果トランジスタを提供することである。

【解決手段】本発明にかかる電界効果トランジスタは、半導体層5と、半導体層5とオーミック接合したソース電極1と、半導体層5とオーミック接合したドレイン電極2と、半導体層5とショットキ接合したゲート電極3と、ソース電極1の一部に形成された空隙に設けられた、半導体層5とショットキ接合したショットキ電極4と、を有する。また、本発明にかかる他の態様の電界効果トランジスタは、半導体層5と、半導体層5とオーミック接合したソース電極1と、半導体層5とオーミック接合したドレイン電極2と、半導体層5とショットキ接合したゲート電極1と、ドレイン電極2の一部に形成された空隙に設けられた、半導体層5とショットキ接合したショットキ電極4と、を有する。

(もっと読む)

半導体装置

【課題】デジタル領域とアナログ領域とが混載された半導体装置におけるデジタル領域からアナログ領域へのノイズ伝搬を効果的に抑制する。

【解決手段】デジタル領域120とアナログ領域130とが混載された半導体装置100は、平面視でデジタル領域120およびアナログ領域130の外周を取り囲む環状のシールリング140と、シールリング140で囲まれた領域内で、デジタル領域120とアナログ領域130との間に設けられ、アナログ領域130をデジタル領域120から隔離するとともに、シールリング140に電気的に接続されたガードリング150と、ガードリング150と当該ガードリング近傍で電気的に接続された電極パッド160aとを含む。電極パッド160aは、外部の接地端子(180a)に接続されて接地電位とされている。

(もっと読む)

誤動作発生攻撃検出回路および集積回路

【課題】レーザ照射により、暗号回路やCPU等のセキュリティLSIの構成要素の回路で、誤動作が発生する前に、確実にレーザ照射を検知して、DFA,FIA攻撃を回避することが可能な誤動作発生攻撃検出回路および集積回路を提供する。

【解決手段】光の照射を検知可能な少なくとも1つのセンサ回路110Dと、センサ回路110の出力により中間電圧を検出し検出信号SFIAを出力する検出回路120Eと、を有し、センサ回路110Dは、出力ノードから所定レベルの信号を出力するように形成され、光照射によって変化する出力ノードのレベルに応じた信号を出力し、検出回路120Eは、センサ回路の出力信号レベルがあらかじめ設定したレベルに達すると検出信号を出力する。

(もっと読む)

高周波スイッチ回路

【課題】素子特性の変動による遮断特性の悪化を防止することのできる高周波スイッチ回路を提供する。

【解決手段】入出力端子Port1、Port2を有する高周波スイッチ回路11は、一端がPort2に接続されたn型MOSFET1の他端に、直列接続された可変容量キャパシタ2とインダクタ3とが、直列に接続され、インダクタ3の他端がPort1に接続されている。

(もっと読む)

半導体装置

【課題】還流ダイオードの導通時の損失並びに過渡動作時の損失は抑えつつ、逆回復動作時に生じる電流・電圧の振動現象を抑制することが容易に可能な電力用半導体装置を提供する。

【解決手段】ユニポーラ動作をする還流ダイオードと、キャパシタと抵抗との直列接続からなり、還流ダイオードに並列接続された半導体回路とを備え、半導体回路200は、抵抗220の少なくとも一部として機能する半導体基体11と、半導体基体の上面に接して設けられた容量低下防止領域1001と、容量低下防止領域1001上に設けられ、キャパシタ210の少なくとも一部として機能するキャパシタ誘電体膜12とを備え、容量低下防止領域1001が、還流ダイオードに逆バイアス電圧が印加された際に半導体基体11中への空乏層の伸張を緩和する。

(もっと読む)

パワー半導体装置の温度測定装置およびこれを使用したパワー半導体モジュール

【課題】製造コストを抑えながら、パワー素子が如何なる状態であっても、温度検出精度の低下を防止することができるパワー半導体装置の温度測定回路およびこれを使用したパワー半導体モジュールを提供する。

【解決手段】シリコンチップにパワー素子5,6と温度検出用ダイオードDD2,DU2とを設けたパワー半導体装置の温度を検出するパワー半導体装置の温度測定回路であって、前記温度検出用ダイオードDD2,DU2のアノードおよびカソードの電位を、前記パワー素子のエミッタ又はソース電位より、負電位に保った状態で、当該アノードおよびカソード間に流した順電流を検出して前記シリコンチップの温度を検出する温度測定部9,10を備えた。

(もっと読む)

電源回路及び光受信回路

【課題】光信号により起動制御が可能な電源回路及び光受信回路を提供する。

【解決手段】半導体基板の上に設けられ、光信号を電気信号に変換する起動回路と、前記半導体基板の上に設けられ、電源投入時に非起動状態であるバイアス回路と、を備え、前記起動回路は、p型半導体領域と、前記p型半導体領域と接して設けられたn型半導体領域と、を有し、前記p型半導体領域は、前記バイアス回路と電気的に接続され、前記n型半導体領域は、前記バイアス回路の電源と電気的に接続され、前記バイアス回路は、前記起動回路を流れる電流により起動状態となることを特徴とする電源回路が提供される。

(もっと読む)

1 - 20 / 96

[ Back to top ]