Fターム[5F038AZ07]の内容

Fターム[5F038AZ07]の下位に属するFターム

温度検知 (298)

Fターム[5F038AZ07]に分類される特許

1 - 20 / 115

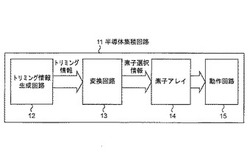

半導体集積回路およびそれを用いた光センサ機器

【課題】修正前の特性値がその特性値の出現頻度分布における平均値±2×(標準偏差)の範囲に入る製造品に対するヒューズ溶断本数を少なくする。

【解決手段】素子アレイ14には抵抗アレイを設け、特性値の分布の平均値を素子アレイ14で得られる合成抵抗値の中央値に対応付け、トリミング情報生成回路12における上記中央値より大きい合成抵抗値に対応するトリミング情報の配列を、10進数で「15」〜「8」の降順に、上記中央値以下の合成抵抗値に対応するトリミング情報の配列を、10進数で「0」〜「7」の昇順に設定する。変換回路13は、トリミング情報生成回路12からのトリミング情報を変換して、素子アレイ14の抵抗アレイから各合成抵抗値を得るためにオフする抵抗を選択する素子選択情報を生成する。こうして、上記分布における「平均値±2σ」の範囲内に対応付けられトリミング情報を生成する場合のヒューズ溶断数を大幅に削減する。

(もっと読む)

半導体装置

【課題】電磁適合性(EMC)の問題を改善することができる半導体装置を提供する。

【解決手段】第1主面と第2主面とを有する半導体基板10と、第1主面上に形成され、入射光を電気信号に変換するセンサ部31と、第1主面上に形成されたロジック回路12と、センサ部31及びロジック回路12上に形成され、電磁波を遮断するシールド層14と、第2主面上に配置されたカラーフィルタ37と、カラーフィルタ37上に配置されたマイクロフィルタ38とを有する。

(もっと読む)

半導体集積回路及びその設計方法

【課題】チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

半導体集積回路、電子機器及びマルチチップ半導体パッケージ

【課題】比較的簡単な構成でありながらも動的で高分解能の電圧制御可能な半導体集積回路、電子機器及びマルチチップ半導体パッケージを提供すること。

【解決手段】電子機器100は、電源IC110と、電源IC110から出力される電源電圧Vsrcで動作するSoC#0〜2とを備える。SoC#0〜2は、三次元実装されたマルチチップ半導体パッケージに搭載される。SoC#0〜2は、第3の端子123から入力されるアナログ制御信号の電位と、内部配線124の電位とに基づいて、第2の端子122から出力するアナログ制御信号を生成する電位制御回路125と、電源フィードバック(FB)電圧入力端子である第2の端子122及び第3の端子123と、を備える。SoC#0〜2は、FB出力端子FB_out/FB入力端子FB_inをカスケード接続し、最終段のSoC#0のFB出力を電源IC110に接続している。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

低フラックス及び低ノイズの検出回路

【課題】低フラックスを用いている間のノイズレベルを減少することを可能にするような検出回路を提供する。

【解決手段】ソースフォロワ検出器型の検出回路は、結合ノードNに接続されたフォトダイオード1を備える。バイアス回路3は、逆バイアスである第1の状態とフローティングである第2の状態との間にフォトダイオード1をバイアスすることを可能にする。読み出し回路4は、結合ノードNに接続され、フォトダイオード1により測定された現状を示す信号を生成する。金属シールド5は結合ノードNの周りに配置される。金属シールド5は、読み出し回路4の出力に接続され、結合ノードNの電位と同じ方向に変動する電位を持つように構成される。

(もっと読む)

半導体装置とその動作方法

【課題】半導体装置において、消費電力を低減する。また、スタンバイ回路を少ない素子で構成し、半導体装置の回路面積の増大を防ぐ。

【解決手段】半導体装置に備えるスタンバイ回路をトランジスタ一つのみで構成し、該トランジスタに供給する電圧を切り替えることで、半導体装置の出力電流を制御する。これにより、スタンバイ状態での半導体装置の出力電流をほぼゼロにすることができるため、消費電力の低減が可能になる。なお、トランジスタの半導体層に酸化物半導体を用いることで、リーク電流を極小に抑えることができる。

(もっと読む)

半導体装置及びその試験方法

【課題】半導体チップに部分的に大きな電流が流れるのを抑制する技術を提供することを目的とする。

【解決手段】半導体装置は、ゲート電極5を有する半導体チップ1と、半導体チップ1の表面に設けられ、当該表面にかかる応力を検出する応力検出用素子7とを備える。そして、半導体装置は、応力検出用素子7で検出された応力に基づいて、ゲート電極5に印加される制御信号を制御する。また、平面視において半導体チップ1の中央部にかかる応力を検出する応力検出用素子7が、第1応力検出用素子7−1として設けられ、平面視において半導体チップ1の外周部にかかる応力を検出する応力検出用素子7が、第2応力検出用素子7−2として設けられることが好ましい。

(もっと読む)

赤外線センサー及び赤外線アレイセンサー

【課題】周囲温度が変化した場合でも、ペルチェ素子等の電気的な冷却素子を使用することなく、熱型赤外線センサーの出力電圧のDCレベル変化を小さくする。

【解決手段】電源VddとグランドGNDの間にセンサーMOSFET3と電流源MOSFET5が直列に接続されている。センサーMOSFET3は断熱構造体1上に配置され、電流源MOSFET5は断熱構造体1の外部に配置されている。センサーMOSFET3及び電流源MOSFET5は同じ導電型のMOSFETからなり、かつサブスレッショルド領域で動作される。センサーMOSFET3と電流源MOSFET5の間の端子がセンサー出力端子Voutを構成する。センサーMOSFET3及び電流源MOSFET5は周囲温度変化に対して特性がほぼ等しく変化する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線層の層間における剥離の有無を簡便な手法で検出できるようにする。

【解決手段】第1電極412は多層配線層20に形成されている。第2電極422は、絶縁膜22の一部を介して第1電極412と対向している。第1電極パッド430は第1電極412に接続している。第2電極パッド432は第2電極422に接続している。そして少なくとも2層以上の絶縁膜22のそれぞれが、第1電極412及び第2電極422に挟まれている。そして第1電極412及び第2電極422により、センサ40の少なくとも一部が形成されている。センサ40は、多層配線層20の層間における剥離の有無を検出するために用いられる。

(もっと読む)

半導体集積回路装置

【課題】デジタル回路からアナログ回路へのノイズの混入を十分に抑圧する半導体集積回路装置を提供することを目的とする。

【解決手段】デジタル回路を形成するデジタル回路領域13と、アナログ回路を形成するアナログ回路領域12とに分離し、アナログ回路領域を、アナログ回路の能動素子を形成する能動素子領域12aと、アナログ回路の受動素子を形成する受動素子領域12b,12cとに分離し、受動素子領域12b,12cをデジタル回路領域13と隣り合う領域に配置し、能動素子領域12aをデジタル回路領域13から離れた領域に配置した半導体集積回路装置において、受動素子領域12b,12cの半導体基板20に半導体基板の導電型と異なる第1導電型の第1ウェル21を形成し、第1ウェル21内に第1ウェルの第1導電型と異なる第2導電型の第2ウェル22を形成し、第2ウェル22上に素子分離膜23を介在させて受動素子を配設した。

(もっと読む)

集積回路および測定装置

【課題】集積回路自体の構成を変更することなく、回路動作を容易に変更することができる集積回路を提供する。

【解決手段】本発明の集積回路は、外部センサ200からの信号を処理する集積回路であって、互いに異なる入力端子部101,103に入力された信号を処理して互いに異なる出力端子部102,104に出力する複数の処理回路110,120を有し、前記集積回路に選択的に接続される外部センサ200の種類に応じて前記入力端子部と前記出力端子部との間の外部接続状況を変更することによって、前記複数の処理回路のうちで、前記外部センサからの信号を初めに受信する初段の処理回路と次段以降の処理回路との順番を切り替える。

(もっと読む)

温度センサと、半導体装置およびその較正方法

【課題】出力電圧の温度依存性を示す曲線の曲率が小さく、レイアウト面積が小さな温度センサを提供する。

【解決手段】この温度センサは、アノードがノードN1に接続されたダイオードD0と、アノードが抵抗素子8を介してノードN2に接続されたダイオードD1〜Dnと、ノードN1,N2の電圧を一致させる演算増幅器1と、抵抗素子9,10を介してノードN1,N2に接続され、抵抗素子9,10に流れる電流を調整し、温度センサの出力電圧VOの温度依存性を示す曲線の曲率を小さくする電圧調整回路12を備える。したがって、2つのサブ温度センサを設ける従来に比べ、レイアウト面積が小さくて済む。

(もっと読む)

システムインパッケージ

【課題】外付け機器用に別途端子を設けたりテスト端子を別途設けたりすることなく、マイクロコンピュータおよび周辺素子がパッケージに内蔵され互いに電気的に接続されたとしてもデバッグツールを外部接続することができ外部からデバッグできるようにする。

【解決手段】代替パルス発生制御部7eはデバッグするときにパルス発生素子3のパルス信号に代えて代替パルス信号を発生し、切替部8はパルス発生素子3のパルス信号と代替パルス発生制御部7eの代替パルス信号とを切替え、デバッグするときに代替パルス信号に切替えて出力し、各機能部4〜6が代替パルス信号に応じて動作し、外部接続されたデバッグツール9によってデバッグできる。

(もっと読む)

半導体装置

【課題】半導体装置の小型化を図ることを課題とする。

【解決手段】炭化珪素基体1と、炭化珪素基体1上に形成された第1導電型のドリフト領域2と、ドリフト領域2の主面に接するようにドリフト領域2内に形成された第2導電型のウェル領域3と、ドリフト領域2の主面に接するようにウェル領域3内に形成された第1導電型のソース領域4と、ドリフト領域2とソース領域4に挟まれたウェル領域3上にゲート絶縁膜5を介して形成されたゲート電極6と、ウェル領域3とソース領域4に接続されたソース電極7と、炭化珪素基体1に接続されたドレイン電極9とを備えたトランジスタと、ドリフト領域2に形成された第2導電型の拡散領域10からなるアノードと、第2導電型の拡散領域10内に形成された第1導電型の拡散領域11からなるカソードとを備え、カソードはゲート電極6に接続されて構成されたダイオード12とを有することを特徴とする。

(もっと読む)

イメージセンサ用IC及びそれを用いた密着型イメージセンサ

【課題】 センサチップを所定のピッチで配列しても仮想画素が生じない高密度対応のイメージセンサ用IC及びそれを用いた密着型イメージセンサを提供する。

【解決手段】 対辺が平行な四角形の半導体基板の表面に互いに隣接して直線的に配置され、半導体基板の対向する一方の辺の所定位置から他方の辺の所定位置まで少なくとも一組の対辺に対して傾斜させて設置した受光素子10aと、直線的に配置された受光素子10aと一組の対辺とで成す角度が広角となる領域側の一組の対辺一端部又は両端部に設けられ、直線的に配置された受光素子10aと傾斜角度があると共に直線的に配置された受光素子10aの外側に光を受光する補間素子10bとを備えるようにした。

(もっと読む)

半導体集積回路及びデータ処理システム

【課題】意図的に誤動作を生じさせるための局所的な光照射を検出するための構成を小さなチップ占有面積で実現し、検出感度を高くする。

【解決手段】ロジック回路(6)が形成された領域に分散され初段の入力が一定論理値にされて直列的に接続された複数個の検出インバータ(100)を検出素子として採用し、単数又は複数のインバータに光が照射されて各々に出力が反転することによって直列的に接続された複数個の検出インバータの最終出力が判定され、これにより局所的な光照射を検出することができる。

(もっと読む)

半導体装置

【課題】 パッケージに封止される半導体素子は、使用環境によって湿度の影響を受けて、半導体素子の劣化が起こることがある。パッケージに実装することが容易で、半導体素子周囲の湿度・水分量を測定・記録できる湿度センサを得る。

【解決手段】 半導体基板2上に形成した絶縁膜7の上に、水溶性金属の薄膜8を用いた湿度センサ6を形成し、水溶性金属の薄膜8の抵抗を測定する。水溶性金属とは、電位−pH図において、電位がゼロ、pHが7付近で腐食域にある金属を意味する。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】高性能なフレキシブル半導体装置を提供すること。

【解決手段】可撓性を有するフレキシブル半導体装置であって、絶縁膜と、かかる絶縁膜の下面に位置する金属箔をエッチングすることによって形成されたソース電極およびドレイン電極と、絶縁膜の上面の一部に形成された半導体層と、ソース電極およびドレイン電極のそれぞれと、前記半導体層とを電気的に接続する取出し電極パターンと、取出し電極パターンおよび半導体層を封止する封止樹脂層と、封止樹脂層の面のうちソース電極およびドレイン電極が形成された面とは反対側の面に形成されたゲート電極とを備えたフレキシブル半導体装置。

(もっと読む)

1 - 20 / 115

[ Back to top ]