Fターム[5F038BG04]の内容

Fターム[5F038BG04]に分類される特許

1 - 20 / 104

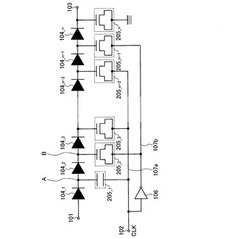

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

半導体装置

【課題】低電圧で動作するとともに高電圧が入力された場合でも破壊することがないチャージポンプ回路を備えているとともに、通常の量産用の半導体製造プロセスが適用可能な半導体装置を提供する。

【解決手段】半導体装置において、チャージポンプ回路30は、薄膜トランジスタで構成され、外部電源電圧を昇圧する。スイッチ制御部11は、外部電源電圧が基準電圧を超えている場合には、チャージポンプ回路30への外部電源電圧の供給が遮断されるようにするとともに外部電源電圧がチャージポンプ回路30を介さずに負荷回路50に直接供給されるようにする。基板電圧制御部14は、外部電源電圧が基準電圧以下の場合に、チャージポンプ回路30を構成するトランジスタの基板領域に順方向となるバイアス電圧を供給する。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

シンクロナス整流器或いは電圧クランプ用の3端子パワーMOSFETスイッチ

【課題】パワー変換器に於けるシンクロナス整流器として適するMOSFETスイッチを提供する。

【解決手段】互いに接続されソース及びボディが、ドレンよりはより正の側に高い電圧にバイアスされたN−チャネルパワーMOSFETを製造する。ゲートはスイッチ(1184)により制御され、ゲートを、ソース及び当該MOSFETのチャネルを完全にオンにするのに十分な電圧(VCP)のいずれか一方に選択的に接続する。ゲートがソースに接続されたとき、デバイスは、比較的低い電圧でオンし、従来のPN接合よりは低い導通抵抗を有する「擬似ショットキー」ダイオードとして機能する。ゲートが、前記した正の電圧に接続されたとき、MOSFETのチャネルは完全にオンとなる。このMOSFETスイッチは、電力損及び“break-before-make”時間に於ける蓄積電荷を低減する。

(もっと読む)

半導体装置

【課題】同期整流方式のDCDC変換装置において、短絡防止期間中に、同期整流用FETのドレインが負電圧となると、基板−ドレインの間に電流が流れ、基板の電位が揺すられる。同期整流用FETを内蔵した素子の場合、この基板の電位の揺れは制御回路の誤動作を招く。

【解決手段】P型基板とバックゲートとが分離されたNチャネルMOSFETを2段縦積みにした構造を有する複合素子を、同期整流用FETとして用い、複合素子の上段側FETを、メイン側FETがオフかつ下段側FETがオフとなる短絡防止期間において、オフとする。

(もっと読む)

半導体装置

【課題】通信距離が極端に短い場合においても正常に動作し、且つ通信距離が長い場合においては、保護回路での消費電力を抑え、信頼性の高い半導体装置(RFID)を提供する。

【解決手段】無線によりデータの交信が可能な半導体装置(RFID)を構成する素子を保護するための保護回路107を設けることに特徴を有する。そして、整流回路102において生成された直流電源電位が所定の値(基準値)以上となるときに保護回路107が動作するようにし、生成される直流電源電位の値を小さくする。一方、整流回路102において生成された直流電源電位が所定の値(基準値)以下となるときは、保護回路107が動作しないようにし、生成された直流電源電位の値をそのまま用いる。また、保護回路107のトランジスタ201,202は、酸化物半導体層により構成されており、トランジスタ201,202のオフ電流を下げ、保護回路107での消費電力を抑える。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】ゲートリセスの深さの制御を安定的に行なえるようにして、ノーマリオフ動作のデバイスを安定的に作製できるようにする。

【解決手段】半導体装置を、基板1の上方に設けられたGaN電子走行層2と、GaN電子走行層2上に設けられた第1AlGaN電子供給層3と、第1AlGaN電子供給層3上に設けられたAlN電子供給層4と、AlN電子供給層4上に設けられた第2AlGaN電子供給層5と、第2AlGaN電子供給層5及びAlN電子供給層4に設けられたゲートリセス9と、ゲートリセス9に設けられたゲート電極12とを備えるものとする。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】トランジスタが有するしきい値相当分の電圧/電流のロスを低減し、プロセスの簡略化、及び回路構成の簡素化を目的とした整流特性を有する半導体装置(RFID)を提供する。

【解決手段】無線によりデータの交信が可能な半導体装置(RFID)を構成する素子に整流回路を設ける。整流回路において、電波を受信するアンテナと整流回路のトランジスタのゲートとドレイン端子との間に、コイルを重ねて配置することで、電波を受信するアンテナとコイルの結合を利用して、ダイオード単体と比較しダイオードとコイルが出力する電圧を大きくし、整流効率を向上させる。

(もっと読む)

集積回路およびウェーハを試験する無線周波数技術構造および方法

【課題】集積回路を有するウェーハの無線試験を行うためのウェーハ上に形成された試験回路を含む装置および方法を提供する。

【解決手段】ウェーハ16の外部にある試験ユニット12、および集積回路を含むウェーハ上に製造された少なくとも1つの試験回路14を含む。試験ユニット12は、RF信号を送信し、試験回路14に電力を供給する。試験回路14は、可変リング発振器を含み、集積回路の公称動作周波数での一連のパラメータ試験を実行し、試験結果を分析のために試験ユニット12に送信する。

(もっと読む)

半導体装置

【課題】接触動作時において非接触端子からのアクセスがあった場合においても安定した内部電源を生成する。

【解決手段】半導体装置(U2)は、外部から電源端子(VCC)に与えられる電圧に基づいて第1の電源ライン(VDD)に直流電圧を得る第1の電源回路(B3)と、アンテナ(L0)からアンテナ端子(LA、LB)に与えられる交流信号を整流する整流回路(B4)と、整流された電圧に基づいて前記第1の電源ラインに直流電圧を得る第2の電源回路(B5)とを有し、前記電源端子に電圧が与えられたとき、前記整流回路は整流動作を停止する。

(もっと読む)

半導体昇圧回路

【課題】チャージポンピング方式の昇圧回路において、ポンピング容量駆動回路に起因した昇圧電位におけるノイズを低減する。

【解決手段】ポンピング容量駆動回路を、プッシュプル動作する第1の回路と第2の回路で構成する。第1の回路と第2の回路は、各々の動作点をバイアス電位で調整するように構成し、不感帯領域を持つように適切なバイアス電位に調整する。不感帯領域により、従来のインバータ駆動で生じていたオーバーシュート、アンダーシュートが軽減され、昇圧回路の昇圧電位におけるノイズが低減できる。

(もっと読む)

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】主面をm面とするIII 族窒化物半導体で構成されたHFETにおいて、正のしきい値電圧を高めること。

【解決手段】HFET100は、凹凸加工されたa面サファイア基板101上に、m面を主面とするGaNからなるバッファ層102、ノンドープのGaNからなるチャネル層103、ノンドープのAlGaNからなる障壁層104、酸素ドープのn−AlGaNからなるキャリア供給層105を有している。キャリア供給層105は2つの領域に分離して形成されている。キャリア供給層105は、障壁層104上に選択的に再成長させて形成した層である。ゲート電極109にバイアスを印加しない状態では、ゲート電極109直下に2DEGが形成されないため、正のしきい値電圧を高めることができる。

(もっと読む)

半導体装置

【課題】素子が破壊されるほど高い電圧が印加された場合であっても、素子の破壊を抑制する。

【解決手段】第1の電圧が入力されることにより動作を行う半導体装置であって、第1の電圧の絶対値が基準値より大きいとき、第1の電圧の値を変化させる保護回路を具備し、保護回路は、第1の電圧に応じて第2の電圧を生成し、生成した第2の電圧を出力する制御信号生成回路と、電圧制御回路と、を備え、電圧制御回路は、ソース、ドレイン、及びゲートを有し、ゲートに制御信号として第2の電圧が入力され、第2の電圧に応じてオン状態又はオフ状態になることにより、第1の電圧の値をソース及びドレインの間に流れる電流量に応じて変化させるか否かを制御するトランジスタを含み、トランジスタは、チャネル形成層としての機能を有する酸化物半導体層をさらに有し、酸化物半導体層のバンドギャップは、2eV以上である。

(もっと読む)

直流変換回路及び電源回路

【課題】高い信頼性を有する直流変換回路を提供する。

【解決手段】流れる電流の変化に応じて起電力が発生する誘導素子と、ゲート、ソース、及びドレインを有し、オン状態又はオフ状態になることにより、誘導素子における起電力の発生を制御するトランジスタと、トランジスタがオフ状態のときに導通状態になる整流素子と、トランジスタのオン状態又はオフ状態を制御する制御回路と、を具備し、トランジスタは、チャネル形成層として水素濃度が5×1019atoms/cm3以下である酸化物半導体層を有する構成とする。

(もっと読む)

半導体集積回路装置

【課題】半導体プロセスを用いて、雰囲気温度から駆動電圧を得る半導体集積回路装置を提供する。

【解決手段】ダイオード接続された整流素子(トランジスタ3)と、一端が前記整流素子の一端に接続され、他端が接地電位に接続された電圧発生源としての抵抗素子(抵抗1)と、から構成される駆動電圧発生回路(単位セル31)から成り、前記抵抗素子(抵抗1)が発生する電圧を駆動電圧として前記整流素子(トランジスタ3)の他端に出力することを特徴とする半導体集積回路装置。

(もっと読む)

半導体装置およびDC−DCコンバータ

【課題】電力変換効率をより向上させる半導体装置を提供する。

【解決手段】第1のゲート配線に接続する第1のゲート電極および第1の閾値電圧を有する第1のスイッチング素子と、前記第1の閾値電圧よりも絶対値が大きい第2の閾値電圧を有し、第1のゲート配線の単位長さあたりの抵抗よりも大きい抵抗を有する第2のゲート配線に接続する第2のゲート電極を有する第2のスイッチング素子と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置

【課題】半導体装置の歩留まりを向上させること若しくは製造コストを低減すること又は集積回路の面積を低減する半導体装置を提供する。

【解決手段】半導体装置が有するメモリ素子10のメモリ層12及び抵抗素子20の抵抗層22が同一材料によって構成される。そのため、メモリ層12と、抵抗層22とを同一工程によって形成することで、半導体装置の作製工程数を低減することができる。結果として、半導体装置の歩留まりを向上させること又は製造コストを低減することができる。また、半導体装置は、抵抗値の高い抵抗成分を備えた抵抗素子20を有する。そのため、半導体装置が有する集積回路の面積を低減することができる。

(もっと読む)

半導体装置

【課題】バイポーラの高耐圧縦型PNPプロセスをベースに高耐圧、低オン抵抗特性のダイオードで直列ダイオード群を形成する。係る直列ダイオード群を2つ並列接続しブリッジを形成し寄生トランジスタ等によるリーク電流の無い高効率な全波整流回路を構築する。

【解決手段】P型半導体基板1をアノード、N型埋め込み層2をカソードとするダイオードと、P+型導電層8をアノード、N型エピタキシャル層5をカソードとするダイオードを電極AC1で直列接続し直列ダイオード群を形成する。この場合、N+型埋め込み層3及びN+型導電層7を形成し、電極AC1に大きな正電圧が印加された場合にもP+型埋め込み層4の電位よりN+型埋め込み層3の電位が低下するのを防止し、P+型埋め込み層4、N+型埋め込み層3、P型半導体基板1をそれぞれエミッタ、ベース、コレクタとする寄生PNPトランジスタがオンするのを防止する。

(もっと読む)

1 - 20 / 104

[ Back to top ]