Fターム[5F038BG05]の内容

Fターム[5F038BG05]に分類される特許

1 - 20 / 292

半導体集積回路

半導体装置

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

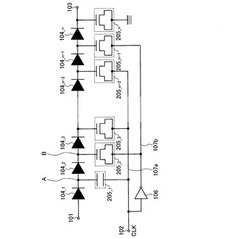

チャージポンプ回路およびそれを用いた半導体装置

【課題】起動時の消費電流を小さく抑制できるチャージポンプ回路を提供する。

【解決手段】このチャージポンプ回路30では、ポンプ回路10の起動期間は分周クロック信号CLKDをポンプ回路10に与えてポンプ回路10の電流供給能力を低く設定し、起動期間の終了後はクロック信号CLKをポンプ回路10に与えてポンプ回路10の電流供給能力を高く設定する。したがって、起動期間はポンプ回路10の消費電流を小さく抑制し、起動期間の終了後はポンプ回路10の電流供給能力を高めることができる。

(もっと読む)

トレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法

【課題】製造コストの増加を抑制し、キャパシタの端部の段差を小さくできるトレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法を提供することにある。

【解決手段】トレンチ52内壁に分離絶縁層53を配置し、この分離絶縁層53を介して下部電極となる第1ポリシリコン54を埋め込んだトレンチ型PIPキャパシタ50を半導体基板に形成することで、キャパシタの端部に形成される段差を低減できる。その結果、配線となるメタル層59を過度に厚くする必要がなく、メタル層59を微細化することができる。その結果、パワーICを微細化することができる。

(もっと読む)

チャージポンプ及びこれを用いた電源装置

【課題】プリント配線基板上の実装面積削減やコスト削減を実現することのできるチャージポンプを提供する。

【解決手段】チャージポンプ100は、フライングキャパシタ120の充放電用スイッチとして、半導体装置110に集積化されたフローティングNMOSFET111及び112のボディダイオード111d及び112dを用いる。

(もっと読む)

半導体集積回路及びその制御方法

【課題】デカップリング容量素子の信頼性と、フラッシュメモリの動作モードに対応した供給電流の補償を損なわずに、フラッシュメモリの面積増加を抑制する。

【解決手段】本発明に係る半導体集積回路10は、フラッシュメモリ部12と、フラッシュメモリ部12に電圧を供給する昇圧回路13と、昇圧回路13の出力に一端が接続されたデカップリング容量素子15と、フラッシュメモリ部12の動作モードに応じて、デカップリング容量素子15の他端の電位を制御する制御回路14とを備える。

(もっと読む)

半導体装置及びこれを備える情報処理装置

【課題】安定したチャージポンプ動作を行う。

【解決手段】ノードA,Bを有するコンデンサC1と、VDDレベルからVSSレベルの間で振幅するポンピング信号PUMP1をコンデンサC1のノードAに供給するポンピング回路110と、コンデンサC1のノードBをVPPextレベルにプリチャージし、ポンピング信号PUMP1がVSSレベルからVDDレベルに変わった時に、コンデンサC1のノードBをVPPextレベルよりも高いレベルに駆動する出力回路120とを備える。本発明によれば、コンデンサC1のノードAをポンピングするための電圧と、コンデンサC1のノードBをプリチャージするための電圧が異なっていることから、昇圧電圧を効率よく生成することできる。

(もっと読む)

昇圧回路

【課題】損失を抑制すると共により迅速に昇圧を行なう。

【解決手段】チャージポンプ20からの出力電圧VCがトリガ電圧を超えると、スイッチ70がオンし、クロック信号供給回路30は出力電圧VCの振幅のクロック信号CKmos,CKBmosをチャージポンプ20に出力し、クロック信号供給回路40は出力電圧VCの振幅のクロック信号CKmosを用いてクロック信号CKcap,CKBcapを生成してチャージポンプ20に出力し、チャージポンプ20では、各トランジスタのゲートへ出力電圧VCの振幅のクロック信号CKmos,CKBmosが供給され、各キャパシタの他端へ立ち上がり時間の小さいクロック信号CKcap,CKBcapが供給される。これにより、昇圧回路10全体の損失を抑制すると共により迅速に出力電圧VCを目標出力電圧に昇圧することができる。

(もっと読む)

チャージポンプ回路およびその制御回路、オーディオ信号処理回路、電子機器

【課題】昇圧率の切りかえの際に、電流の逆流を防止する。

【解決手段】コントローラ10は、第1スイッチSW1から第7スイッチSW7のオン、オフ状態を制御することにより、(1)第1モードにおいて、第3端子P3に入力電圧VDDを、第4端子P4に入力電圧VDDを反転した負電圧−VDDを発生させ、(2)第2モードにおいて、第3端子P3に入力電圧VDDの略1/2倍の電圧を、第4端子P4に、入力電圧VDDの略1/2倍の電圧を反転した負電圧−VDD/2を発生させる。コントローラ10は、第1モードから第2モードへの移行を指示されると、遷移期間にわたり、第3スイッチおよび第5スイッチをオンする第1状態と、第2スイッチおよび第4スイッチをオンする第2状態と、を交互に繰り返す第3モードで動作し、その後、第2モードで動作する。

(もっと読む)

半導体装置

【課題】低電圧で動作するとともに高電圧が入力された場合でも破壊することがないチャージポンプ回路を備えているとともに、通常の量産用の半導体製造プロセスが適用可能な半導体装置を提供する。

【解決手段】半導体装置において、チャージポンプ回路30は、薄膜トランジスタで構成され、外部電源電圧を昇圧する。スイッチ制御部11は、外部電源電圧が基準電圧を超えている場合には、チャージポンプ回路30への外部電源電圧の供給が遮断されるようにするとともに外部電源電圧がチャージポンプ回路30を介さずに負荷回路50に直接供給されるようにする。基板電圧制御部14は、外部電源電圧が基準電圧以下の場合に、チャージポンプ回路30を構成するトランジスタの基板領域に順方向となるバイアス電圧を供給する。

(もっと読む)

昇圧回路

【課題】負荷電流に応じて昇圧能力を調整することにより、過剰な昇圧回路出力リップルを抑制する。

【解決手段】昇圧回路1は、昇圧部出力CPOの電圧を変動させて昇圧回路出力VPPを生成し、昇圧回路出力VPPの負荷電流の大きさに応じて制御電圧CON1を生成する制御部2と、制御電圧CON1に応じて電源VDDP1の電圧を変動させることにより昇圧部電源VDDPを生成する電源降圧部3と、昇圧回路出力VPPの電圧と目標電圧との差分に応じて昇圧部電源VDDPの電圧を変動させることにより昇圧部出力CPOを生成する昇圧部4とを備える。

(もっと読む)

半導体装置

【課題】出力端子に接続される内部回路の動作開始を早く行うことができる定電圧発生回路を備えた半導体装置を提供する。

【解決手段】クロック信号VOSCが入力されると、内部の複数のノードにおいてポンピング動作を行い、入力端子に供給される電荷を複数のノードを介して出力端子へと順次転送し、出力端子から出力電圧を発生する昇圧回路20と、出力電圧が予め設定された電圧に達した場合、非活性レベルの検知信号VUPTを出力する電圧検出回路30と、検知信号が活性レベルの場合、クロック信号を昇圧回路へ出力し、検知信号が非活性レベルの場合、クロック信号の昇圧回路への出力を停止するクロック信号制御回路40と、を備え、クロック信号制御回路は、検知信号が非活性レベルであっても、入力される制御信号RESETTのレベルに応じてクロック信号を昇圧回路へ出力する。

(もっと読む)

電源逆接保護装置

【課題】簡素な回路構成により、誘導成分を含む負荷への通電を制御する場合においても、電源逆接保護用半導体素子のゲート破壊を招く虞のない信頼性の高い電源逆接保護装置を提供する。

【解決手段】直流電源10と、グロープラグ18への通電を制御する通電制御用半導体素子14と、過電流保護回路161とグロープラグ18と電源10、及び/又は、通電制御用半導体素子14とを繋ぐ配線17の寄生インダクタンスLを誘導成分として含み、電源逆接保護用半導体素子11として、P-チャンネルパワーMOSFETを通電制御用半導体素子14の上流側に配設すると共に、所定の抵抗値RGを有するゲート抵抗13を介して、P-チャンネルパワーMOSFET11のゲートG11を接地せしめる。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

半導体装置

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

半導体装置および半導体装置の測定方法

【課題】半導体ウエハ上の半導体チップのアナログ特性の測定を精度良く行えるようにする。

【解決手段】半導体チップ1の被測定部3は半導体素子3a、回路3bである。被測定部3のアナログ特性を測定する測定回路4を設けている。測定回路4は、外部電源からプローブ針Pa、Pbを介して給電され、内部で測定用印加電圧を生成し、配線パターン5を介して被測定部3に印加する。測定回路4は、被測定部3の出力を配線パターン5から入力し、デジタルデータに変換する。測定回路4と配線パターン7を介して半導体チップ2の不揮発性メモリ6に接続され、デジタルデータが転送記憶される。一連の測定が終了した後に、不揮発性メモリ6からデジタルデータを取り出す。プローブ針の接触抵抗や浮遊容量の影響を低減して精度良いアナログ特性の測定ができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積を削減することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施形態に係る不揮発性半導体記憶装置は、半導体基板と、半導体基板上に積層され、垂直方向に直列接続された複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられ、所望の電圧をメモリセルアレイに供給する電源回路とを備える。電源回路は、電圧を生成するポンプ回路と、ポンプ回路の出力端子に接続され、出力端子の電圧値が所定の値を下回った場合にポンプ回路へ制御信号を出力するリミッタ回路と、出力端子に一端が接続され、出力端子の電圧を調整するように構成されたキャパシタと、キャパシタの他端に接続され、制御信号に基づき所定の電流値の定電流を用いてキャパシタを充電するブースト回路と、ブースト回路の充電動作を停止させるスイッチとを備える。キャパシタは、メモリセルアレイの直下に設けられる。

(もっと読む)

半導体集積回路

【課題】電荷転送効率が高い転送トランジスタを備える半導体集積回路を提供することを目的とする。

【解決手段】実施形態に係る半導体集積回路は、ゲート電極を有し、当該ゲート電極及び一の拡散層が第1配線でダイオード接続された転送トランジスタと、クロック信号が供給されるクロック信号線とを備え、前記クロック信号線の一部である第1部分クロック信号線の少なくとも一部が前記ゲート電極上に形成されていることを特徴とする。

(もっと読む)

1 - 20 / 292

[ Back to top ]