Fターム[5F038BH19]の内容

Fターム[5F038BH19]に分類される特許

201 - 220 / 1,289

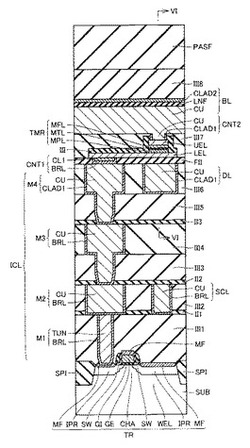

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体装置およびその制御方法

【課題】電源遮断・復帰時に動作中の回路の誤動作を抑止しつつ、デバイスの製造ばらつきに応じて最適な速度での電源制御領域の電源遮断・復帰を可能とする半導体装置の制御技術を提供する。

【解決手段】半導体装置において、通常動作領域10と、電源制御領域20と、電源制御領域20に接続され、電源制御領域20への電源を供給または遮断する複数の電源スイッチSWとを有し、さらに、複数の電源スイッチSWのオンオフを制御し、半導体装置毎の製造後の性能に応じて電源遮断・復帰の遷移時間を変更し、電源遮断・復帰を行うスイッチ制御回路30を有する。さらに、半導体装置毎の製造後の性能を記録する記憶素子40を有する。

(もっと読む)

昇圧回路、昇圧装置及び半導体集積回路

【課題】電源ノイズ及び接地ノイズを低減することができる昇圧回路を提供すること。

【解決手段】本発明は、MOS容量C1、駆動回路10及びトランジスタ3を備える。MOS容量C1のゲートは出力端子VOUTと接続され、正の電荷が蓄積される。駆動回路10は、入力信号に応じて、MOS容量C1の一端に電源電圧VCCを出力し、又はMOS容量C1の他端にグランド電圧GNDを出力する。トランジスタ3は、出力端子VOUTと電源電圧VCCとの間に接続される。駆動回路10がMOS容量C1に電源電圧VCCを出力する場合は、トランジスタ3はOFFとなる。一方、駆動回路10がMOS容量C1にグランド電圧GNDを出力する場合は、トランジスタ3はONとなる。

(もっと読む)

半導体装置、半導体ウエハおよびその電源制御方法

【課題】電源供給構造を備えた半導体装置において、外部測定装置のコストの増大を招くことなく、電源回路を正確に制御することが困難である。

【解決手段】本発明の半導体装置は、主回路部と、電源配線部と、無線信号を受信し制御信号を出力する無線回路部と、電源配線部と主回路部に接続され、無線回路部からの制御信号に基づき、主回路部への電源供給状態を制御する第一の電源回路部と、電源配線部と無線回路部に接続され、無線回路部への電源供給状態を制御する第二の電源回路部とを有する。

(もっと読む)

半導体装置

【課題】絶縁ゲート型電界効果トランジスタのスイッチング速度低下を防止し、省スペース化を実現する半導体装置を提供する。

【解決手段】本発明に係る半導体装置90は、絶縁ゲート型電界効果トランジスタとコンデンサが同一チップ上に形成されたものであって、表層において、n−型エピタキシャル層2を挟持するp型ボディ領域5内にそれぞれ配設されたn+型ソース領域6の当該n−型エピタキシャル層2に最近接する端部間に亘る領域上に配設された絶縁層7と、絶縁層7を介してn−型エピタキシャル層2と対向されるコンデンサ上部電極40と、絶縁層7上でコンデンサ上部電極40の両サイドに絶縁分離されるように、かつチャネル形成可能な位置に配設されたゲート電極31を備える。コンデンサC1は、コンデンサ上部電極40を上部電極とし、これと絶縁層7を介して対向配置されるn−型エピタキシャル層2を下部電極とする。

(もっと読む)

双方向スイッチ素子及びそれを用いた双方向スイッチ回路

【課題】安定に動作する双方向スイッチ素子を実現できるようにする。

【解決手段】双方向スイッチ素子は、窒化物半導体からなる半導体層積層体203と、半導体層積層体203の上に形成された第1のオーミック電極211及び第2のオーミック電極212と、第1のゲート電極217及び第2のゲート電極218とを備えている。第1のゲート電極217は、第1のオーミック電極211と電位が実質的に等しい第1のシールド電極221に覆われている。第2のゲート電極218は、第2のオーミック電極212と電位が実質的に等しい第2のシールド電極222に覆われている。第1のシールド電極221の端部は、第1のゲート電極217よりも第2のゲート電極218側に位置し、第2のシールド電極222の端部は、第2のゲート電極218よりも第1のゲート電極217側に位置している。

(もっと読む)

キャパシタ、集積装置、高周波切替装置及び電子機器

【課題】能動素子で扱う信号の影響を抑制しつつ、十分な容量密度を得られるキャパシタ、集積装置、高周波切替装置及び電子機器を提供する。

【解決手段】絶縁層12と、絶縁層12の上に設けられた半導体層13と、半導体層13において、能動素子が形成されるアクティブ領域とは電気的に分離して設けられたダミーアクティブ領域20と、を有する基板10と、基板10におけるダミーアクティブ領域20の上に、互いに対向して配置された第1電極31及び第2電極32と、第1電極31と、第2電極32と、の間に設けられた第1誘電体部40と、を備える。

(もっと読む)

解析装置及び半導体装置

【課題】 本発明の課題は、複数段の電源スイッチを段階的にオンすることによって内部回路に電源供給する半導体装置において、電源供給開始から起動可能となるまでの復帰時間を短縮することを目的とする。

【解決手段】 上記課題は、複数段の電源スイッチを段階的にオンすることによって内部回路に電源供給する電源供給回路を解析する解析装置であって、前段までの電源スイッチをオン状態とし、オンすることによって発生する許容ノイズ量を超えない最大電源ノイズ量となる電源スイッチサイズを次段の電源スイッチとして決定する電源スイッチサイズ決定手段と、前記次段の電源スイッチサイズによる電源ノイズが前記オンされてから収束判定量以下となるまでの時間をオン時間間隔として決定するオン時間間隔決定手段とにより達成される。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及びプログラム

【課題】半導体集積回路において、シールド配線を配置することで配線間のクロストークの影響を削減するとともに、配置したシールド配線の電位を安定化させること。

【解決手段】半導体集積回路の設計方法は、コンピュータが、半導体集積回路の配線パターンにおいて、配置済の信号配線に対して複数のシールド配線を配置する工程と、前記複数のシールド配線のそれぞれを電源配線に接続する工程と、前記複数のシールド配線を相互に接続する工程と、前記複数のシールド配線のうちの電源配線に接続されていないものを除去する工程と、を含む。

(もっと読む)

半導体装置の試験方法及び半導体装置

【課題】電源ノイズの影響を受けることなく、TDT試験を正常に実施できるようにする。

【解決手段】半導体装置における試験対象の内部回路を複数の回路ブロックに分割し、同時に動作させる回路ブロックを変化させて判定試験を行うとともに、判定試験の実行時に発生した電源ノイズを検出して、判定試験の結果及び検出された電源ノイズに基づいて、電源ノイズの影響を受けることなくTDT試験を正常に実施できる適切な回路規模を判定し、判定結果に基づいて回路ブロックに供給するクロックを制御することで同時に動作する回路ブロックの数を制限してTDT試験を実施する。

(もっと読む)

半導体装置

【課題】V−G間SSOノイズだけでなく、S−G間SSOノイズも低減することができる半導体装置10を提供する。

【解決手段】本発明の半導体装置10は、出力回路12毎に受信回路15の入力容量34と所定の関係を有する容量の近傍オンチップバイパスキャパシタ23を、所定の配線抵抗となるように設け、それぞれの出力回路12について容量および配線抵抗が所定の関係となる遠方オンチップバイパスキャパシタ24を、複数の出力回路12に共通に設ける。

(もっと読む)

半導体集積回路及び半導体集積回路の電源スイッチ制御方法

【課題】電源スイッチを非導通状態から導通状態に遷移させる時間を最適化できる半導体集積回路及びその電源スイッチ制御方法を提供する。

【解決手段】共通電源配線と、第1の回路と、それぞれ電源スイッチ制御信号に基づいて導通、非導通が制御され共通電源配線と第1の回路との間を並列に接続する複数の電源スイッチと、電源スイッチ制御信号と複数の電源スイッチとの間に接続され電源スイッチ制御信号が非導通状態から導通状態に遷移するときに電源スイッチ制御信号の遷移をそれぞれ異なった遅延時間だけ遅延させて複数の電源スイッチに伝え複数の電源スイッチをそれぞれ時間をずらして非導通状態から導通状態に遷移させる遅延回路と、各遅延回路の遅延時間の増減を制御する遅延時間制御部と、を備える。

(もっと読む)

半導体基板および半導体装置

【課題】トレンチゲート型などの微細MOSFETにおいて、MOSFETの動作電流とダイオード電流を検出することができる半導体基板を提供する。

【解決手段】半導体基板において、半導体基板1は、主電流領域2と主電流領域2に流れる主電流より小さい電流が流れる電流センス領域3を有し、主電流領域2は、主面にソース電極8が配置され、ソース電極8はp型半導体領域(ボディ)6とn+型半導体領域(ソース)7に接触し、電流センス領域3は、主面にMOSFET電流検出用電極10およびダイオード電流検出用電極11が配置され、MOSFET電流検出用電極10はp型半導体領域(ボディ)6とn+型半導体領域(ソース)7に接触し、ダイオード電流検出用電極11はp型半導体領域(ボディ)6に接触する。

(もっと読む)

半導体装置

【課題】スイッチング素子による高温の悪影響を回避して、誤点弧を防止する回路をスイッチング素子と同一の基板上に配置した半導体装置を提供する。

【解決手段】基板5上の導電体パターン51,52上にNチャネル型のMOSFET10、及びNチャネル型で半導体材料が炭化珪素からなるJFET30を各別に近接して配置し、MOSFET10のゲート電極13とJFET30のドレイン電極31とをリード線61で接続する。MOSFET10をオン/オフに制御する外部からの駆動信号がJFET30のソース電極32及びドレイン電極31間を伝播するときに、ソース電極32及びゲート電極33間のゲート電圧の低/高に応じてJFET30のチャネル抵抗を大/小に変更することにより、MOSFET10のドレイン電極11及びソース電極12間のスイッチング波形の前縁を、後縁に比較して緩やかな傾斜にする。

(もっと読む)

静電気放電保護回路及び半導体装置

【課題】特定周波数のノイズ等を防ぐことができ、かつESD保護素子のトリガー電圧を調整できるESD保護回路及び半導体装置を提供する。

【解決手段】静電気放電保護回路は、信号線に接続された第1の主端子と、グラウンド線に接続された第2の主端子と、制御電圧を印加するための制御端子とを有し、制御端子に、トリガー電圧よりも高い制御電圧が印加されることで動作する静電気放電保護素子211と、信号線上に配置された第1の回路素子と、第1の回路素子と保護対象の回路との間の第1のノードで信号線に接続され、グラウンド線上の第2のノードでグラウンド線に接続された第2の回路素子とを含むフィルタ回路212と、第1のノードと第2の回路素子との間の第3のノードに接続された入力部と、上記制御端子に接続された出力部とを有し、バッファ又はインバータを含み、上記制御端子に制御電圧を印加する制御電圧印加回路213とを備える。

(もっと読む)

保護回路及び半導体装置

【課題】誤作動の発生を抑制することができる保護回路及び半導体装置を提供する。

【解決手段】一端が電源配線VDDに、他端がインバータ116の入力端子116Aに各々接続され、一端から特定流路に予め定められた周波数特性を有するサージ電流が流入した場合、サージ電流によって生じる磁界を打ち消す磁界を発生させるように誘導起電力を発生させてサージ電流の流れを妨げることにより、入力端子116Aに対して閾値電圧未満の電圧を印加し、一端から周波数特性を有さない駆動用電流が流入した場合、入力端子116Aに対して閾値電圧以上の電圧を印加する電流調整部14を保護回路10に設ける。

(もっと読む)

情報処理装置

【課題】 電源遮断機能を有するLSIにおいて、電源遮断をオンオフするときにリーク電流による電流が急激に変化すると電源線にノイズを生ずる。

【解決手段】 情報処理装置であって、回路ブロックと、前記回路ブロックに電源を供給するためのローカル電源線と、電源線と、前記電源線と前記ローカル電源線の間にそのソース―ドレイン経路が設けられる第1のトランジスタとを有し、前記第1のトランジスタは、第1の状態においてはオフ状態に制御され、第2の状態においてはオン状態に制御され、前記第1の状態から前記第2の状態に移行する際に、前記第1のトランジスタは、前記第1のトランジスタのソース―ドレイン経路を流れる電流の変化率が、所定の値を超えないように制御されることを特徴とする。

(もっと読む)

半導体集積回路およびそれを内蔵した高周波モジュール

【課題】RF送信出力信号の高調波成分を低減する。

【解決手段】半導体集積回路110のアンテナスイッチ100の送信スイッチ104は送信端子102と入出力端子101の間にS・D電流経路が接続されゲート端子Gが送信制御端子108に接続された送信電界効果トランジスタを含み、受信スイッチ105は入出力端子101と受信端子103の間にS・D電流経路が接続されゲート端子Gが受信制御端子109に接続された受信電界効果トランジスタを含む。送信と受信とのnチャネル型MOS電界効果トランジスタは、シリコンオンインシュレータ(SOI)構造で形成される。アンテナスイッチの高調波成分を低減する値に設定された電圧発生回路10の基板電圧は、SOI構造の支持シリコン基板に接続された端子108、109に供給される。

(もっと読む)

半導体集積回路

【課題】より信頼性の高い半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、入力信号DINを記憶保持する複数のフリップフロップF1と、複数のフリップフロップF1からの出力の多数決結果MJを出力する多数決回路7と、複数のフリップフロップF1の出力不一致を検出し、エラー信号を出力するエラー検出回路2と、エラー検出回路2からのエラー信号を監視する監視回路3と、を備え、監視回路3は、エラー検出回路2からのエラー信号をもとに、複数のフリップフロップF1のうち、出力不一致が発生しているフリップフロップF1に対して書き戻しを行うリフレッシュ動作を指示するとともに、リフレッシュ動作により書き戻らなかった場合には外部に通知を行うものである。

(もっと読む)

半導体集積回路、ならびに、その設計方法および製造方法

【課題】ダミー回路を備えることなく、設計時や製造時においても、配線パターンのみの変更によりFFにおけるホールドエラーを解消することができる半導体集積回路、ならびに、その設計方法および製造方法を提供する。

【解決手段】本発明の半導体集積回路は、第1および第2のフリップフロップセルを含む複数のスタンダードセルからなるものである。第1および第2のフリップフロップセルは、同一の寸法のそれぞれの領域内に共通のトランジスタ配置パターンで配置された複数のトランジスタを有するとともに、複数のトランジスタを相互に接続してフリップフロップ回路を構成する互いに異なる配線パターンの配線を有し、それぞれの領域内の同一の位置に配置された同一の寸法の少なくとも1個のトランジスタを、回路的に異なる位置に使用したフリップフロップ回路を構成するセルである。

(もっと読む)

201 - 220 / 1,289

[ Back to top ]