Fターム[5F038BH19]の内容

Fターム[5F038BH19]に分類される特許

121 - 140 / 1,289

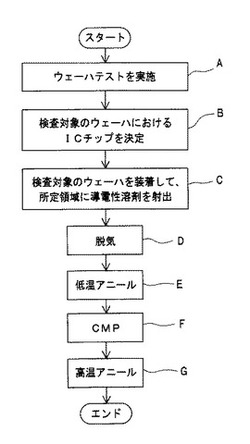

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

電力増幅器

【課題】複数のトランジスタを均一に動作させ、低消費電力及び良好な歪特性を実現する。

【解決手段】高周波信号を増幅する電力増幅器100であって、上部電極120a及び下部電極120bを有し、高周波信号が入力される整合容量120と、整合容量120の下部電極120bから出力される高周波信号を増幅する複数のトランジスタ110が所定の方向に並んで配置されているトランジスタ列とを備え、トランジスタ列に隣り合う領域において、トランジスタ列の両端から略等しい距離には、接地されたビアホール170が形成され、下部電極120bは、ビアホール170を挟んで高周波信号が均等に分配されるように配置されたマイクロストリップ線路であり、複数のトランジスタ110のベース端子に接続される。

(もっと読む)

半導体パッケージ

【課題】ボンディングワイヤのループインダクタンスを低減した半導体パッケージを提供する。

【解決手段】所定の方向に交互に配置された信号用パッドおよび補助パッドのそれぞれが複数設けられた半導体装置と、信号用ボンドフィンガー、電源電圧用ボンドフィンガーおよび接地電位用ボンドフィンガーのそれぞれが複数設けられたパッケージ基板と、を有する。複数の信号用パッドのそれぞれが複数の信号用ボンドフィンガーのそれぞれと第1のワイヤを介して接続され、複数の電源電圧用ボンドフィンガーおよび複数の接地電位用ボンドフィンガーのそれぞれが複数の補助パッドのそれぞれと第2のワイヤを介して接続されている。第1のワイヤが、電源電圧用ボンドフィンガーに接続された第2のワイヤと接地電位用ボンドフィンガーに接続された第2のワイヤとの間に配置されている。

(もっと読む)

半導体パッケージ

【課題】ボンド・ワイヤの寄生インダクタンスを小さくし、高周波特性を良好とすることができる半導体パッケージを提供する。

【解決手段】高周波信号が入力される入力整合回路を有しダイボンド領域に配された半導体集積回路チップと、前記ダイボンド領域の周辺に配されたリード端子と、を備え、前記半導体集積回路チップが有する各端子と前記各リード端子とがボンド・ワイヤにより接続された半導体パッケージにおいて、前記ダイボンド領域の中央部より前記入力整合回路に高周波信号を入力させるための前記リード端子である高周波入力端子側および/または前記入力整合回路のグランド接続用の前記リード端子であるグランド端子側にシフトした位置に前記半導体集積回路チップは配される構成とする。

(もっと読む)

半導体装置及びその制御方法

【課題】内部電圧生成回路を活性化させる際又は非活性化させる際における内部電圧の急激な変動を防止する。

【解決手段】外部電圧VDDから生成した内部電圧VPPを内部電源配線110aに供給する内部電圧生成回路110と、内部電圧生成回路110の動作を制御する制御回路300と、前記第1の電圧のレベルを検出する電圧検出回路330とを備える。例えば、制御回路300は、内部電圧生成回路110を活性化させる場合、内部電圧VPPの供給能力を第1の速度で段階的に上昇させ、内部電圧生成回路110を非活性化させる場合、内部電圧VPPの供給能力を第1との速度と異なる第2の速度で段階的に下降させる。これにより、内部電圧生成回路110を活性化/非活性化させる際の内部電圧VPPの大幅な変動をそれぞれ最適に防止することが可能となる。

(もっと読む)

半導体装置

【課題】 カップリングノイズを低減すること。

【解決手段】 半導体装置は、第1の回路と、第2の回路と、第1の配線と、一対のシールド線とを含む。第1の回路は、所定電圧を発生する電圧発生回路を含み、所定電圧を出力端に出力する。第1の配線は、第1の回路の出力端を第2の回路の入力端に結線する。一対のシールド線は、第1の配線を挟むように配置され、一方には電圧発生回路および第2の回路の少なくとも一方を駆動する電源電位が供給され、他方には電圧発生回路および第2の回路の少なくとも一方を駆動する接地電位が供給される。

(もっと読む)

半導体チップ及びこれを備える半導体装置

【課題】出力バッファのスイッチングに伴う電源ノイズがストローブ出力バッファに伝搬することを防止する。

【解決手段】データ信号DQ0を出力するデータ出力バッファOB0と、データ出力バッファOB0に電源電位VDDQを供給する電源パッド110v1と、電源パッド110v1に接続される電源配線120v1と、ストローブ信号DQSを出力するストローブ出力バッファOBdqsと、ストローブ出力バッファOBdqsに電源電位VDDQを供給する電源パッド110v2とを有し、電源配線120v1と電源パッド110v2は、互いに電気的に独立している。これにより、データ出力バッファOB0のスイッチングに伴う電源ノイズがストローブ出力バッファOBdqsに伝搬しないことから、ストローブ信号DQSの信号品質を高めることが可能となる。

(もっと読む)

スキャンテスト回路、テスト回路生成方法およびテストパタン生成方法

【課題】異なるクロックドメインに属する回路間でデータの授受がある回路において、半導体集積回路のスキャンパスを用いてクロストークの影響を考慮した遅延試験を行うことができる。

【解決手段】第1回路群は、第1のクロックドメインに属する複数のスキャンフリップフロップ(F12、F14)を備え、信号の伝達遅延を測定する第1データパス(102)を含む。第2回路群は、第2のクロックドメインに属する複数のスキャンフリップフロップ(F11、F13、F15)を備え、第1データパス(102)に対してクロストークにより影響を与える第2データパス(101)を含む。第3データパスは、第1回路群・第2回路群間でデータを授受する。クロック切り換え回路(M10)は、制御信号に応答して、第2回路群に供給される第2クロック信号(CK2)を、第1回路群に供給される第1クロック信号(CK1)に替えて第2回路群に供給する。

(もっと読む)

半導体集積回路および電源配線方法

【課題】信号配線リソースを確保しながら、チップ中心部のIRドロップを少なくすることのできる半導体集積回路および電源配線方法を提供する。

【解決手段】実施形態の半導体集積回路は、チップ内に等間隔で配線される下層電源配線1と直交する方向に所定の間隔で配線される上層電源配線が、下層電源配線との接続用のビア3が配線中央部にのみ配置された上層電源配線2Aと、配線中央部を除く領域に上層電源配線2Aへの配置個数よりも多数のビア3が配置された上層電源配線2Bとの対により構成され、上層電源配線2Aの上層電源配線2Bに対する配線幅の比が、配線中央部を除く領域では、上層電源配線2Aの上層電源配線2Bに対する供給電流比の逆数であり、配線中央部では、供給電流比の逆数よりも大きい。

(もっと読む)

半導体装置

【課題】内部回路の動作時における電源ノイズの影響を抑え、少ピン化および小面積化を実現する半導体装置を提供することである。

【解決手段】第1の内部回路102に対する電源線PL1と第2の内部回路104に対する電源線PL2とは共通のピン端子30aに接続され、第1の内部回路102に対する接地線SL1と第2の内部回路104に対する接地線SL2とは共通のピン端子30bに接続される。第1の内部回路102の動作時に電源線PL1上に発生した電源ノイズは、電源線PL1に介挿され、ゲートが接地線SL1に接続されたPチャネルMOSトランジスタP1および電源線PL1および接地線SL1の間に設けられたキャパシタC1により吸収される。接地線SL1上に発生した電源ノイズは、接地線SL1に介挿され、ゲートが電源線PL1に接続されたNチャネルMOSトランジスタN1およびキャパシタC1により吸収される。

(もっと読む)

パワーゲーティングCMOS回路及びスーパーカットオフCMOS回路におけるチャージリサイクリング

【課題】MTCMOS回路やSCCMOS回路等のパワーゲーティングされた回路におけるモード移行時のパワー消費の低減や、ウェークアップ時間や、パワーゲーティング構成により生じるノイズを低減する。

【解決手段】第1の回路ブロックと第1のスリープトランジスタとの間の第1の仮想グラウンドノードと、第2の回路ブロックと第2のスリープトランジスタとの間の第2の仮想グラウンドノードと、第1の仮想グラウンドノードを第2の仮想グラウンドノードに接続し、第1の回路ブロックによるアクティブモードからスリープモードへの移行、及び第2の回路ブロックによるスリープモードからアクティブモードへの移行、またはその逆の間に第1の回路ブロックと第2の回路ブロックとの間のチャージリサイクリングを可能とするトランスミッションゲート(TG)またはパストランジスタとを有する回路である。

(もっと読む)

半導体集積回路

【課題】外部電源電圧を降圧するレギュレータを内蔵することによるチップ面積の増大を抑え且つ降圧電圧の安定化を実現できる半導体集積回路を提供する。

【解決手段】外部電源電圧(Vext)よりも低い内部電源電圧(Vint)で動作する内部回路を持つ半導体集積回路において、内部電源電圧を生成するレギュレータ(150〜157)を、バッファ及び保護素子を配置するための第2の領域(2)に配置することにより、降圧電源回路のオンチップ化による面積オーバヘッドを低減する。降圧電圧を伝達するループ状の電源幹線(L20)を用い、電源幹線に外付け安定化容量を接続するための電極パッドを設ける等により、低消費電力を更に促進する。

(もっと読む)

半導体集積回路装置

【課題】入力回路ブロックの入力配線と出力回路ブロックの出力配線を短くする。

【解決手段】半導体集積回路装置30において、入力回路ブロック32用の外部接続用電極P2及びP3は、入力回路ブロック32と出力回路ブロック33との間に複数配置されており、出力回路ブロック33用の外部接続用電極P1及びP4は、出力回路ブロック33とリード電極34及び35との間に複数配置されており、金属細線Wb1及びWb2を介して外部接続用電極P1及びP2に接続されるリード電極34と、金属細線Wb3及びWb4を介して外部接続用電極P3及びP4に接続されるリード電極35は、いずれも、入力回路ブロック32、外部接続用電極P2及びP3、出力回路ブロック33、外部接続用電極P1及びP4、リード電極34及び35の順に配置された方向と平行する方向に複数配置されている。

(もっと読む)

電子装置およびその製造方法

【課題】半導体基板に設けられた貫通穴に、絶縁体を介して2つの導電体を充填してなるキャパシタ構造体を有する電子装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の表裏両主面11、12間を貫通する貫通穴30には、当該穴の内面側から第1の導電体40、絶縁体50、第2の導電体60が順次充填されてキャパシタ構造体20が形成されており、キャパシタ構造体20は、貫通穴30の内部から半導体基板10の両主面11、12まで連続して形成され、キャパシタ構造体20の静電容量は、キャパシタ構造体20のうち貫通穴30に位置する部位の容量と両主面11、12に位置する部位の容量との合計とされている。

(もっと読む)

測定結果管理システム、管理サーバ、及び半導体集積回路装置

【課題】実際に稼動している半導体集積回路装置の実動作に影響を与える要因を解析し、更にその要因を低減することが可能な半導体集積回路装置を提供する。

【解決手段】測定対象である半導体集積回路131と、この半導体集積回路のジッタ又はノイズジッタ、ノイズ等の実動作に影響を与える物理量を測定する測定回路(半導体集積回路装置)130とを同一チップ上に構成する。測定回路の測定結果を解析し、測定対象の半導体集積回路を調整する回路にフィードバックさせる。

(もっと読む)

半導体装置

【課題】無線通信によりデータの交信を行う半導体装置において、装置を大型化することなく、アンテナの感度を向上させ、チップをノイズから保護することを課題とする。

【解決手段】コイル状のアンテナと当該コイル状のアンテナに電気的に接続された半導体集積回路とを有する。コイル状のアンテナと重なるように半導体集積回路を配置する。このように、半導体装置内のコイル状のアンテナと半導体集積回路の配置を工夫することで、装置を大型化することなく、アンテナの感度を向上させて、半導体集積回路が動作するために十分な電力を得ることができる。

(もっと読む)

半導体集積回路のノイズ耐性評価方法およびノイズ耐性評価装置

【課題】大規模な半導体集積回路であってもノイズ耐性評価が短時間で可能なノイズ耐性評価方法を提供する。

【解決手段】回路ネットリストを作成する第1のステップS11と、能動素子を受動素子回路に置き換えて置換回路ネットリストを作成する第2のステップS12と、トランジスタの制御端子に該当する制御ノードを抽出する第3のステップS13と、ノイズ注入ノードを設定する第4のステップS14と、所定周波数のノイズを設定し、互いに異なる制御ノードとノイズ注入ノード間の経路のインピーダンスを計算する第5のステップS15と、制御ノード、ノイズ注入ノードおよび経路の各組み合わせにおけるインピーダンスのリストを作成する第6のステップS16と、インピーダンスの最小値から半導体集積回路のノイズ耐性を判定する第7のステップS17とを有してなるノイズ耐性評価方法100とする。

(もっと読む)

半導体装置

【課題】RFチップ本来の回路特性を抽出できるようにする。

【解決手段】半導体試験装置より出力された変調信号を増幅して出力する低雑音増幅器より出力される信号が供給されるとともに、低雑音増幅器により増幅された後に直交復調処理された変調信号を半導体試験装置用基板の伝送路に対して出力する増幅器に入力される信号が供給される試験回路をRFチップに備える。試験回路は、半導体試験装置より出力する変調信号の波形データが予め記憶され、低雑音増幅器より出力される信号及び増幅器に入力される信号をスペクトラム解析した解析結果と記憶されている変調信号の波形データとの比較によりRFチップにおけるチップ内ノイズ及びRFチップ本来の回路特性を抽出する。

(もっと読む)

半導体装置

【課題】交流リークが電圧検出回路に流れるのを防ぐことができる半導体装置を提供する。

【解決手段】半導体装置は、アンテナ回路102と、共振周波数調整回路126と、電圧検出回路と、第1の容量素子と、を有する。共振周波数調整回路126は、一方の端子がアンテナ回路102の第1の端子と電気的に接続された第2の容量素子と、第1の端子が第2の容量素子の他方の端子と電気的に接続され、第2の端子がアンテナ回路102の第2の端子と電気的に接続され、ゲートが第1の容量素子及び電圧検出回路と電気的に接続されたトランジスタと、を有する。

(もっと読む)

半導体装置

【課題】 制御端子が浮遊状態になると、予期しないリーク電流などにより電極に電荷が蓄積され、電極の電位が変動し、スイッチが誤動作してしまう可能性がある。

【解決手段】 クーロン力により湾曲させることで第1の信号電極と第2の信号電極とを接触または分離することが可能な架橋部と、前記架橋部を制御するための制御端子とを有するスイッチ素子と、前記制御端子に接続された第1の不揮発性半導体素子と、前記制御端子および前記第1の不揮発性半導体素子に接続された第2の不揮発性半導体素子とを備える。

(もっと読む)

121 - 140 / 1,289

[ Back to top ]