Fターム[5F038BH19]の内容

Fターム[5F038BH19]に分類される特許

101 - 120 / 1,289

半導体装置、および半導体装置の製造方法

【課題】シリンダ型下部電極の剥がれ落ちを防止する、半導体装置の製造方法を提供する。

【解決手段】複数の第1の開口を有するコア絶縁膜を半導体基板上に形成し、複数の第1の開口の側面を導電膜で覆う、シリンダ状の複数の下部電極を形成し、少なくとも複数の下部電極間のコア絶縁膜の上面を覆うサポート膜を形成し、サポート膜を用いて少なくとも複数の下部電極が形成される領域の外側を除去したマスク膜を形成し、マスク膜を形成した後、複数の下部電極間の一部にコア絶縁膜が残るように、コア絶縁膜に対して等方性エッチングを行うものである。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

半導体装置

【課題】半導体チップ内の銅配線が一部消失することを防ぐ。

【解決手段】上層プラグ一本当たりの下層の配線の面積が10000μm2以上になるような大面積の多層配線を有する半導体装置において、前記多層配線が半導体基板1Sの主面においてn型拡散層NSを介してpウエルPWに接続される構造を形成せず、前記多層配線をp型拡散層PSを介してpウエルPWに接続する構造、前記多層配線をp型拡散層PSを介してn型拡散層NSに接続する構造、前記多層配線をn型拡散層NSを介してnウエルに接続する構造、または半導体基板1S上に形成されたMISFETのゲート電極に接続する構造を形成する。

(もっと読む)

静電気保護回路

【課題】被保護回路を静電気放電から保護しつつ、周期性ノイズの印加によって被保護回路が誤動作することを抑制する静電気保護回路を提供する。

【解決手段】静電気放電から、被保護回路を保護する静電気保護回路であって、被保護回路への静電気放電の印加を抑制する抑制回路と、電圧レベルが周期的に変化する周期性ノイズが印加された際に、抑制回路の駆動をオフする制御回路と、を有する。

(もっと読む)

半導体装置

【課題】高出力の高周波信号の影響を抑制することが可能な半導体装置を提供する。

【解決手段】半導体装置は、電子回路が設けられた主面を有する半導体基板10と、前記主面の上に絶縁膜2,3,4を介して設けられたパッシブ回路30と、を備える。そして、前記半導体基板と前記パッシブ回路との間に前記パッシブ回路から絶縁されて設けられ、前記主面に平行な少なくとも1方向に流れる電流を遮断する間隙45を有した第1の導体層40と、前記第1の導体層と前記パッシブ回路との間に、前記第1の導体層および前記パッシブ回路から絶縁されて設けられ、前記主面に平行な少なくとも1方向に流れる電流を遮断する間隙55を有し、前記パッシブ回路から見た前記第1の導体層の間隙を覆う第2の導体層50と、を備える。

(もっと読む)

高周波半導体スイッチ

【課題】送信端子および受信端子に求められる特性を考慮して設計されたFETを有する高周波半導体スイッチを提供する。

【解決手段】高周波半導体スイッチ10は、複数の電界効果型トランジスタ50を有する。複数の電界効果型トランジスタ50は、それぞれ、基板100に間隔を置いて形成されたソース領域130およびドレイン領域140と、当該間隔上であって基板100上に形成されたゲート160と、基板100上に形成されソース領域に接続されるソースコンタクト172と、基板100上に形成されドレイン領域140に接続されるドレインコンタクト182とを含む。受信端子側に接続される受信端子側トランジスタ50aのソースコンタクト172およびドレインコンタクト182間の距離Lrは、送信端子側に接続される送信端子側トランジスタ50cのソースコンタクト172およびドレインコンタクト182間の距離Ltよりも長い。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑え、回路ブロックに電源供給するための複数の電源スイッチをオンするための時間間隔を適切に制御できるようにする。

【解決手段】回路ブロックに対する電源供給を管理する電源管理ユニット11と、回路ブロックA12への電源供給を制御する複数の電源スイッチPSWAと、回路ブロックAに供給する電源で動作し、その電位に応じた遅延を生成する遅延生成器13とを備え、電源スイッチは、電源供給を行うためにオン状態に制御されるときに、電源管理ユニット及び遅延生成器13の出力に基づいて回路ブロックAに供給される電源電位に応じた時間間隔で順次オン状態にするようにして、電源スイッチをオンするための時間間隔を回路ブロックAに供給される電源電位に応じて自動的に調整して電源供給を行う。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体回路および半導体装置

【課題】本発明では、上記のような問題を解消し、dV/dtによる誤動作を防止しつつも、外部要因に左右されることのない汎用的な誤動作防止機能を有する半導体回路および半導体装置を提供することを目的とする。

【解決手段】本発明にかかる半導体回路は、ON駆動信号に応答してON駆動電荷を充電するコンデンサ40と、OFF駆動信号に応答してOFF駆動電荷を充電するコンデンサ41と、ON駆動信号に応答して第1トリガー信号を発生させる信号発生回路20と、OFF駆動信号に応答して第2トリガー信号を発生させる信号発生回路21と、第2トリガー信号に応答して、ON駆動電荷を放電する放電回路30と、第1トリガー信号に応答して、OFF駆動電荷を放電する放電回路31とを備える。

(もっと読む)

半導体装置

【課題】出力トランジスタの形成領域から他の素子の形成領域への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体基板SUBと、1対の注入元素子DRと、アクティブバリア構造ABと、p型接地領域PGDとを備える。半導体基板SUBは主表面を有し、かつ内部にp型領域を有する。1対の注入元素子DRは、p型領域上であって主表面に形成される。アクティブバリア構造ABは、主表面において1対の注入元素子DRに挟まれる領域に配置される。p型接地領域PGDは、主表面において1対の注入元素子DRに挟まれる領域を避けて1対の注入元素子DRおよびアクティブバリア構造ABよりも主表面の端部側に形成され、かつp型領域に電気的に接続された、接地電位を印加可能な領域である。p型接地領域PGDは、1対の注入元素子DRに挟まれる領域と隣り合う領域において分断されている。

(もっと読む)

半導体装置

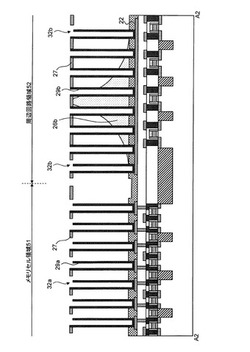

【課題】出力バッファにおいて発生したノイズが、他の出力バッファに伝搬することを防止し、且つ各出力バッファに安定した電源供給を行うことが可能な半導体装置を提供する。

【解決手段】外部電圧が供給される複数の電源パッド111,112と、複数のデータ出力パッド113,114と、複数の電源パッド111,112に共通接続された電源幹線411,412と、電源幹線から分岐した複数の分岐電源配線411B,412Bと、それぞれ対応する分岐電源配線411B,412Bから供給される電源電圧によって動作し、それぞれ対応するデータ出力パッド113,114を駆動する複数の出力バッファ72と、複数の分岐電源配線411B,412Bにそれぞれ設けられたローパスフィルタ回路1000とを備える。

(もっと読む)

半導体装置

【課題】半導体装置においてチップサイズに影響を与えないデカップリング容量を得る。

【解決手段】半導体装置は、基板1、10と、高濃度拡散層領域11と、第1ウェル4と、第2ウェル3とを具備している。基板1、10は第1導電型である。高濃度拡散層領域11は基板1、10上に形成され、第1導電型である。第1ウェル4は基板1、10上に形成され、高濃度拡散領域11の一方側に設けられ、第1導電型である。第2ウェル3は基板1、10上に形成され、高濃度拡散領域11の他方側に設けられ、第1導電型と逆導電型となる第2導電型である。第2ウェル3と高濃度拡散領域11との間、及び、第2ウェル3と基板1、10との間でデカップリング容量が形成される。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

2つのタイプの減結合コンデンサを備えた集積回路および方法

【課題】デュアル電圧パワーアイランドアーキテクチャにおいて、低いオフ状態リークを実現する事が可能な最適な減結合キャパシタンスのための方法およびシステムを提供する。

【解決手段】チップの低電圧領域において、誘電体膜厚の異なる2つの異なるタイプのコンデンサが使用される。膜厚の薄いコンデンサは常時オン状態の領域で使用され、膜厚の厚いコンデンサーは条件付きで起動される領域で使用される。これによって低いオフ状態リークをで減結合コンデンサーを使用できる。

(もっと読む)

電磁気干渉ノイズ低減回路

【課題】ドライバICでのEMIノイズを低減するためのEMIノイズ低減用電源回路を提供することである。

【解決手段】本発明の回路は、入力ポートと、少なくとも1つの出力ポートとを備えて外部機器を駆動するドライバICで、前記出力ポートに流入するEMIノイズを低減するためのものであって、前記ドライバICの前記少なくとも1つの出力ポートと、前記外部機器を接続する出力端との間に、それぞれ直列に配置される、少なくとも1つの抵抗を含む。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

電力用半導体装置及びその動作方法

【課題】電力用半導体装置がOFF状態の時に電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止する。

【解決手段】本発明の電力用半導体装置は、電源端子と出力端子との間に接続された出力トランジスタと、出力トランジスタのゲートに接続された第1ノードを充放電し、出力トランジスタをON/OFF制御するゲート充放電回路と、第1ノードと出力端子との間に接続されたショートスイッチ回路と、ショートスイッチ回路を制御するショート制御回路と、を備える。ターンオン期間、ON期間及びターンオフ期間において、ショート制御回路は、ショートスイッチ回路を介した第1ノードと出力端子との間の電気的接続を切断する。OFF期間において、ショート制御回路は、ショートスイッチ回路を介して第1ノードと出力端子との間を電気的に接続する。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

電力増幅器

【課題】複数のトランジスタを均一に動作させ、低消費電力及び良好な歪特性を実現する。

【解決手段】高周波信号を増幅する電力増幅器100であって、上部電極120a及び下部電極120bを有し、高周波信号が入力される整合容量120と、整合容量120の下部電極120bから出力される高周波信号を増幅する複数のトランジスタ110が所定の方向に並んで配置されているトランジスタ列とを備え、トランジスタ列に隣り合う領域において、トランジスタ列の両端から略等しい距離には、接地されたビアホール170が形成され、下部電極120bは、ビアホール170を挟んで高周波信号が均等に分配されるように配置されたマイクロストリップ線路であり、複数のトランジスタ110のベース端子に接続される。

(もっと読む)

101 - 120 / 1,289

[ Back to top ]