Fターム[5F038BH19]の内容

Fターム[5F038BH19]に分類される特許

21 - 40 / 1,289

EMIフィルタ

【課題】EMIフィルタが形成された半導体素子の小型化を図る。

【解決手段】本発明の実施形態のEMIフィルタは、第1のダイオードD1、第1のキャパシタC1、及び抵抗体Rを備える。第1のダイオードは、第1の半導体層中に設けられ、上記第1の電極、上記第1の半導体層、その表面に形成されたn形の第2の半導体層2A、及びその表面上に形成された第2の電極11を有する。第1のキャパシタは、上記第1の半導体層1表面に形成され、上記第1の電極、上記第1の半導体層、その表面上に形成された第1の誘電体膜10A、及びその上に形成され第2の電極と電気的に接続された第3の電極12を有する。抵抗体は、第1の半導体層上に形成され、第1のダイオードの第2の電極と電気的に接続された第4の電極14を有する。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜の漏れ電流試験に影響を与えることなく、ゲート・ソース間に抵抗を挿入した半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置は、ゲート電極及びソース電極間に抵抗が挿入されたトランジスタを内蔵する半導体装置であって、ゲート電極及びソース電極間に、抵抗に対して直列に挿入されたダイオードを備えることを特徴とする。

(もっと読む)

半導体装置

【課題】抵抗値が制御されることができる抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、絶縁膜14bと、半導体素子と、抵抗素子4tとを有する。絶縁膜14bは半導体基板101の少なくとも一部を被覆している。半導体素子は、半導体基板101の一部からなるチャネル領域と、電極とを有する。抵抗素子4tは、電極を流れる電流に対する抵抗となるように電極と電気的に接続され、かつ絶縁膜14bを介して半導体基板101上に設けられている。抵抗素子4tは半導体領域を含む。半導体基板101と抵抗素子4tとの間の電位差により半導体領域に空乏層が生じる。

(もっと読む)

窒化物半導体装置

【課題】スイッチングノイズ発生を抑制できるノーマリオフ形の窒化物半導体装置の提供。

【解決手段】本発明の実施形態の窒化物半導体装置は、AlxGa1−xN(0≦x<1)からなる第1の半導体層4と、AlyGa1−yN(0<y≦1、x<y)からなる第2の半導体層5と、導電性基板2と、第1の電極6と、第2の電極8と、制御電極7と、を備える。第2の半導体層は第1の半導体層に直接接合する。第1の半導体層は、導電性基板に電気的に接続される。第1の電極及び第2の電極は、第2の半導体層の表面に電気的に接続される。制御電極は、第1の電極と第2の電極との間の第2の半導体層の前記表面上に設けられる。第1の電極は、Si−MOSFET102のドレイン電極8aに電気的に接続される。制御電極は、前記MOSFETのソース電極6aに電気的に接続される。導電性基板は、前記MOSFETのゲート電極7aに電気的に接続される。

(もっと読む)

半導体集積回路及びその電源制御方法

【課題】電源遮断状態からの復帰の際に、周辺回路の動作に影響を与えない半導体集積回路及び電源制御方法が、望まれる。

【解決手段】半導体集積回路は、第1及び第2の電源線と、サブ電源線と、第1の電源線とサブ電源線との間に配置される第1のスイッチ回路と、第2の電源線とサブ電源線との間に配置される論理回路と、第1の端子が第1の電源線と接続される容量素子と、容量素子の第1の端子の他方の第2の端子の接続を、第1の電源線、又は、サブ電源線、のいずれかに切り替える第2のスイッチ回路と、論理回路を非活性化状態から活性化状態に遷移させる場合に、第1のスイッチ回路により、第1の電源線及びサブ電源線の接続を遮断しつつ、第2のスイッチ回路により、第2の端子の接続を少なくても1回以上、サブ電源線に接続した後、第1の電源線に接続する制御回路と、を備えている。

(もっと読む)

ラッチ回路、トリミング回路、システム、判定プログラム、確認方法、及び判定方法

【課題】入力信号の状態が適正であるかを確認することができる、ラッチ回路、トリミング回路、システム、判定プログラム、確認方法、及び判定方法を提供する。

【解決手段】トリミング回路14の読出回路20から出力されるトリミング素子であるヒューズ素子H1の状態に応じた入力信号I1が入力されるラッチ回路22を、ラッチ回路L1と、ラッチ回路L2と、一致確認回路26と、で構成している。ラッチ回路L1は、入力信号I1の論理値をタイミングT1で保持して、保持した論理値に応じた出力信号O1をトリミング回路14の外部に出力する。ラッチ回路L2は、タイミングT1よりも遅いタイミングT2で保持して、保持した論理値に応じた出力信号O2を出力する。一致確認回路26は、排他的論理和回路30により構成されており、出力信号O1と出力信号O2とが一致しているか否かを示す一致判定信号X1を外部の判定回路18に出力する。

(もっと読む)

プロセッサシステム及び半導体集積装置

【課題】処理速度の低下を最低限に抑えかつ従来技術に比較して消費電流の変動を抑える。

【解決手段】プロセッサシステム1は、プログラムメモリ2に格納された複数の命令コードを任意の順序で連続して実行する。テーブルメモリ53は、各命令コードと各命令コードの実行時の消費電流量との関係を示す消費電流量テーブルを格納する。電流変動抑制回路51は、消費電流量テーブルを参照して、連続する2つの命令コードの実行時の消費電流量の差の大きさが所定のしきい値以下になるように、上記連続する2つの命令コードのうちの一方の命令コードの実行時にプロセッサシステム1に流す補正消費電流を算出し、上記算出された補正消費電流量の補正消費電流をプロセッサシステム1に流すように、補正消費電流発生回路54を制御する。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

半導体集積回路システムおよび半導体集積回路システムの配置配線方法

【課題】EMI低減に有効な半導体集積回路システムを提供する。

【解決手段】バスライン8上に配置された中央演算処理装置1と、演算論理装置6と、デカップリングキャパシタ形成領域100・合成論理形成領域200・インピーダンス形成領域300を有する半導体集積回路400と、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26・電源配線配置配線情報格納部28を有する記憶装置2とを備え、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26のそれぞれの格納データに基づいて、それぞれ合成論理形成領域200・デカップリングキャパシタ形成領域100・インピーダンス形成領域300における配置配線を実行する半導体集積回路システム10。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

半導体装置

【課題】出力信号を高速に変化させかつオーバーシュートやアンダーシュートを抑制できるようにする。

【解決手段】入力信号を反転して出力する主ドライバ11に加えて、補助ドライバ12を設け、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、変化開始から主ドライバの出力信号がある電圧レベルを超えるまでの期間では信号変化を補助するように制御部15により補助ドライバの動作を制御し、主ドライバの出力信号がある電圧レベルを超えてから第2の電圧レベルになるまでの期間に信号変化を抑制するように制御部により補助ドライバの動作を制御するようにして、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制できるようにする。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

ダイオード素子及び検出素子

【課題】従来の横型のダイオード素子は、表面二電極間における電流経路に半導体界面が現れるため、界面状態に起因する雑音が大きいという点を解決するダイオード素子、検出素子等を提供する。

【解決手段】ダイオード素子は、第一の導電型の低濃度キャリア層103と、第一の導電型の高濃度キャリア層102と、半導体表面上に形成されたショットキー電極104及びオーミック電極105と、を備える。低濃度キャリア層のキャリア濃度は、高濃度キャリア層のキャリア濃度より低く、オーミック電極の直下に第一の導電型の不純物導入領域106が形成される。ショットキー電極及びオーミック電極の間の半導体表面に、ショットキー電極とは電気的に接触しない第二の導電型の不純物導入領域107が形成され、第二の導電型の不純物導入領域が第一の導電型の不純物導入領域と接する。

(もっと読む)

電力増幅器

【課題】本発明は、発振電力を吸収する抵抗の抵抗値を容易に制御できる電力増幅器を提供することを目的とする。

【解決手段】本願の発明に係る電力増幅器10は、複数のトランジスタセルが形成された半導体基板12と、該半導体基板上に形成された、該複数のトランジスタセルのドレイン電極40と、該半導体基板上に該ドレイン電極と接続されるように形成された、ドレインパッド42と、該半導体基板に、該ドレインパッドに沿って該ドレインパッドと接するように形成されたイオン注入抵抗44と、該半導体基板上に該イオン注入抵抗を介して該ドレインパッドと接するように形成されたフローティング電極46と、該半導体基板の外部に形成された出力整合回路16と、該ドレインパッドと該出力整合回路を接続する配線18a,18b,18c,18dと、を備える。

(もっと読む)

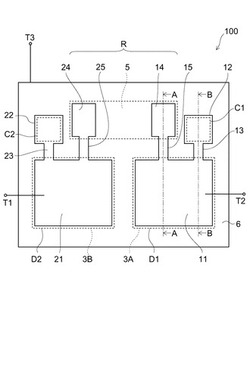

電磁波干渉フィルタ

【課題】小型化が可能な電磁波干渉フィルタを提供すること。

【解決手段】実施形態に係る電磁波干渉フィルタ10は、半導体基板11の表面上に形成された抵抗R、およびこの抵抗Rの両端にそれぞれ電気的に接続された一対のキャパシタC、をそれぞれ具備する複数の電磁波干渉フィルタ回路12と、これらの電磁波干渉フィルタ回路12間の半導体基板11に埋め込み形成された素子分離層13と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

21 - 40 / 1,289

[ Back to top ]