Fターム[5F038BH19]の内容

Fターム[5F038BH19]に分類される特許

41 - 60 / 1,289

半導体集積回路

【課題】出力トランジスタで発生するラッシュ電流を抑制する。

【解決手段】一つの実施形態によれば、半導体集積回路は、第一及び第二の出力トランジスタ、第一の遅延発生部が設けられる。第一及び第二の出力トランジスタは並列的に配置される。第一の出力トランジスタは、制御端子に第一の制御信号が入力され、第一の制御信号に基づいてオンして低電位側電源側に第一の電流を流し、第一の電流が流れ始めてから一定な電流になるまでに第一の時間を要する。第一の遅延発生部は、第一の制御信号が入力され、第一の制御信号を第一の時間よりも短い第二の時間だけ遅延させた第二の制御信号を出力する。第二の出力トランジスタは、制御端子に第二の制御信号が入力され、第二の制御信号に基づいてオンして低電位側電源側に第二の電流を流す。

(もっと読む)

半導体装置

【課題】多層配線内の信号線とそれに接続されるビアとを共に同軸構造にする。

【解決手段】多層配線には、例えば、異なる層に設けられる信号線10,20と、これらの信号線10,20間を接続する接続部30(ビア)が設けられる。信号線10,20は、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。更に、信号線10,20間を接続する接続部30も、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。信号線10,20のほか接続部30も同軸構造とすることで、信号線10,20及び接続部30を伝送される信号の、周囲からの、又は周囲への、電磁気的な影響が効果的に抑制されるようになる。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】スイッチング用のパワーMOSFETと、そのパワーMOSFETよりも小面積でかつそのパワーMOSFETに流れる電流を検知するためのセンスMOSFETとが1つの半導体チップCPH内に形成され、この半導体チップCPHはチップ搭載部上に導電性の接合材を介して搭載され、樹脂封止されている。半導体チップCPHの主面において、センスMOSFETが形成されたセンスMOS領域RG2は、センスMOSのソース用のパッドPDHS4よりも内側にある。また、半導体チップCPHの主面において、センスMOS領域RG2は、パワーMOSFETが形成された領域に囲まれている。

(もっと読む)

低フラックス及び低ノイズの検出回路

【課題】低フラックスを用いている間のノイズレベルを減少することを可能にするような検出回路を提供する。

【解決手段】ソースフォロワ検出器型の検出回路は、結合ノードNに接続されたフォトダイオード1を備える。バイアス回路3は、逆バイアスである第1の状態とフローティングである第2の状態との間にフォトダイオード1をバイアスすることを可能にする。読み出し回路4は、結合ノードNに接続され、フォトダイオード1により測定された現状を示す信号を生成する。金属シールド5は結合ノードNの周りに配置される。金属シールド5は、読み出し回路4の出力に接続され、結合ノードNの電位と同じ方向に変動する電位を持つように構成される。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

トランジスタ及び半導体装置

【課題】SEU耐性が高く、高性能で低価なトランジスタ及び半導体装置を提供すること。

【解決手段】絶縁性基板12上に形成されたシリコン層と、シリコン層に形成され、第1導電型であるボディ(P−)15、第2導電型であるソース(N+)13、ドレイン(N+)14からなる部分と、ボディ(P−)15及びソース(N+)13にボディ(P−)15と同一導電型で接合され、ソース(N+)13と同じもしくは高い電位が供給されるボディ端子(P+)16と、を具備する。ボディ(P−)15において放射線によって発生した負電荷は、ボディ端子(P+)16を介して当該トランジスタ外に流出する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

半導体集積回路及びBGAパッケージ

【課題】実使用時におけるクロストークの発生の抑制と、実使用時以外における信号用端子の確保とを半田ボールを増加させずに実現することが可能な半導体集積回路及びBGAパッケージが提供される。

【解決手段】半導体集積回路10が提供される。バッファ15は、マクロ11に接続される信号入力端子15aと、パッド21に接続される信号出力端子15bとを備える。バッファ15は、マクロ11が出力するバッファ制御信号41に基づいて、信号入力端子15aに入力される信号を信号出力端子15bから出力する動作状態と信号入力端子15aに入力される信号を信号出力端子15bから出力しない非動作状態とが切り替わる。バッファ16は、バッファ制御信号41に基づいて、パッド22とマクロ12とを接続するマクロ接続状態とパッド22とグラウンド電位14とを接続するグラウンド電位接続状態とが切り替わる。

(もっと読む)

半導体集積回路

【課題】突入電流が周辺の回路へ及ぼす影響を低減しつつ、停止状態にある回路を短時間に動作状態とすることが可能な半導体集積回路を提供することである。

【解決手段】本発明にかかる半導体集積回路1は、領域PD1と、制御回路25と、回路26と、を備える。領域PD1には、電源線VDDと電源線VSDとの間にそれぞれ接続されたスイッチ21_1、22_1、23_1と、電源線VSDと電源線VSSとの間に接続された回路35と、が配置されている。回路26は、電源線VDDおよび電源線VSSから電源が供給され、回路35よりも最低動作電圧が高い回路である。スイッチ22_1はスイッチ21_1よりもオン抵抗が低い。スイッチ22_1は領域PD1のうち回路26と最も離れた頂点の近傍に配置されている。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

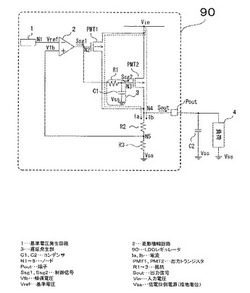

半導体集積回路装置

【課題】内部コアエリアのトランジスタを犠牲にすることなく、周辺エリアのトランジスタを用いてリップルフィルタによる電源供給回路を構成する。

【解決手段】入出力回路を構成するためのトランジスタが配列されてなる周辺エリア(図2の12に相当)をチップ上に有する半導体集積回路装置であって、ドレインを電源に接続し、ソースを負荷側に接続し、ゲートを容量素子(図2のC1)を介して交流的に接地する第1のトランジスタ(図2のMN1)と、容量素子をゲート・基板間によって形成する第2のトランジスタと、を周辺エリアに備える。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】ジッタ耐性検査における検査コストの低減を図りつつ、入力される主信号の特性劣化を抑制できる半導体集積回路を提供する。

【解決手段】半導体集積回路101は、主信号にジッタ信号が付加されてなる検査信号を生成する機能を有し、ジッタ信号の基となる信号を生成するジッタ信号生成部50と、電源線Vccと接地線GNDとの間に介在し、電源線Vccからの電力供給を受けて外部からの主信号を増幅して出力するバッファ回路10と、電源線Vccとバッファ回路10との間およびバッファ回路10と接地線GNDとの間に介在し電源線Vccからバッファ回路10への供給電力をジッタ信号の基となる信号の大きさに基づいて変化させることにより主信号にジッタ信号を付加するジッタ信号付加部30とを備える。

(もっと読む)

コンパレータ、及びそれを用いた半導体装置

【課題】新たな構成のチョッパ型のコンパレータを提供する。

【解決手段】コンパレータは、インバータと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、インバータの入力端子と出力端子とは、第1のスイッチを介して電気的に接続され、インバータの入力端子は、容量素子の一対の電極のうちの一方と電気的に接続され、容量素子の一対の電極のうちの他方は、第2のスイッチを介して参照電位が与えられ、入力された信号電位は第3のスイッチを介して容量素子の一対の電極のうちの他方に与えられ、インバータの出力端子から出力される電位を出力信号とし、第1のスイッチは、チャネルが酸化物半導体層に形成されるトランジスタを用いて構成される。

(もっと読む)

インダクタ

【課題】基体上に形成された絶縁膜中の多層配線層を用いたインダクタの、上下隣接配線間の寄生容量を低減する。

【解決手段】基体16上の絶縁膜17中に配設された複数の配線層18のうち、隣接する少なくとも2つの配線層の各々に形成された一周回の周回配線(A-B又はB-C)を有し、前記少なくとも2つの配線層に形成された前記一周回の周回配線(A-B及びB-C)の一端(B)は相互にビア2で接続され、前記少なくとも2つの配線層に形成された前記一周回の周回配線(A-B及びB-C)は、基体上方から見て基体面内で実質的に同一位置に配設されることを特徴とするインダクタ。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体装置設計装置、及びプログラム

【課題】より多くのI/Oセルを配置することができるようにする。

【解決手段】多層配線層には、電位供給用接続配線230が設けられている。電位供給用接続配線230は、平面視で外周セル列20を構成するI/Oセル200のいずれか、および内周セル列30を構成するI/Oセル200のいずれかと重なっている。そして電位供給用接続配線230は、外周セル列20の下方に位置する電源電位供給配線222を、内周セル列30の下方に位置する電源電位供給配線222に接続するとともに、外周セル列20の下方に位置する接地電位供給配線224を、内周セル列30の下方に位置する接地電位供給配線224に接続している。

(もっと読む)

半導体装置

【課題】従来の入出力セルよりも回路面積の大きな入出力セルを面積効率良く配置する。

【解決手段】半導体装置において、複数の第1バッファセル31〜34は、基板の一辺に沿って1列に設けられる。複数の第2バッファセル21,22は、複数の第1バッファセルよりも基板の中央寄りの位置に、複数の第1バッファセルの配列方向に沿って1列に設けられる。複数の第1パッド81〜88は、複数の第1バッファセルの上部に上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、複数の第1パッドよりも基板の中央寄りの位置に、上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、各々が、複数の第1バッファセルのいずれか1つと個別に接続される複数の第3のパッド61,63,65,66と、各々が、複数の第2バッファセルのいずれか1つと個別に接続される複数の第4パッド62,64とを含む。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

41 - 60 / 1,289

[ Back to top ]