Fターム[5F038CD04]の内容

Fターム[5F038CD04]に分類される特許

1 - 20 / 425

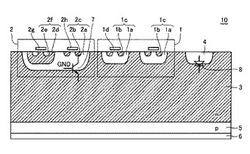

半導体装置

半導体装置

【課題】本発明は、半導体装置に負電流が流れた場合でも、回路素子を構成する深い半導体層の電位に対して、半導体基板の電位が低くなるのを抑制して寄生素子を作動させず、半導体装置の誤動作を防止する。

【解決手段】本発明は、n型の半導体基板3と、半導体基板3の一面に形成し、接続する負荷に電力を供給する電力素子1と、n型のソース・ドレイン領域を有するMOSトランジスタ2cを少なくとも1つ含む回路素子2と、電力素子1および回路素子2に対し独立して配置したp型の半導体層4と、半導体基板3および半導体層4と接続する外部回路とを備えている。外部回路は、電源と、電源に一端を接続する抵抗素子と、抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地するダイオードとを有し、抵抗素子の他端に半導体層4を接続する。

(もっと読む)

半導体装置及びアナログスイッチの制御方法

【課題】高い電圧を有する入力信号に対して適切に動作するアナログスイッチを有する半導体装置を提供する。

【解決手段】入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,入力端子に印加される入力電圧に応じて,Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,アナログスイッチを導通または非導通に制御する制御信号を可変電圧回路に供給する制御回路とを有する。可変電圧回路は,導通に制御する制御信号に応答して,可変生成される第1ゲート電圧と第2ゲート電圧とをPチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する。

(もっと読む)

チャージポンプ及びこれを用いた電源装置

【課題】プリント配線基板上の実装面積削減やコスト削減を実現することのできるチャージポンプを提供する。

【解決手段】チャージポンプ100は、フライングキャパシタ120の充放電用スイッチとして、半導体装置110に集積化されたフローティングNMOSFET111及び112のボディダイオード111d及び112dを用いる。

(もっと読む)

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

半導体集積回路装置

【課題】高周波回路に於いては、トランジスタ等の能動素子間および能動素子と外部端子の間を直流的に遮断する必要がありため、MIMキャパシタ等が多用される。これらのMIMキャパシタのうち、外部端子に接続されたものは、外部からの静電気の影響を受けやすく、静電破壊等の問題を発生しやすい。

【解決手段】本願発明は、半絶縁性化合物半導体基板上に形成された半導体集積回路装置であって、外部パッドに電気的に接続されたMIMキャパシタの第1の電極は前記半絶縁性化合物半導体基板に電気的に接続されており、一方、前記MIMキャパシタの第2の電極は前記半絶縁性化合物半導体基板に電気的に接続されている。

(もっと読む)

半導体集積装置

【課題】共通放電経路との間の異種電源間ESD保護回路をそれぞれの電源のパッドの近くに配置することのできる半導体集積装置を提供する。

【解決手段】実施形態の半導体集積装置1は、パッドPと、自己電源用ESD保護回路ESD1とを有し、VDDc系統の電源供給に使用の電源用I/OセルIOC1と、パッドPと、自己電源用ESD保護回路ESD1と、異種電源間ESD保護回路ESD2とを有し、VDDa、VDDb系統の電源供給に使用の電源用I/OセルIOC2とを備える。信号入出力用I/OセルIOC100と同一外形寸法の電源用I/OセルIOC1およびIOC2が、列状に配置されたIOC100と同列に配置され、電源用I/OセルIOC2の異種電源間ESD保護回路ESD2へ接続される共通放電経路CDLが、電源用I/OセルIOC1から、列状に配置されたIOC100を貫通して、電源用I/OセルIOC2へ配線される。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体装置

【課題】精度良く形成されたフィンを有しつつ、十分な特性を有するESD保護素子を形成することができる半導体装置を提供する。

【解決手段】実施形態にかかる半導体装置は、制御整流素子を有し、このシリコン制御整流素子は、半導体基板と、第1のウェル領域と、第2のウェル領域と、複数のフィン領域とを有する。第1のウェル領域は半導体基板の最外周に位置する。さらに、ウェルコンタクト領域よりも外周に位置し、第1の導電型の不純物拡散層領域を有し、且つ、電気的に浮遊状態にある最外周フィン領域を有する。

(もっと読む)

検波器及び受信機

【課題】低電圧、低電流、或いは低電力といった条件下でも使用することが可能な検波器を提供する。

【解決手段】検波器は、信号入力端子に接続された第1導電型の第1の半導体領域と、信号出力端子に接続された第2導電型の第2の半導体領域であって、第1の半導体領域に接して位置する第2の半導体領域と、交流的に接地された第1導電型の第3の半導体領域であって、第1の半導体領域から離間し且つ第2の半導体領域に接して位置する第3の半導体領域と、一端が第2の半導体領域に接続され、他端が交流的に接地された第1の抵抗素子と、を含む。

(もっと読む)

混合器、送信機及び通信システム

【課題】低電圧、低電流、或いは低電力といった条件下でも使用することが可能な混合器、送信機及び通信システムを提供する。

【解決手段】混合器は、交流的に接地された第1導電型の第1の半導体領域と、第1の信号入力端子に接続された第2導電型の第2の半導体領域であって、第1の半導体領域に接して位置する第2の半導体領域と、第1の信号出力端子に接続された第1導電型の第3の半導体領域であって、第1の半導体領域から離間し且つ第2の半導体領域に接して位置する第3の半導体領域と、第2の半導体領域上に位置する第1の絶縁膜と、第2の信号入力端子に接続された第1の導電体膜であって、第1の絶縁膜上に位置する第1の導電体膜と、を含む。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積を削減することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施形態に係る不揮発性半導体記憶装置は、半導体基板と、半導体基板上に積層され、垂直方向に直列接続された複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられ、所望の電圧をメモリセルアレイに供給する電源回路とを備える。電源回路は、電圧を生成するポンプ回路と、ポンプ回路の出力端子に接続され、出力端子の電圧値が所定の値を下回った場合にポンプ回路へ制御信号を出力するリミッタ回路と、出力端子に一端が接続され、出力端子の電圧を調整するように構成されたキャパシタと、キャパシタの他端に接続され、制御信号に基づき所定の電流値の定電流を用いてキャパシタを充電するブースト回路と、ブースト回路の充電動作を停止させるスイッチとを備える。キャパシタは、メモリセルアレイの直下に設けられる。

(もっと読む)

電源電圧判定回路

【課題】外部電源電圧の規格が異なるSDRAMの設計を共通化しつつ、該SDRAMの消費電流の増大を抑制できる電源電圧判定回路を提供する。

【解決手段】第1外部電源電圧と第2外部電源電圧間の電位差に比例する比例電圧と所定の一定電圧とを比較し、該比較結果を基に第1外部電源電圧がしきい値よりも低いとき、Pch基板電位設定回路は第1外部電源電圧をPチャネルトランジスタの基板へ供給し、Nch基板電位設定回路は第2外部電源電圧をNチャネルトランジスタの基板へ供給する。また、第1外部電源電圧がしきい値以上であるとき、Pch基板電位設定回路は第1外部電源電圧よりも高い電圧をPチャネルトランジスタの基板へ供給し、Nch基板電位設定回路は、第2外部電源電圧よりも低い電圧をNチャネルトランジスタの基板へ供給する。

(もっと読む)

半導体装置

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

半導体集積回路

【課題】電源電圧線とグランド線の両方を外部サージから保護することができる半導体集積回路を提供する。

【解決手段】GCNMOS回路70は、電源電圧線63またはグランド線64にサージ電圧が加えられたときに、サージ電圧を放電する。スイッチ72は、内部回路と電源電圧線63およびグランド線64とを接続または分離する。制御回路71は、スイッチ72を制御する。GCNMOS回路70、スイッチ72、および制御回路72のトランジスタは、厚膜トランジスタで構成され、コア領域61の内部回路のトランジスタは、薄膜トランジスタで構成される。制御回路71は、電源電圧線63またはグランド線64にサージ電圧が加えられたときに、スイッチ72をオフにする。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

半導体装置

【課題】複数のフローティング領域の間の電位差の不均一を軽減することができる半導体装置を提供する。

【解決手段】半導体装置は、領域3(k)と領域3(k+1)間に、外部容量6(k)を備えている。複数の外部容量6(k)は、その容量がkの増加とともに(即ち、図1の紙面右側から紙面左側に向かうほど)大きくなるように選定されている。この構造により、領域3(k)と領域3(k+1)間の電位差の不均一を軽減することができる。

(もっと読む)

抵抗素子及び反転バッファ回路

【課題】無駄な電流や信号の歪みを発生させることなく、抵抗素子層の周辺の半導体基板や、抵抗素子層の上部を通過する電源線、信号線等の電位によって抵抗値が変化するのを抑えることのできる抵抗素子及び反転バッファ回路を提供する。

【解決手段】抵抗素子10は、半導体基板14上に、第1の電極11及び第2の電極12を有する抵抗素子層13が形成されている。第1の電極11の電位によってバイアスされた第1の導電層15と、第2の電極12の電位によってバイアスされた第2の導電層16とで、抵抗素子層13の下部が均等に覆われている。このように、両端をバイアスされた抵抗素子層13の下部又は上部の少なくとも一方を覆う第1の導電層15及び第2の導電層16によって、抵抗素子層13の周辺の半導体基板14等との電圧差による抵抗値の変化を相殺することで、抵抗値の変化を抑える。

(もっと読む)

1 - 20 / 425

[ Back to top ]