Fターム[5F038DT10]の内容

Fターム[5F038DT10]に分類される特許

1 - 20 / 408

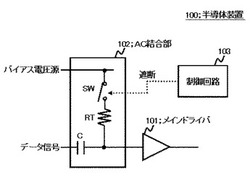

半導体装置及びそのテスト方法

【課題】データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置のDCテストの実施には、振幅を維持できないという問題がある。そのため、データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置であって、DCテストを可能にする半導体装置が、望まれる。

【解決手段】半導体装置は、データ信号を外部に出力するメインドライバと、データ信号が伝達する配線と接続されているコンデンサと、一端がコンデンサと接続され、他の一端がバイアス電圧源に接続されている終端抵抗と、バイアス電圧源と終端抵抗との間に接続されている第1のスイッチと、を含むAC結合部と、テストモード時にAC結合部のバイアス電圧源と終端抵抗との接続を、第1のスイッチにより遮断する制御回路と、を備える。

(もっと読む)

発振回路およびテスト回路

【課題】非導通状態におけるトランジスタから漏出するリーク電流を正確に測定することができるテスト回路を実現する。

【解決手段】遅延回路は、制御トランジスタ、測定対象トランジスタおよびコンデンサを備える。制御トランジスタは、入力端子の電位に応じて導通状態および非導通状態のうちのいずれかに移行することにより出力端子の電位を変化させる。チャネルの極性が前記制御トランジスタと同一の測定対象トランジスタは、電源とアースとの間において制御トランジスタに直列に接続される。コンデンサは、制御トランジスタが導通状態から非導通状態へ移行した場合に測定対象トランジスタから漏出したリーク電流の値に応じて出力端子の電位の変化を遅延させる。反転回路は、出力端子の電位を反転して前記入力端子に帰還させる。

(もっと読む)

半導体基板の評価方法および評価用半導体基板

【課題】例えばCCD、CMOSセンサ等の高歩留まりが要求される製品に使用される高品質ウェーハに関して、接合リーク電流特性を高精度で評価することが可能な半導体基板の評価方法および評価用半導体基板を提供する。

【解決手段】評価する半導体基板1に、複数のPN接合5と、該複数のPN接合5同士を分離する分離酸化膜6と、該分離酸化膜6の下に位置するチャネルストップ層3とを形成してから、前記複数のPN接合5における接合リーク電流を測定して評価を行う半導体基板の評価方法。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

半導体装置および電源供給方法

【課題】消費電力を低減することが可能な半導体装置および電源供給方法を提供することである。

【解決手段】本発明にかかる半導体装置は、内部回路3に電源を供給する電源供給部4と、内部回路3の複数の場所における特性をモニタする複数のモニタ部1_1〜1_Nと、複数のモニタ部1_1〜1_Nから出力された信号C_1〜C_Nに基づき算出されたモニタ値C_AVEと、設定された比較値COMPとの比較結果に応じて電源供給部4を制御する制御部2と、を備える。制御部2は、複数のモニタ部1_1〜1_Nにおける特性のばらつきに応じて比較値COMPを設定する。

(もっと読む)

半導体装置

【課題】裏面電極と導通したパッドを破ることなく、複数のバイアホールの検査を短時間で実施できる半導体装置を提供する。

【解決手段】半導体装置は、基板と、該基板の裏面に形成された裏面電極と、該基板を貫通するN個(Nは2以上の整数)のバイアホール16のそれぞれを経由して該裏面電極と電気的に接続されるように該基板の表面に形成されたN個のパッドと、該N個のパッドのそれぞれに電気的に接続されたN個のエピ抵抗30とを有する。そして、該N個のエピ抵抗を介して該N個のパッドと接続された配線34と、該配線と接続された検査用パッド36と、該N個のパッド、及び該N個のバイアホールを経由して該裏面電極に電流を流すように該基板の表面に形成された電流印加用パターンと、を備える。

(もっと読む)

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

半導体テスト回路

【課題】スキャンチェーンを構成する回路でバーンイン試験を行う際に、シフトモードとキャプチャモードを切り替えるスキャンモードコントロール信号が接続された回路に対してもストレス印加を可能にする半導体テスト回路を提供する。

【解決手段】半導体テスト回路は、シフトモードとキャプチャモードを交互に切り替える内部スキャンモードコントロール信号と、スキャンチェーンのスキャンフリップフロップ回路に供給する内部クロック信号を生成するスキャンチェーン制御信号生成部を備える。スキャンチェーン制御信号生成部は、スキャンフリップフロップ回路の出力を遷移させる内部クロック信号のエッジのタイミングにおいて、内部スキャンモードコントロール信号がシフトモードになるように、内部スキャンモードコントロール信号と内部クロック信号の相互のタイミングを制御する。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜の漏れ電流試験に影響を与えることなく、ゲート・ソース間に抵抗を挿入した半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置は、ゲート電極及びソース電極間に抵抗が挿入されたトランジスタを内蔵する半導体装置であって、ゲート電極及びソース電極間に、抵抗に対して直列に挿入されたダイオードを備えることを特徴とする。

(もっと読む)

半導体回路及びテスト方法

【課題】スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する半導体回路及びテスト方法を提供する。

【解決手段】複数の被試験回路と、試験回路に対応して設けられた複数の第1のラッチ回路と、第2のラッチ回路と、パターンアドレスに対応して入力信号が規定されたテストパターンのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を第2のラッチ回路に出力する総合判定回路と、複数の第1のラッチ回路と第2のラッチ回路とを、第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

(もっと読む)

集積回路および集積回路の接続不良検出方法

【課題】製品組立後の経年劣化による接続不良を含め、簡単な構成で被実装基板との接続不良を検出する。

【解決手段】集積回路に、同一の電位が与えられる2以上の比較電圧用パッドと、比較電圧用パッドにかかる電圧を比較して、その比較結果に基づいて被実装基板との接続不良の有無を示す信号を出力する比較判別回路とを設け、比較判別回路において、少なくとも2つの比較電圧用パッドにかかる電圧の電位差が所定の値を超えた場合に、接続不良を示す信号を出力させる。

(もっと読む)

半導体装置及びその評価方法

【課題】大規模な被測定素子の測定を短時間で行うことができ、且つ、高抵抗状態の短絡不良が発生した場合でも、不良の発生箇所を容易に特定することができるようにする。

【解決手段】直列接続された第1の被評価パターン101、及び該第1の評価パターンと隣接して配置された第2の被評価パターン102と、第2の被評価パターンとそれぞれ電気的に接続可能に設けられたノード情報伝達回路105とを備えている。第1の被評価パターンと第2の被評価パターンとは、互いに対向する領域により被測定素子103が構成されている。複数の第1の被評価パターンには、外部から所定の電圧が印加され、第2の被評価パターンとノード情報伝達回路とが電気的に接続されることにより、被測定素子の評価結果である第2の被評価パターンの電位がノード情報伝達回路に入力される。ノード情報伝達回路は入力された第2の被評価パターンの電位を外部へ順次出力する。

(もっと読む)

半導体装置および半導体装置の測定方法

【課題】半導体ウエハ上の半導体チップのアナログ特性の測定を精度良く行えるようにする。

【解決手段】半導体チップ1の被測定部3は半導体素子3a、回路3bである。被測定部3のアナログ特性を測定する測定回路4を設けている。測定回路4は、外部電源からプローブ針Pa、Pbを介して給電され、内部で測定用印加電圧を生成し、配線パターン5を介して被測定部3に印加する。測定回路4は、被測定部3の出力を配線パターン5から入力し、デジタルデータに変換する。測定回路4と配線パターン7を介して半導体チップ2の不揮発性メモリ6に接続され、デジタルデータが転送記憶される。一連の測定が終了した後に、不揮発性メモリ6からデジタルデータを取り出す。プローブ針の接触抵抗や浮遊容量の影響を低減して精度良いアナログ特性の測定ができる。

(もっと読む)

半導体装置、電子機器、および半導体装置の検査方法

【課題】電源端子または接地端子の接続不良を容易に検出する。

【解決手段】半導体装置の電源端子TCと第1の入出力端子T1との間には、電源端子TCがカソード側となり、第1の入出力端子T1がアノード側となるようにダイオードD11が設けられる。判定部10Aは、電源電圧Vccに等しいハイレベルの信号が第1の入出力端子T1に入力されたとき、電源端子TCの電圧が第1の入出力端子T1の電圧よりも低いか否かを判定する。

(もっと読む)

半導体試験装置及びそのテスト方法

【課題】メモリのテスト時の消費電流を抑え、メモリテスト時の周波数を高速化する。

【解決手段】制御回路103は、第1及び第2のテストパタンジェネレータ104、105によるテストがともにライトの場合、一方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータに対してテストシーケンスの実行を不許可とし、一方のテストパタンジェネレータからメモリグループ101、102の対応する一方のグループに対してライトのテストパタンを出力し、他方のグループに対するライトの実行を、一方のグループのライトのテストサイクル単位で時間的にずらし、一方のテストパタンジェネレータによる一方のグループのライトの終了後、他方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータから対応する他方のグループに対するライトのテストパタンを出力する。

(もっと読む)

半導体集積回路のテスト回路及び方法

【課題】ウェハ上の単一チップに形成された貫通ビアの不良の可否をテストすることができ、またパッケージングされた半導体集積回路に形成された貫通ビアの不良の可否をテストすることができる半導体集積回路のテスト回路及び方法を提供する。

【解決手段】半導体集積回路のテスト回路1は貫通ビア100、電圧駆動部200及び判定部300を含む。前記貫通ビア100は入力電圧V1を受信する。前記電圧駆動部200は前記貫通ビア100と連結されて前記入力電圧V1を受信し、テスト制御信号EN_P,EN_Nに応答して前記入力電圧V1のレベルを変化させてテスト電圧VTを生成する。前記判定部300は前記入力電圧V1及び前記テスト電圧VTを比較して結果信号を出力する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】TEGによる検査結果を容易に確認できるようにしつつ、TEGの占有面積を小さくする。

【解決手段】TEG群300は、第1テスト用パッド310、第2テスト用パッド312、及び複数のTEG(例えば第1TEG320、第2TEG340、及び第3TEG360)を有している。複数のTEGは、電気回路上、第1テスト用パッド310と第2テスト用パッド312の間に位置し、互いに直列又は並列に配置されており、かつ平面視で互いに重なっていない。本実施形態において、TEG群300を構成するTEGは、OBRICH(Optical Beam Induced Resistance Change)用のTEGである。

(もっと読む)

MOSトランジスタ集積回路およびMOSトランジスタ劣化度合模擬算出システム

【課題】MOSトランジスタ集積回路中のリング発振器では、使用期間が長くなるとそれを構成しているMOSトランジスタの特性に劣化が生じ、発振周期が大になって来る。従って、劣化度合を量的に把握する必要があったが、個別の集積回路につき、MOSトランジスタの劣化度合を算出するようにしたものは従来なかった。

【解決手段】リング発振器2を集積するMOSトランジスタ集積回路1内に、NMOSトランジスタの劣化のみ生ずる構成にしたリング発振器4、PMOSトランジスタの劣化のみ生ずる構成にしたリング発振器5を作り込む。それらの現時点での発振周期もしくは製造当初の発振周期を基に、劣化による増加遅延時間や発振周期を模擬算出装置7で算出する。

(もっと読む)

半導体集積回路のスキャンテスト回路の設計方法、スキャンテスト回路、およびスキャンテスト方法

【課題】半導体集積回路にスキャンパスを組み込んでスキャンテストを行う際に、シングルサイクルパスとマルチサイクルパスが混在している論理回路において、シングルサイクルパスの実動作速度によるテストを可能にすること。

【解決手段】実動作モードでタイミング解析を行い、マルチサイクルパスを抽出する。次に、シングルサイクルパスとマルチサイクルパスの分岐点と、シングルサイクルパスとマルチサイクルパスの合流点を抽出する。そして、上記分岐点から出力側のマルチサイクルパス側の経路上と、上記合流点から入力側のマルチサイクルパス側の経路上に、出力固定回路を挿入する。但し、出力固定回路は、マルチサイクルテスト時には、入力と同じ信号を出力し、シングルサイクルテスト時には、任意の固定値を出力する回路である。

(もっと読む)

1 - 20 / 408

[ Back to top ]