Fターム[5F045GH02]の内容

気相成長(金属層を除く) (114,827) | 機械加工プロセスとの組み合わせ (190) | 機械加工による前処理(膜形成が後) (70) | 研磨 (55)

Fターム[5F045GH02]の下位に属するFターム

化学的機械研磨(CMP) (29)

Fターム[5F045GH02]に分類される特許

1 - 20 / 26

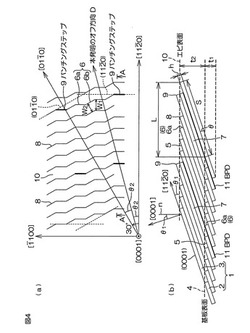

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】(0001)面に対して4°以下のオフ角θ1で傾斜したSi面が主面4とされたSiC基板2と、SiC基板2の主面4に形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、SiC基板2の主面4のオフ方向Dを、[11−20]軸方向および[01−10]軸方向に対して15°+/−10°の角度θ2で傾斜した方向にする。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】面取り部の形状を再成形するとともに、裏面クラウンを完全に除去し、平坦性に優れた、パーティクルのほとんど無いエピタキシャルウェーハを製造することができる方法を提供することを目的とする。

【解決手段】表裏の主面と該主面の外周の面取り部とからなるシリコン単結晶基板上にエピタキシャル層を成長させることによりエピタキシャルウェーハを製造する方法において、前記シリコン単結晶基板の前記裏面側の主面全面と前記裏面側の面取り部に裏面酸化膜を形成する工程と、該裏面酸化膜を形成したシリコン単結晶基板の表面側の主面上に、40μm以上の膜厚のエピタキシャル層を成長させる工程と、該エピタキシャル層表面に保護酸化膜を形成する工程と、該保護酸化膜を形成したシリコン単結晶基板の面取り部を研削及び研磨する工程と、その後、前記保護酸化膜を除去して、仕上げの洗浄を行う工程とを含むエピタキシャルウェーハの製造方法。

(もっと読む)

III族窒化物半導体基板およびIII族窒化物半導体基板の製造方法

【課題】III族窒化物半導体で構成される基板を生産する際の歩留まりを改善することを課題とする。

【解決手段】基板の表面から裏面まで貫通する貫通孔20を有するIII族窒化物半導体(AlxGa1−x−yInyN(0≦x≦1、0≦y≦1、0≦x+y≦1))で構成される基板30と、貫通孔20の内部に充填され、貫通孔20を塞ぐ、組成一様のIII族窒化物半導体で構成される充填材40と、を有するIII族窒化物半導体基板10を提供する。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法およびシリコンエピタキシャルウェーハ

【課題】{110}面からの傾斜角度が小さくてもヘイズレベルが良好で、かつシリコン単結晶エピタキシャル層の層厚均一性も良好であり、更に表面欠陥の少ないシリコンエピタキシャルウェーハの製造方法を提供する。

【解決手段】シリコン単結晶基板の主表面上にシリコン単結晶エピタキシャル層を気相成長させるシリコンエピタキシャルウェーハの製造方法であって、前記シリコン単結晶基板として、主表面が{110}面または{110}面からのオフアングル角度が0.5度未満のものを用い、かつ前記気相成長工程では、前記シリコン単結晶基板温度を1170℃〜1190℃として気相成長することを特徴とするシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板1は、III族窒化物結晶基板1の任意の特定結晶格子面のX線回折条件を満たしながら結晶基板の主表面1sからのX線侵入深さを変化させるX線回折測定から得られる特定結晶格子面の面間隔において、0.3μmのX線侵入深さにおける面間隔d1と5μmのX線侵入深さにおける面間隔d2とから得られる|d1−d2|/d2の値で表される結晶基板の表面層の均一歪みが1.7×10-3以下であり、主表面の面方位が、結晶基板のc軸を含む面から[0001]方向に−10°以上10°以下の傾斜角を有する。

(もっと読む)

プラズマ処理装置および方法

【課題】TSV(Through Silicon Via hole)加工用の薄化Si基板の支持ガラスの熱伝導効率を上げることで、加工処理速度や、成膜速度、膜質を向上させる。

【解決手段】凹部16と凸部17からなる凹凸パターン15を裏面12側に形成した、再利用可能な支持ガラス基板11の表面13側に接着剤24で貼り合わせた薄化半導体基板19をESC電極2上に載置することによって前記半導体基板19の冷却を促進し、TSV加工速度を向上させる。

(もっと読む)

CdTe系半導体基板の製造方法及びCdTe系半導体基板

【課題】良質なエピタキシャル結晶を成長可能なエピタキシャル成長用のCdTe系半導体基板の製造方法及びCdTe系半導体基板を提供する。

【解決手段】所定の半導体をエピタキシャル成長させるためのCdTe系半導体基板の製造方法において、基板表面を鏡面研磨した後又はエッチングした後、24時間以内に非酸化性ガス雰囲気中で保管する。これにより、原子間力顕微鏡で基板表面を観察したときに10μm×10μmの視野範囲内に高さ5nm以上の突起が観察されないCdTe系半導体基板が実現される。

(もっと読む)

GaN単結晶基板およびその製造方法、ならびにGaN系半導体デバイスおよびその製造方法

【課題】大口径で主面の面方位が(0001)および(000−1)以外で主面内におけるキャリア濃度の分布が実質的に均一であるGaN単結晶基板およびその製造方法を提供する。

【解決手段】本GaN単結晶基板20pは、主面20pmの面積が10cm2以上であり、主面20pmの面方位が(0001)面または(000−1)面20cに対して65°以上85°以下で傾斜しており、主面20pm内におけるキャリア濃度の分布が実質的に均一、たとえば主面20pm内において平均キャリア濃度に対するキャリア濃度のばらつきが±50%以内である。

(もっと読む)

III族窒化物結晶およびその製造方法

【課題】{0001}以外の面方位の主面を有する結晶性の高いIII族窒化物結晶を高い結晶成長速度で成長させるIII族窒化物結晶の製造方法を提供する。

【解決手段】本III族窒化物結晶の製造方法は、III族窒化物バルク結晶1から、{20−21}、{20−2−1}、{22−41}および{22−4−1}からなる群から選ばれるいずれかの結晶幾何学的に等価な面方位に対するオフ角が5°以下の面方位を有する主面10pm,10qmを有する複数のIII族窒化物結晶基板10p,10qを切り出す工程と、基板10p,10qの主面10pm,10qmが互いに平行で、かつ、基板10p,10qの[0001]方向が同一になるように、横方向に基板10p,10qを互いに隣接させて配置する工程と、基板10p,10qの主面10pm,10qm上にIII族窒化物結晶20を成長させる工程と、を含む。

(もっと読む)

半導体ウェハの製造方法

【課題】半導体ウェハの裏面の定義されたかつ有利な特性を有する半導体ウェハを提供すること

【解決手段】a) シリコン棒をウェハに切断することにより半導体ウェハを準備する工程、b) 前記半導体ウェハのエッジを丸めることで、前記半導体ウェハは前面及び裏面が平坦な面とエッジ領域で丸められかつ傾斜する面とを有する工程、c) 前記半導体ウェハの前面及び裏面を研磨し、前記前面の研磨は、研磨パッド中に固定された砥粒を有していない研磨パッドを使用する化学機械的研磨を有し、前記半導体ウェハの裏面の研磨は、それぞれ研磨パッド中に結合された研磨材料を有する研磨パッドを使用してかつ前記半導体ウェハの裏面に研磨圧力を加える3つの工程で行い、第1の工程では、固体を有していない研磨剤を前記研磨パッドと前記半導体ウェハの裏面との間に導入し、第2及び第3の工程では研磨材料を有する研磨剤を導入し、第1の及び第2の工程の8〜15psiの研磨圧力を、第3の工程では0.5〜5psiに低下させる工程を有する半導体ウェハの製造方法

(もっと読む)

シリコンウェーハ及びその製造方法、並びに、半導体デバイスの製造方法

【課題】デバイス後工程で薄型化され、且つ、裏面研磨される半導体デバイス用として好適なシリコンウェーハを提供する。

【解決手段】ボロン濃度に基づく比抵抗が2mΩ・cm以上200mΩ・cm以下であり、初期酸素濃度が7×1017atoms/cm3以上2.4×1018atoms/cm3以下であるシリコン基板11を用意する工程S11aと、シリコン基板11の内部に酸素を析出させる工程S12aと、シリコン基板11に膜厚が10μm以下のエピタキシャル膜12を形成する工程S14aとを備える。これにより、デバイス後工程でシリコン基板11の裏面を研削することによってチップを薄型化し、さらに裏面研磨を施したとしても、デバイス後工程で導入されうる重金属汚染に対して十分なゲッタリング能力を発揮することができる。

(もっと読む)

エピタキシャルウェハの製造方法、欠陥除去方法およびエピタキシャルウェハ

【課題】膜厚分布が均一なエピタキシャル膜を有するとともに、平坦度に優れたエピタキシャルウェハを簡単な工程で製造することのできるエピタキシャルウェハの製造方法およびエピタキシャルウェハを提供すること。

【解決手段】CZ法により得られたシリコン単結晶インゴットを薄円板状に切り出してウェハを得る(ステップS1)。次に、ウェハの表面を研削(ラッピング)して平面化する(ステップS2)。次に、エッチングによる化学研磨を行った(ステップS3)後、ウェハの両面を粗研磨する(ステップS4)。粗研磨終了後、気相エッチングを行い(ステップS5)、その後、エピタキシャル膜を形成する(ステップS6)。そして、エピタキシャル膜が形成されたウェハに対して仕上げ研磨を行い(ステップS7)、最終洗浄を行った(ステップS8)後、終了する。

(もっと読む)

化合物半導体基板及び半導体デバイス

【課題】 エピタキシャル層と基板との界面における電気抵抗の低減が図られた化合物半導体基板及び半導体デバイスを提供する。

【解決手段】 本発明に係る化合物半導体基板10は、III族窒化物で構成され、Cl換算で200×1010個/cm2以上12000×1010個/cm2以下の塩化物及びO換算で3.0at%以上15.0at%以下の酸化物を含む表面層12を表面に有する。発明者らは、鋭意研究の末、化合物半導体基板10の表面の表面層12に、Cl換算で200×1010個/cm2以上12000×1010個/cm2以下の塩化物及びO換算で3.0at%以上15.0at%以下の酸化物が含まれるときに、化合物半導体基板10とその上に形成されるエピタキシャル層14との間の界面のSiが低減され、その結果界面における電気抵抗が低減されることを新たに見出した。

(もっと読む)

III族窒化物結晶基板、エピタキシャル層付III族窒化物結晶基板および半導体デバイス

【課題】半導体デバイスに用いることができる平滑で加工変質層が薄いIII族窒化物結晶基板およびエピタキシャル層付III族窒化物結晶基板の基板、ならびにかかるIII族窒化物結晶基板を含む半導体デバイスを提供する。

【解決手段】半導体デバイス400の基板410として用いられ、1層以上のIII族窒化物層をエピタキシャル成長させるためのIII族窒化物結晶基板410であって、表面粗さRaが0.5nm以下であり、かつ加工変質層の厚さが50nm以下、表面酸化層の厚みが3nm以下で、記III族窒化物結晶基板の主面と、ウルツ鉱型構造におけるC面、A面、R面、M面およびS面のいずれかの面とのなす角であるオフ角が、0.05°以上15°以下である。

(もっと読む)

エピタキシャルシリコンウェーハおよびその製造方法

【課題】450mm以上の大口径ウェーハの表面のみにエピタキシャル膜を成長させた際に、ウェーハの反りを低減可能で、かつ高いエクストリンシックゲッタリング能力も得られるエピタキシャルシリコンウェーハおよびその製造方法を提供する。

【解決手段】直径が450mm以上、比抵抗値が0.1Ω・cm以上の大口径で高抵抗のシリコンウェーハ11の裏面に、エクストリンシックゲッタリング層を形成したので、エピタキシャルシリコンウェーハの反りを低減でき、高いゲッタリング能力が得られる。しかも、ドーパントがウェーハ裏面から外方拡散してデバイス形成面のエピタキシャル膜へ回り込むことで生じるオートドープ現象も抑制できる。

(もっと読む)

エピタキシャルシリコンウェーハおよびその製造方法

【課題】450mm以上の大口径ウェーハの表面のみにエピタキシャル膜を成長させた際に、ウェーハの反りを低減可能で、かつ高いイントリンシックゲッタリング能力も得られるエピタキシャルシリコンウェーハおよびその製造方法を提供する。

【解決手段】直径が450mm、比抵抗値が0.01Ω・cm以上0.1Ω・cm未満の大口径シリコンウェーハ11に、インゴット引き上げ時のシリコン溶融液56への窒素導入によるイントリンシックゲッタリング構造を形成したので、エピタキシャル膜12の成長後、シリコンウェーハ11に大きな反りが発生しにくい。その結果、エピタキシャルシリコンウェーハ10の反りを低減でき、しかも高いイントリンシックゲッタリング能力が得られる。

(もっと読む)

シリコンエピタキシャルウェーハ及びその製造方法

【課題】{110}面の傾斜角度が小さくてもヘイズレベルが良好なウェーハを提供する。

【解決手段】{110}面を主面とし、{110}面のオフアングルが1度未満のシリコン単結晶基板にエピタキシャル層を成長させる工程と、前記エピタキシャル層表面のヘイズレベル(SP2,DWOモードで測定)が0.18ppm以下であって、輝点欠陥LPDがヘイズの影響なく測定できるように、前記エピタキシャル層の表面を30℃〜90℃の温フッ化アンモニウム溶液で処理する工程と、を備える。

(もっと読む)

III族窒化物半導体基板およびその洗浄方法

【課題】ダングリングボンド密度が14.0nm-2よりも大きくて平坦な面を有するIII族窒化物半導体基板を提供する。

【解決手段】III族窒化物半導体基板を構成するダングリングボンド密度が14.0nm-2より大きい面を、アンモニウム塩を含む洗浄剤で洗浄する。

(もっと読む)

シリコンエピタキシャルウェーハとその製造方法

【課題】エピタキシャルウェーハにおいて、少なくともデバイス特性に悪影響を及ぼさない高品質なエピタキシャル表面品質を得るために、エピタキシャルウェーハ用として最適な低COPの基板を効率よく製造でき、高品質エピタキシャルウェーハを歩留りよく製造できる製造方法の提供。

【解決手段】炭素濃度を0.3×1016〜3.2×1017atoms/cm3 (NEW ASTM)の範囲に添加、制御させることによって、COPの発生が低減、抑制され、特に、その後のエピタキシャル成長によっても消滅し難い0.130μm以上のCOPの発生を頭著に低減、抑制でき、従来の結晶の生産性低下を招く低速引き上げを行うことなく、COP発生を低減抑制できる。

(もっと読む)

窒化物半導体基板、窒化物半導体レーザ素子、窒化物半導体基板の製造方法、および窒化物半導体レーザ素子の製造方法

【課題】レーザ発振寿命の長い窒化物半導体レーザ素子に適した窒化物半導体基板を提供する。

【解決手段】窒化物半導体基板は、断面をV字状にした溝の側面である斜面をファセット面とし、そのファセット面の斜面を維持させながら成長させることにより、溝に転位を集中させた上にストライプ状に生じた転位集中領域と、転位集中領域を除いた領域である低転位集中領域と、を含み、さらに、その窒化物半導体基板の表面が、(0001)面から0.2°〜1°の範囲のオフ角度を有している。

(もっと読む)

1 - 20 / 26

[ Back to top ]