Fターム[5F048BB07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558) | P型ドープ多結晶Si (956)

Fターム[5F048BB07]に分類される特許

941 - 956 / 956

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

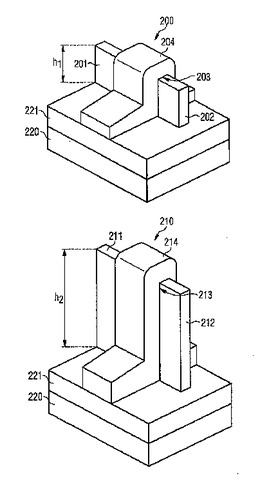

Fin電界効果トランジスタの配列及びFin電界効果トランジスタの配列の形成方法

本発明は、基板と、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第1のFin電界効果トランジスタと、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、当該フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第2のFin電界効果トランジスタとを備えた、Fin電界効果トランジスタ配置に関する。上記第1のFin電界効果トランジスタのフィンの高さは、上記第2のFin電界効果トランジスタのフィンの高さよりも高くなっている。  (もっと読む)

(もっと読む)

CMOSシリサイド金属ゲート集積化

本発明は、ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。本発明の集積化方式を用いて形成される各シリサイド金属ゲートは、シリサイド金属ゲートの寸法に関わりなく、同じシリサイド金属相および実質的に同じ高さを有する。本発明は、半導体構造物の表面全体にわたってポリSiゲート高さが実質的に同じであるシリサイド接点を有するCMOS構造物を形成するさまざまな方法も提供する。

(もっと読む)

(もっと読む)

垂直型FIN−FETMOSデバイス

【課題】 トランジスタ本体として働く垂直方向のシリコン「フィン」を用いて、低い接触抵抗を持つ高密度の垂直型Fin−FETデバイスを生成すること。

【解決手段】 低い接触抵抗を示す新しいクラスの高密度の垂直型Fin−FETデバイスが説明される。これらの垂直型Fin−FETデバイスは、トランジスタ本体として働く垂直方向のシリコン「フィン」(12A)を有する。ドープされたソース領域及びドレイン領域(26A、28A)が、それぞれフィン(12A)の下部及び上部内に形成される。ゲート(24A、24B)が、フィンの側壁に沿って形成される。適切なバイアスがゲート(24A、24B)に印加されると、電流は、ソース領域(26A)とドレイン領域(28A)との間で、フィン(12A)を通して垂直方向に流れる。pFET、nFET、マルチ・フィン、シングル・フィン、マルチ・ゲート、及びダブルゲートの垂直型Fin−FETを同時に形成するための統合プロセスが説明される。

(もっと読む)

直流ノード拡散領域の下に埋め込み酸化物を有さず、酸化物ホールを有する差別化SOI構造

直流ノード拡散領域の下に埋め込み酸化物を設けず、すべてのデバイスのための本体接触部を有する選択的SOI構造を提供する。印加電圧Vdd、接地GND、基準電圧Vrefおよびその他の類似DCノードなどのDCノード拡散領域の直下に存在する埋め込み酸化物を設けずに、すべてのデバイスのための本体接触部を有する選択的SOI構造を提供する。本発明の選択的SOI構造をIC中に用いて回路の性能を改善することができる。本発明の選択的SOI構造は、上に配置された複数のSOIデバイスを有する上部Si含有層を備える絶縁体上シリコン(SOI)基板材料を含む。本SOIデバイスは、本体接触部領域を介して下地のSi含有基板と接触する。下地の埋め込み酸化物領域を備えないDCノード拡散領域がSOIデバイスの一つに隣接する。

(もっと読む)

(もっと読む)

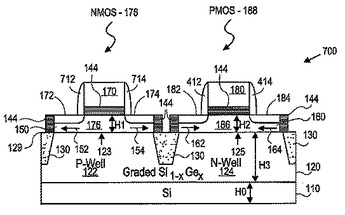

CMOS用歪トランジスタの集積化

【解決手段】CMOSデバイスに関連する本発明の様々な実施形態は、(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

(もっと読む)

半導体装置および半導体集積回路装置

pチャネルMOSトランジスタおよびnチャネルMOSトランジスタの各々においてチャネル方向を<100>方向に設定し、STI型素子分離構造に、引っ張り応力を蓄積した第1の応力補償膜を形成し、さらにシリコン基板上に素子分離構造を覆うように引っ張り応力を蓄積した第2の応力補償膜を形成する。 (もっと読む)

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

high−kゲート誘電体と関連の構造を有するCMOSゲートを形成するための、異なる仕事関数を有する金属を統合する方法

1つの一般的な実施形態では、デュアルメタルのNMOSゲート(226)とPMOSゲート(228)を形成するために、基板(202)上に第1金属層(206)と第2金属層(208)を統合するための方法として、基板(202)のNMOS領域(210)とPMOS領域(212)上に誘電体層(204)を堆積する。更に、本方法は、誘電体層(204)上に第1金属層を堆積する。更に、方法は、第1金属層(206)上に第2金属層(208)を堆積する(150)。更に、本方法は、基板(202)のNMOS領域(210)に窒素を注入し(152)、第1金属層(206)の第1部分を金属酸化物層(220)に変え(154)、第1金属層(206)の第2部分を金属窒化物層(218)に変える。更に、本方法は、NMOSゲート(226)とPMOSゲート(228)を形成し(156)する。NMOSゲート(226)は金属窒化物層(218)のセグメント(234)を含み、PMOSゲート(228)は金属酸化物層(220)のセグメント(242)を含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

並列接続されているトランジスタTr1、Tr2、Tr3のゲート電極1−1、2−1、3−1のゲート幅、及び、隣接し合うゲート電極間の距離が異なり、また、ソース領域やドレイン領域の対応するゲート電極のゲート幅に沿う方向の長さや面積がトランジスタTr1、Tr2、Tr3で種々異なる値を持っている。したがって、同一のトランジスタ群内のトランジスタTr1、Tr2、Tr3間でゲート長などの特性の相関が低下し、それによって、複数のトランジスタ群間における特性のばらつきが小さくなる。  (もっと読む)

(もっと読む)

同じ半導体チップ内のPMOSおよびNMOSトランジスタの薄いゲート誘電体を個々に最適化する方法、およびそれによって製造されたデバイス

【課題】半導体基板(12)に形成され、シリコン酸化物およびそれの異なる程度の窒化(18Dと18E)で構成されたPFETゲート誘電体層(16)およびNFETゲート誘電体層(14)でそれぞれ覆われたPFET領域およびNFET領域を有するCMOS半導体(10)材料を形成する方法を提供すること

【解決手段】シリコン基板(12)にPFET領域(16)およびNFET領域(14)を設け、その上にPFETおよびNFETゲート酸化物層を形成する。PFET領域の上のPFETゲート酸化物層の窒化を行って、PFET領域の上のPFETゲート酸化物層に、第1の濃度レベルの窒素原子を有する、PFET領域の上のPFETゲート誘電体層(42)を形成する。NFETゲート酸化物層の窒化を行って、第1の濃度レベルと異なる濃度レベルの窒素原子を有する、NFET領域の上のNFETゲート誘電体層(40)を形成する。NFETゲート誘電体層(40)およびPFETゲート誘電体層(42)は、同じ厚さを有することができる。

(もっと読む)

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

格子不整合エピタキシャル拡張領域ならびにソースおよびドレイン領域を有するひずみチャネルCMOSトランジスタ構造体およびその製造方法

【課題】n型電界効果トランジスタ(NFET)およびp型電界効果トランジスタ(PFET)がそれぞれ、第1の半導体の単結晶層内に配置されたチャネル領域を有し、PFETのチャネル領域には第1の大きさの応力が加えられているが、NFETのチャネル領域にはその大きさの応力が加えられていない構造体およびその製造方法を提供すること。

【解決手段】この応力は、第1の半導体とは格子不整合の第2の半導体の層によって加えられる。この第2の半導体の層は、PFETのソースおよびドレイン領域ならびに拡張領域の上の、PFETのチャネル領域から第1の距離のところに形成されており、この第2の半導体の層は、NFETのソースおよびドレイン領域の上の、NFETのチャネル領域からより大きな第2の距離のところにも形成されており、またはNFETには全く形成されていない。

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

格子不整合のソースおよびドレイン領域を有する歪み半導体CMOSトランジスタを有する集積回路および製作方法

【課題】 p型電界効果トランジスタ(PFET)およびn型電界効果トランジスタ(NFET)を有する集積回路を提供することにある。

【解決手段】 第1の歪みは、NFETではなくPFETのみのソースおよびドレイン領域内に配置されたシリコン・ゲルマニウムなどの格子不整合半導体層を介してNFETではなくPFETのチャネル領域に加えられる。PFETおよびNFETを形成するプロセスが提供される。PFETのソースおよびドレイン領域になるためのエリア内にトレンチがエッチングされ、それに隣接するPFETのチャネル領域に歪みを加えるために、格子不整合シリコン・ゲルマニウム層をそこにエピタキシャル成長させる。シリコン・ゲルマニウム層の上にシリコンの層を成長させ、シリコンの層からサリサイドを形成して、低抵抗ソースおよびドレイン領域を提供することができる。

(もっと読む)

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

941 - 956 / 956

[ Back to top ]