Fターム[5F048BC15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 材料 (764)

Fターム[5F048BC15]の下位に属するFターム

多結晶Si(SOI) (345)

Fターム[5F048BC15]に分類される特許

201 - 220 / 419

半導体装置及びその製造方法

【課題】ゲート電極をフルシリサイド化したMISFETを有する半導体装置及びその製造方法に関し、MISFETの特性劣化を引き起こすことなくゲート電極をフルシリサイド化しうる半導体装置の製造方法、並びに、そのような製造方法を用いて形成された優れた特性のMISFETを有する半導体装置を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜18と、ゲート絶縁膜18上に形成された金属シリサイド膜56bと、金属シリサイド膜56b上に形成された金属シリサイド膜56aとを有し、金属シリサイド膜56bにおける金属元素に対するシリコンの組成が、金属シリサイド膜56aにおける金属元素に対するシリコンの組成よりも大きいゲート電極26nと、ゲート電極26nの両側の半導体基板10内に形成された不純物拡散領域対54とを含むトランジスタを有する。

(もっと読む)

半導体装置の製造方法

【課題】バッチ式の反応炉を用いた場合でも、安定した特性を得ることができる半導体装置の製造方法を提供する。

【解決手段】供給ラインに原料ガスを流し始める(ステップS2)。供給ラインからMFCを通過した原料ガスは排気ラインに流れ、炉内供給ラインには流れない。その後、MFCを流れる原料ガスの流量が安定したかを判定する(ステップS3)。例えば、流量の変動幅が所定の範囲内に収まっているか判定する。流量が安定すると、バルブV1を開くと共に、バルブV2を閉じる(ステップS4)。この結果、供給ラインからMFCを通過した原料ガスは排気ラインに流れなくなり、炉内供給ラインに流れるようになる。続いて、所定時間が経過したかを判定する(ステップS5)。この所定時間は、形成しようとしているSiGe層の成長に必要とされる時間である。所定時間が経過すると、バルブV1を閉じると共に、バルブV2を開く(ステップS6)。

(もっと読む)

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

有機薄膜トランジスタおよびその製造方法

【課題】有機TFTにおいて、電子注入効率とホール注入効率を改善した電極と有機半導体の組み合わせをそれぞれ判別する手法を提供し、また、n型チャネルTFTとp型チャネルFETの2種類のTFTを実現し、さらに、相補型有機薄膜トランジスタ(有機CTFT)および、有機CTFTによる所望の任意回路構成を形成する有機CTFTアレイを提供する。

【解決手段】半導体−電極界面、および、半導体−ゲート絶縁体界面におけるフェルミエネルギーの差の大きさを与える数式を用いて、TFT材料を変えずに電極および絶縁膜の表面修飾だけを選択的に変化してn型とp型のTFTを実現する。任意回路を構成するために、p型チャネルTFT用のソース電極とゲート電極、および、n型チャネルTFT用のドレイン電極とゲート電極をすべてつないでおいて、表面修飾のプロセスを行い、その後、光照射などにより不要配線を切断する。

(もっと読む)

半導体装置の製造方法

【課題】

深さ方向の圧縮応力を印加して、NMOSトランジスタの性能を向上した半導体装置を提供する。

【解決手段】

CMOS型半導体装置用シリコン基板のNMOSトランジスタ領域、PMOSトランジスタ領域上方に多結晶シリコンのゲート電極を形成し、ゲート電極側壁上に第1サイドウォールスペーサを形成し、NMOSトランジスタ領域、PMOSトランジスタ領域に選択的にイオン注入を行ない、第1サイドウォールスペーサに整合した低抵抗ソース/ドレイン領域を形成する際、NMOSトランジスタ領域においてはゲート電極の上部をアモルファス化し、少なくともNMOSトランジスタ領域において第1サイドウォールスペーサを実質的に除去し、ゲート電極を覆ってキャップ膜を形成し、低抵抗ソース/ドレイン領域の活性化を行うと共にアモルファス化されたゲート電極の再結晶化を行う熱処理を行ない、キャップ膜を異方性エッチングして第2サイドウォールスペーサに加工する。

(もっと読む)

半導体装置

【課題】良好な特性を得ながら、小型化、高耐圧化および低消費電力化が可能な半導体装置を提供する。

【解決手段】この半導体装置1は、シリコンよりも大きいバンドギャップを有し、パワートランジスタ2が形成されたSiC層11と、SiC層11の主表面11aよりも上側の所定領域に形成されるとともに、制御回路用のNMOSトランジスタ3およびPMOSトランジスタ4が形成され、SiC層11とは別の層からなるシリコン層21と、SiC層11のパワートランジスタ2とシリコン層21のNMOSトランジスタ3およびPMOSトランジスタ4とを接続するAl配線5とを備える。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極、ソース電極またはドレイン電極にタングステン膜を用いた半導体装置において、nMOSとpMOS間での抵抗差を低減可能な半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極14a,14bとソース/ドレイン拡散層16a,16bとを有するnMOS及びpMOSを形成し、ゲート電極14a,14b及びソース/ドレイン拡散層16a,16b上に、タングステン膜17を選択的に形成し、タングステン膜17を覆うように、絶縁膜(エッチングストップシリコン酸化膜18、シリコン窒化膜19)を形成し、pMOS領域12bの絶縁膜を除去し、pMOS領域12bのタングステン膜17上に、タングステン膜20を選択的に形成する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、これらの問題を解決するためになされたもので、半導体装置の微細化に影響することなく、同一基板上で異なる極性の領域において各々の特性を向上させる処理が可能な半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明による半導体装置の製造方法は、第1領域全体と第2領域全体とを全面に覆うサイドウォール下地膜9を形成する工程と、サイドウォール下地膜9上であって第1ゲート構造および第2ゲート構造の側面にサイドウォール膜10を形成する工程と、第1領域全体と第2領域全体とを全面に覆うカバー膜11を形成する工程と、第2領域において、サイドウォール下地膜9およびカバー膜11を除去し、サイドウォール膜10に覆われたサイドウォール下地膜9のみ残す工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】歪み発生層に緩和が生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極15と、ゲート電極15の両側面上に形成され、断面L字状の内側サイドウォール17Bと、半導体基板11におけるゲート電極15の両側方の領域に埋め込まれた歪み発生層19とを備えている。内側サイドウォール17Bは、5×1019/cm3以上の炭素を含む炭素含有シリコン酸化膜からなる。歪み発生層19は、1%以上の炭素を含む炭素含有シリコンエピタキシャル層を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】電極の接触抵抗の低減によって高性能化した半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体基板上に第1の金属を堆積する工程と、第1の熱処理により第1の金属と半導体基板を反応させて、前記ゲート電極両側の前記半導体基板表面に金属半導体化合物層を形成する工程と、金属半導体化合物層中に、Siの原子量以上の質量を有するイオンをイオン注入する工程と、金属半導体化合物層上に第2の金属を堆積する工程と、第2の熱処理により、第2の金属を金属半導体化合物層中に拡散させることで、金属半導体化合物層と半導体基板の界面に、第2の金属を偏析させて界面層を形成する工程を有することを特徴とする半導体装置の製造方法。

(もっと読む)

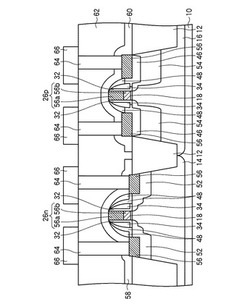

半導体装置及びその製造方法

【課題】n型MISトランジスタのゲート電極、及びp型MISトランジスタのゲート電極の双方を精度良く実現する。

【解決手段】第1のMISトランジスタと第2のMISトランジスタとを備えた半導体装置において、第1のMISトランジスタは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され、シリコン膜14aとシリコン膜14a上に形成された第1の金属シリサイド膜20aとからなる第1のゲート電極26aとを備え、第2のMISトランジスタは、半導体基板10における第2の活性領域10b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜13b上に形成され、フルシリサイド化された第2の金属シリサイド膜20Bからなる第2のゲート電極26bとを備え、第1の金属シリサイド膜20aは、第2の金属シリサイド膜20Bに比べて膜厚が薄い。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層における転位の発生を抑止しトランジスタのロールオフ特性を十分に確保しつつも、チャネル領域への歪み量を増加させて電流駆動能力を大幅に向上させて動作速度を増大させる。

【解決手段】SiGe層103は、第1のSiGe層103aと、第1のSiGe層103a上に形成され、Si又は第1のSiGe層103aよりもGe濃度の低い中間層103cと、第1のSiGe層103a上に中間層103cを介して形成され、第1のSiGe層103aよりもGe濃度の高い第2のSiGe層103bと、第2のSiGe層103b上に形成され、Si又は第1のSiGe層103aよりもGe濃度の低い上層103d有して構成される。

(もっと読む)

半導体基板、及びその製造方法

【課題】DSB基板を用いてHOT構造の半導体基板を作製するに際し、その機能性基板の、互いに異なる結晶方位を有する結晶領域の境界における結晶欠陥の発生を抑制し、本来的な実用に足る前記HOT構造の半導体基板を提供する。

【解決手段】第1の結晶方位を有するシリコン支持基板と、このシリコン支持基板上に直接的に形成され、前記シリコン支持基板の前記第1の結晶方位と異なる結晶方位を有する第1の結晶領域と、前記シリコン支持基板の前記第1の結晶方位と異なる結晶方位を有する第2の結晶領域とを有するシリコン機能性基板とを具えた半導体基板において、前記シリコン機能性基板の、前記第1の結晶領域及び前記第2の結晶領域の境界に、少なくとも前記シリコン支持基板の主面にまで達するような溝部を形成する。

(もっと読む)

半導体装置

【課題】チャネル領域における高いキャリア移動度を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成され、内部におけるキャリアの移動度がSi結晶よりも大きい第1の結晶からなる半導体層と、前記半導体層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層を挟んで形成され、前記半導体層に前記半導体層内のキャリアの移動度が上昇する方向に歪みを与える第2の結晶を含み、前記半導体層に接する深さの浅い領域であるソース・ドレインエクステンション領域を有するソース・ドレイン領域と、を有する。

(もっと読む)

配置配線システムにおける設計最適化のためのフィラーセル

集積回路設計において、複数の回路レイアウトセルを相互の間に間隙を設けてレイアウトし、前記間隙の少なくとも一部の所定の間隙の夫々に、前記所定の間隙に隣接する少なくとも1つの回路レイアウトセルの性能パラメータに対して所望される影響に基づいて所定のデータベースから選択された対応するフィラーセルを挿入するためのシステム及び方法を提供する。前記回路レイアウトセルは複数行にわたって配列されており、幾つかの実施形態では、所定の間隙に対する適切なフィラーセルの選択は、前記所定の間隙の両側に隣接する回路レイアウトセルの性能パラメータに依存する。前記所定のフィラーセルは、例えば、ダミー拡散領域、ダミーポリシリコン線、Nウェル境界の移動、エッチング停止層境界の移動を備える。一実施形態では、回路レイアウトセルは、選択されたフィラーセルを収容するために移動させることができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域における歪みを適正に増大させ、キャリア注入速度を向上させて、近時における更なる狭チャネル化にも対応したトランジスタ特性の大幅な向上を可能とする信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極101の側面に、自身は膨張性を有する応力膜からなる第1のサイドウォール111と、第1のサイドウォール111上にこれに比して応力の小さい膜からなる第2のサイドウォール112とが形成されており、半導体層、例えばSiC層104が第2のサイドウォール112により第1のサイドウォール111から離間する。

(もっと読む)

半導体装置の製造方法

【課題】応力源となるSiGe混晶層のエピタキシャル成長の際に生じる、ポリシリコンゲート電極パターン上のSiGe混晶異常成長を抑制する半導体装置製造方法の提供。

【解決手段】pチャネルMOSトランジスタの製造方法は、(A)シリコン単結晶基板表面に、ゲート絶縁膜22A,22Bを介してポリシリコンゲート電極23A,23Bを、上面に絶縁膜が形成された状態で形成する工程と、(B)ゲート電極の合対向する側壁面に、側壁絶縁膜を形成する工程と、(C)基板表面を、各側壁面外側においてエッチングし、溝部を形成する工程と、(D)溝部にそれぞれSiGe領域を、基板に対してエピタキシャルに成長させる工程と、を含み、さらに工程(B)の後で工程(D)の前に、ポリシリコンゲート電極に不純物元素をイオン注入法により導入し、ポリシリコンゲート電極の少なくとも上部をアモルファス状態に変化させる工程(E)を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】歪み技術を適用した半導体装置のシリサイド化に起因したリーク電流の発生を抑制する。

【解決手段】半導体基板2の素子分離領域3で画定された素子領域20上に、ゲート絶縁膜5を介してゲート電極6を形成し、そのゲート電極6の両側の素子領域20内に、エクステンション領域8およびソース・ドレイン領域9を形成すると共に、半導体基板2と格子定数の異なる半導体層10を素子分離領域3の少なくとも一部と離間して形成する。これにより、シリサイド層11の形成を行った場合にも、素子分離領域3の近傍でのスパイクの形成が抑えられ、そのようなスパイクに起因したリーク電流の発生が抑えられるようになる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】チャネルのサイズおよび形状の揺らぎを可及的に抑制するとともに、チャネルの幅が可及的に小さい電界効果トランジスタを提供することを可能にする。

【解決手段】Siを含む半導体層を上面に備えた半導体基板4上に、絶縁膜のマスク9を形成する工程と、マスクを用いてエッチングを行うことにより半導体層を半導体基板の上面に平行な一方向に延在するメサ状に加工する工程と、水素雰囲気中での熱処理を行うことにより、半導体層の一方向に延在しかつ対向する一対の側面間の距離を狭くするとともに側面を平坦化する工程と、側面が平坦化された半導体層を覆うゲート絶縁膜12を形成する工程と、ゲート絶縁膜を覆うゲート電極13を形成する工程と、ゲート電極の両側の半導体層にソース/ドレイン領域を形成する工程と、を備えている。

(もっと読む)

半導体装置

【課題】本発明は、MOSトランジスタの電流駆動能力をより向上させることができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1、PMOSトランジスタP1、およびSiC層10を備えている。半導体基板1は、シリコンから成る。PMOSトランジスタP1は、半導体基板1の上面内に形成される。SiC層は、PMOSトランジスタP1のチャネル領域の下方から、PMOSトランジスタP1を構成する電極領域内若しくは電極領域下に渡って、形成される。

(もっと読む)

201 - 220 / 419

[ Back to top ]