Fターム[5F048BC15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 材料 (764)

Fターム[5F048BC15]の下位に属するFターム

多結晶Si(SOI) (345)

Fターム[5F048BC15]に分類される特許

121 - 140 / 419

半導体装置及びその製造方法

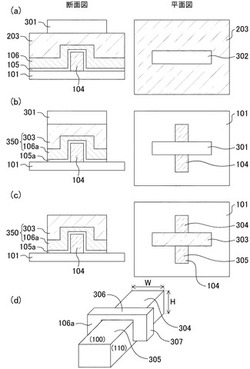

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】p型ソースドレイン領域内にシリコン混晶層が形成されていると、N型MISトランジスタのキャリア移動度が低下する虞があった。

【解決手段】活性領域10aと活性領域10bとが素子分離領域11により分離されており、活性領域10a上には第1導電型の第1のトランジスタが設けられており、活性領域10b上には第2導電型の第2のトランジスタが設けられている。活性領域10b内には、第1の応力を有するシリコン混晶層21が設けられている。素子分離領域11のうち活性領域10aと活性領域10bとで挟まれた部分の上面には凹部22が設けられている。凹部23内には応力絶縁膜24が設けられており、応力絶縁膜24は第1の応力とは反対方向の第2の応力を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

MOSトランジスタ及びMOSトランジスタを備えた半導体装置の製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上部のシリサイドの細線効果を低減すること、また、シリサイドと上部拡散層間の界面抵抗を低減することによりトランジスタ特性を改善すること、またコンタクトとゲート間のショートが発生しない構造を実現すること。

【解決手段】柱状半導体層と、前記柱状半導体層の底部に形成される第1のドレイン又はソース領域と、該柱状半導体層の側壁を包囲するように第1の絶縁膜を介して形成されるゲート電極と、前記柱状半導体層上面上部に形成されるエピタキシャル半導体層とを含み、前記第2のソース又はドレイン領域が少なくとも前記エピタキシャル半導体層に形成され、前記第2のソース又はドレイン領域の上面の面積は、前記柱状半導体層の上面の面積よりも大きいことを特徴とするMOSトランジスタ。

(もっと読む)

半導体装置およびその製造方法

【課題】薄膜BOX−SOI基板に形成される電界効果型トランジスタの信頼性および動作特性の劣化を防ぐことのできる技術を提供する。

【解決手段】薄膜BOX−SOI基板の主面上に所定の間隔で配置されたnウェルnwおよびpウェルpwが形成されており、pウェルpwに形成されたnMIS1nは、SOI層1iの主面上に所定の距離を隔てて積み上げられた半導体層に形成された一対のn型ソース・ドレイン領域2nと、一対のn型ソース・ドレイン領域2nに挟まれたゲート絶縁膜3、ゲート電極4、およびサイドウォール5とを有しており、nウェルnwとpウェルpwとの間に素子分離10を形成し、素子分離10の側端部が、n型ソース・ドレイン領域2nの側端部(BOX層1bの側壁部)よりもゲート電極4側に広がっている。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】微結晶シリコンをチャンネル領域として用い、良好にリーク電流を抑制することが可能な薄膜トランジスタ及びその製造方法を提供する。

【解決手段】薄膜トランジスタ100は、図1に示すように、基板11と、ゲート電極112と、ゲート絶縁膜113と、半導体層(チャンネル領域)114と、エッチングストッパ膜115と、高濃度不純物含有アモルファスシリコン層116,117と、ドレイン電極118と、ソース電極119と、低濃度不純物含有半導体層120,121を備える。微結晶シリコンを用いたチャンネル領域114と、高濃度不純物含有アモルファスシリコン層116及び/又は高濃度不純物含有アモルファスシリコン層117との間に低不純物濃度半導体層120,121を設けることにより、良好にリーク電流を抑制することができる。

(もっと読む)

半導体素子、半導体装置、半導体素子の製造方法、および半導体装置の製造方法

【課題】特定の領域において有機半導体の電荷タイプを変換する方法を提供する。

【解決手段】本発明に係る有機半導体素子の製造方法は、半導体層がキノイド構造を有するオリゴチオフェン化合物によって形成されている有機化合物層である半導体素子の製造方法であって、有機化合物層に対して、加熱処理、光照射処理および溶媒処理の少なくとも何れかの処理を施すことにより、有機化合物層のn型の特性、p型の特性または両極性型の特性を、n型の特性、p型の特性および両極性型の特性のうちの別の特性に変化させる工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極との短絡を抑えたセルフアラインコンタクトを有する、製造コストの低い半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、それぞれ半導体基板2上に形成され、それぞれゲート電極4a、4bを有し、互いの間のソース・ドレイン領域8aを共有する隣接したトランジスタ1a、1bと、ゲート電極4a上に形成された絶縁膜11aと、ゲート電極4b上に形成された絶縁膜11aよりも厚さの厚い領域を有する絶縁膜11bと、ソース・ドレイン領域8aに接続され、その中心位置がゲート電極4a、4bの間の中心位置よりもゲート電極4b側に位置するSAC14と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】nMOSFETのソース/ドレイン領域にはSiGeを埋め込まず、pMOSFETのソース/ドレイン領域にのみSiGeを再現性よく埋め込むことが可能な製造方法を提供する。

【解決手段】第1活性領域12と交差する第1ゲート電極21、及び第2活性領域13と交差する第2ゲート電極22を形成し、第1及び第2ゲート電極を覆うように、第1キャップ膜35を形成する。第1活性領域上の第1キャップ膜35を、エッチングして除去する。半導体基板全面に、第2キャップ膜を形成37する。第2活性領域上の第2キャップ膜37を第2マスクパターンで覆い、第1活性領域上の第2キャップ膜37をエッチングして除去する。第2活性領域を第1及び第2キャップ膜で覆った状態で、第1活性領域において、ソース/ドレイン領域をエッチングすることにより、凹部を形成する。凹部内を、埋込部材で埋め込む。

(もっと読む)

縦型論理素子

【課題】狭い面積で高速応答性の縦型半導体装置を提供する。

【解決手段】基板上に形成された第1の電極と、絶縁膜と、絶縁膜を介し第1の電極の側面の一方に形成された第1の導電型の第1の半導体層と、絶縁膜を介し第1の電極の側面の他方に形成された第2の導電型の第2の半導体層と、一部領域における第1の半導体層上に形成された第2の電極と、他の一部領域における第2の半導体層上に形成された第3の電極と、第1の電極の上層の第1の半導体層及び第2の半導体層上に形成された第4の電極とを有し、第2の電極と前記第4の電極間における第1の半導体層に第1のチャネル領域が形成され、第3の電極と前記第4の電極間における第2の半導体層に第2のチャネル領域が形成されるものであることを特徴とする縦型半導体装置を提供することにより上記課題を解決する。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域のエクステンション領域の不純物濃度プロファイルが急峻なp型トランジスタを有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1aは、半導体基板2上に形成された結晶層13と、結晶層13上にゲート絶縁膜14を介して形成されたゲート電極15と、半導体基板2と結晶層13との間に形成された、ゲート電極15の下方の領域において第1の不純物を含むC含有Si系結晶からなる不純物拡散抑制層12と、半導体基板2、不純物拡散抑制層12、および結晶層13内のゲート電極15の両側に形成され、結晶層13内にエクステンション領域を有する、p導電型を有する第2の不純物を含むp型ソース・ドレイン領域17と、を有し、C含有Si系結晶は第2の不純物の拡散を抑制する機能を有し、第1の不純物は、C含有Si系結晶内の固定電荷の発生を抑制する機能を有する。

(もっと読む)

SiGeチャネルを有するデュアル高K酸化物

PMOSデバイス領域112、113内にシリコンゲルマニウムチャネル層21を有する単一基板15にデュアルゲート酸化物(DGO)トランジスタデバイス50、52およびコアトランジスタデバイス51、53を集積するための方法および装置を記載する。各DGOトランジスタデバイス50、52は、金属ゲート25と、第2の相対的により高い高K金属酸化物層24から形成された上部ゲート酸化物領域60、86と、第1の相対的により低い高K誘電体層22から形成された下部ゲート酸化領域58、84とを含む。また、各コアトランジスタデバイス51、53は、金属ゲートと、第2の相対的により高い高K金属酸化物層24から形成されたコアゲート誘電層72、98とを含む。  (もっと読む)

(もっと読む)

論理回路及び半導体装置

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置及びその作製方法

【課題】大型の半導体装置で、高速に動作する半導体装置を提供することを目的する。

【解決手段】単結晶の半導体層を有するトップゲート型のトランジスタと、アモルファス

シリコン(またはマイクロクリスタルシリコン)の半導体層を有するボトムゲート型のト

ランジスタとを同一基板に形成する。そして、各々のトランジスタが有するゲート電極を

同じレイヤーで形成し、ソース及びドレイン電極も同じレイヤーで形成する。このように

して、製造工程を削減する。つまり、ボトムゲート型のトランジスタの製造工程に、少し

だけ工程を追加するだけで、2つのタイプのトランジスタを製造することが出来る。

(もっと読む)

半導体装置及びその製造方法

【課題】炭素含有シリコン領域を有するn型MISトランジスタを備えた半導体装置において、チャネル領域のゲート長方向に印加される引っ張り応力の大きさを、効果的に増大させる。

【解決手段】少なくともn型MISトランジスタNTrを有する半導体装置において、n型MISトランジスタnTrは、半導体基板10における第1の半導体領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール18Aと、第1のサイドウォール18Aの外側方に形成された炭素含有シリコン領域27とを備え、炭素含有シリコン領域27の上面高さは、第1の半導体領域10aにおける第1のゲート絶縁膜13aの下に位置する領域の上面高さよりも高い。

(もっと読む)

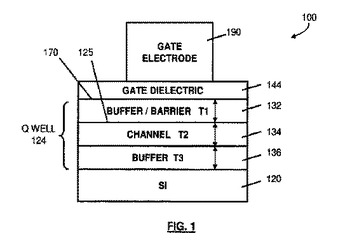

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】オフ状態でのリーク電流を抑制したMOSトランジスタを有する回路領域と、オン状態でのドレイン電流を大きいMOSトランジスタを有する回路領域と、を備えた半導体装置を提供する。

【解決手段】第1のMOSトランジスタは、第1の不純物領域として、半導体基板内に設けられた第1の領域及び第1の領域の上方に突出するように設けられた第2の領域からなる第1のソース/ドレイン領域を有する。第2のMOSトランジスタは、半導体基板内に設けられた第2の不純物領域と、第2の不純物領域に接触して半導体基板の上方に突出する第3の不純物領域と、第3の不純物領域上に第4の不純物領域とを有する第2のソース/ドレイン領域を有する。第3の不純物領域は、第4の不純物領域よりも不純物濃度を低くし、第1の不純物領域は、第2の不純物領域よりも不純物濃度を低くする。

(もっと読む)

121 - 140 / 419

[ Back to top ]