Fターム[5F048BC15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 材料 (764)

Fターム[5F048BC15]の下位に属するFターム

多結晶Si(SOI) (345)

Fターム[5F048BC15]に分類される特許

101 - 120 / 419

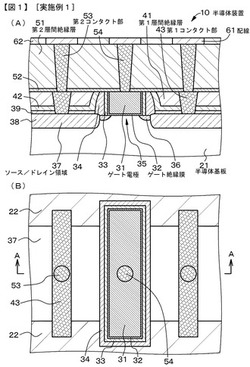

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リークを抑制しながら、キャリアの移動度向上とチャネル中でのキャリア速度の増加を実現することができるトランジスタを提供する。

【解決手段】半導体基板10のチャネル形成領域にチャネル方向に第1の幅を有するSiGe層15が埋め込まれ、チャネル形成領域上にゲート絶縁膜28が形成され、ゲート絶縁膜上に、第1の幅より大きい第2の幅を有してSiGe層の形成領域からはみ出す領域を有するゲート電極29が形成され、チャネル形成領域を挟む半導体基板においてエクステンション領域12を有するソースドレイン領域13が形成されて、電界効果トランジスタが構成されており、エクステンション領域と半導体基板の接合面から伸びる空乏層がSiGe層に達しないようにエクステンション領域とSiGe層が離間されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置が備えるnMOSトランジスタ及びpMOSトランジスタの形成面積を縮小する。

【解決手段】半導体装置の製造方法は、基板上に環状の突起部を形成する工程と、環状の突起部に第1のn型チャネル領域を形成する工程と、環状の突起部に第1のp型チャネル領域を形成する工程と、環状の突起部に形成された第1のn型チャネル領域及び第1のp型チャネル領域を跨ぐ第1のゲート電極を形成することにより、第1のnMOSトランジスタ及び第1のpMOSトランジスタを形成する工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 厚さが異なるゲート電極を含む、互いにチャネルタイプの異なるMISFETの対を形成する際におけるリソグラフィのプロセスマージンの低下を抑制できる半導体装置を提供すること。

【解決手段】 半導体装置は、第1の主面を有する半導体領域を含む第1の領域Pと、第2の主面を有する半導体領域を含む第2の領域Nとを備え、前記第1の主面が前記第2の主面よりも低い、半導体基板100と、第1の領域P内に設けられ、第1のゲート電極108,109を含む第1導電型MISFETと、第2の領域N内に設けられ、第2のゲート電極109を含む第2導電型MISFETであって、第2のゲート電極109の上面と第1のゲート電極108,109の上面とが同じ高さになるように、第2のゲート電極109の厚さは第1のゲート電極108,109の厚さよりも薄くなっている前記第2導電型MISFETとを具備してなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、pチャネルトランジスタのチャネル領域には圧縮歪を、nチャネルトランジスタのチャネル領域には引っ張り歪をそれぞれ効果的に印加できる新しい歪技術を提供する。

【解決手段】pチャネルトランジスタ105のゲート電極は、引っ張り内部応力を持つpチャネルメタル電極110を有する。nチャネルトランジスタ106のゲート電極は、圧縮内部応力を持つnチャネルメタル電極116を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】容易に製造できる半導体装置を提供する。

【解決手段】半導体装置は、PMOSトランジスタのゲート電極1pの仕事関数値が、High-kゲート絶縁膜16(16a)、及び、High-kゲート絶縁膜16・酸化シリコン膜15界面へのAlの拡散により調整されており、NMOSトランジスタのゲート電極1nの仕事関数値が、High-kゲート絶縁膜16・金属ゲート膜19間に挿入された、数原子層程度のAl層18により調整されている構成を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】混晶層に発生する転位、結晶欠陥を抑制することができる半導体装置を提供すること。

【解決手段】p型のSi基板13表面のn型ウェル層16の両端に形成され、SiおよびGeからなる混晶層18と、これらの混晶層18の表面にそれぞれ形成されたp型の不純物注入層19、20と、これらの不純物注入層19、20をそれぞれドレイン領域、ソース領域とするpMOSFET15−1と、を具備する素子領域11と、この素子領域11を囲うようにSi基板13の表面に形成された素子分離層14−1と、この素子分離層14−1外のSi基板13の表面に前記素子領域11の混晶層18と同一材料で形成され、その主方向が、Si基板13の<110>方向とは異なるダミーパターン35と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体絶縁膜及びメタルゲート電極を有する半導体装置において、高仕事関数を得ると共にNBTI信頼性劣化を低減する。

【解決手段】半導体装置100において、基板101上に、高誘電体ゲート絶縁膜109を介してメタルゲート電極110が形成されている。高誘電体ゲート絶縁膜109とメタルゲート電極110との界面におけるメタルゲート電極110の側に、ハロゲン元素が偏析している。

(もっと読む)

半導体装置、半導体装置の製造方法、電子機器および電子機器の製造方法

【課題】回路特性の向上が可能な、有機トランジスタよりなる論理回路を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、ドライバトランジスタ(PTD)とロードトランジスタ(PTL)を有する論理回路を含む半導体装置であって、ドライバトランジスタの能動層は、第1のp型有機半導体層(5D)からなり、ロードトランジスタの能動層は、第2のp型有機半導体層(5L)からなり、ロードトランジスタの閾値電圧(VthL)はドライバトランジスタの閾値電圧(VthD)よりも高い。p型有機半導体(5D,5L)の膜厚を変えることにより、閾値を変化させる。p型有機半導体(5D,5L)の材料を変えることにより、閾値を変化させる。第1のp型有機半導体層(5D)にドナーを含ませる。第2のp型有機半導体層(5L)にアクセプターを含ませる。かかる構成により、論理回路の特性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】pMOSトランジスタにcSiGeとeSiGeを適用し、且つゲート絶縁膜におけるダメージ発生を防止でき、素子特性の向上及びしきい値制御性の向上をはかる。

【解決手段】pMOSトランジスタのチャネル部及びソース・ドレイン領域にSiGeを用いた半導体装置において、Si基板202上の一部に形成され、pMOSトランジスタのチャネルとなる第1のSiGe層205と、第1のSiGe層205上にゲート絶縁膜206を介して形成されたゲート電極208と、pMOSトランジスタのソース・ドレイン領域に埋め込み形成され、且つチャネル側の端部が基板表面よりも深い位置でチャネル側に突出するように形成された第2のSiGe層214と、第1のSiGe層205と第2のSiGe層214とを分離するように、基板の表面部でSiGe層205,214間に挿入されたSi層222とを備えた。

(もっと読む)

半導体装置及び電子機器

【課題】回路面積が小さい、またはトランジスタの劣化を防止するよう形成された、有機トランジスタと無機トランジスタとを備えた半導体装置を提供する。

【解決手段】本発明の一形態の半導体装置としてのCMOS回路は、(a)基板100と、(b)有機半導体層106aを含むp型有機トランジスタPTと、(c)p型有機トランジスタPTの上層に設けられた無機半導体層126aを含むn型無機トランジスタNTと、を備える。さらに、n型無機トランジスタNTのチャネル領域126は、p型有機トランジスタPTのチャネル領域106と、平面視において少なくとも部分的に重なっている。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に、酸化物半導体層より導電率の高いバッファ層を形成し、該バッファ層の上にソース電極層及びドレイン電極層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、極めて高い歩留まりでゲート電極について均一で十分なフル・シリサイド化を確実に実現する。

【解決手段】ゲート電極104a,104b及びソース/ドレイン領域107a,107bのNiシリサイド化を行うに際して、1回目のNiシリサイド化の後に1回目のmsecアニール処理であるフラッシュランプアニール処理を行い、2回目のNiシリサイド化、更には必要であれば2回目のフラッシュランプアニール処理を行って、ソース/ドレイン領域107a,107b上には1回目のフラッシュランプアニール処理で形成されたNiSi層111bを維持した状態で、フル・シリサイドゲート電極115a,115bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】微細化が進んでも適切な歪を生じさせることができる半導体装置の製造方法を提供する。

【解決手段】nチャネルトランジスタ形成予定領域51nを覆う部分を残しながら絶縁膜6のエッチバックを行うことにより、pチャネルトランジスタ形成予定領域51p内のゲート電極4の側方にサイドウォール6aを形成する。サイドウォール6aをマスクとして半導体基板1の表面にp型不純物を導入してp型不純物導入領域8pを形成し、サイドウォール6aをマスクとしてp型不純物導入領域8pの表面に溝9を形成する。溝9内にSiGe層10を成長させる。絶縁膜6のエッチバックを行うことにより、nチャネルトランジスタ形成予定領域51n内のゲート電極4の側方にサイドウォールを形成し、nチャネルトランジスタ形成予定領域51n内において、このサイドウォールをマスクとして半導体基板1の表面にn型不純物を導入してn型不純物導入領域を形成する。

(もっと読む)

シャロートレンチアイソレーションプロセス

【課題】トレンチ構造の歪み導入要素によりに歪み導入されたチャネルを持つMOSトランジスタのリーク電流を改善する。

【解決手段】MOSトランジスタ106のチャネル領域108に、第1トレンチ構造55a、第2トレンチ構造55bによる歪み導入要素だけでなく、別の歪み導入要素として、MOSトランジスタ106表面上にコンフォーマルに設けられた窒化シリコンキャップ層130を設ける。別の態様では、チャネル領域108内の歪みは、ガス種、例えば水素、酸素、ヘリウムまたは別の希ガスをゲート110またはチャネル領域108の下の領域内に注入することによって導入される。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】閾値電圧が相対的に高い半導体装置のチャネル領域における不純物濃度を閾値電圧が相対的に低い半導体装置のチャネル領域における不純物濃度よりも高くすると、閾値電圧が相対的に高い半導体装置の駆動力の低下を招来する虞があった。

【解決手段】半導体装置は、第1のトランジスタと第2のトランジスタとを備えている。第1のトランジスタは、第1のチャネル領域3aと、第1のゲート絶縁膜4aと、第1のゲート電極5aと、第1のエクステンション領域8aとを有している。第2のトランジスタは、第1のトランジスタよりも高い閾値電圧を有しており、第2のチャネル領域3bと、第2のゲート絶縁膜4bと、第2のゲート電極5bと、第2のエクステンション領域8bとを有している。第2のエクステンション領域8bは浅接合化不純物を含んでおり、第2のエクステンション領域8bの接合深さは第1のエクステンション領域8aの接合深さよりも浅い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】同一の工程で、同一半導体基板上に異なる構造のトランジスタを形成する半導体装置の提供。

【解決手段】半導体基板上に第一及び第二のゲート電極40,41を形成する工程と、第一のゲート電極の側壁面に第一の絶縁層122を形成するとともに、第二のゲート電極のゲート幅方向両側の半導体基板上にエピタキシャル成長層9aを形成する工程と、第二のゲート電極の側壁面に第二の絶縁層を形成する工程と、第一の絶縁層及び第二の絶縁層を覆うように第三の絶縁層を形成する工程と、第二の絶縁層を覆う第三の絶縁層を除去する工程と、第一のゲート電極のゲート幅方向両側の半導体基板及びエピタキシャル成長層にそれぞれ不純物を拡散させて、第一及び第二の不純物拡散領域6,8を形成する工程と、第一及び第二の不純物拡散領域にコンタクトプラグ12,15を接続させる工程と、を具備してなることを特徴とする半導体装置の製造方法。

(もっと読む)

101 - 120 / 419

[ Back to top ]