Fターム[5F048BF18]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 基板(ウェル)コンタクト領域 (940)

Fターム[5F048BF18]に分類される特許

81 - 100 / 940

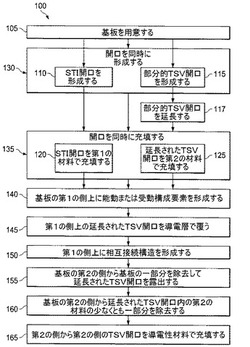

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体装置

【課題】出力トランジスタの形成領域から他の素子の形成領域への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体基板SUBと、1対の注入元素子DRと、アクティブバリア構造ABと、p型接地領域PGDとを備える。半導体基板SUBは主表面を有し、かつ内部にp型領域を有する。1対の注入元素子DRは、p型領域上であって主表面に形成される。アクティブバリア構造ABは、主表面において1対の注入元素子DRに挟まれる領域に配置される。p型接地領域PGDは、主表面において1対の注入元素子DRに挟まれる領域を避けて1対の注入元素子DRおよびアクティブバリア構造ABよりも主表面の端部側に形成され、かつp型領域に電気的に接続された、接地電位を印加可能な領域である。p型接地領域PGDは、1対の注入元素子DRに挟まれる領域と隣り合う領域において分断されている。

(もっと読む)

半導体装置

【課題】半導体装置においてチップサイズに影響を与えないデカップリング容量を得る。

【解決手段】半導体装置は、基板1、10と、高濃度拡散層領域11と、第1ウェル4と、第2ウェル3とを具備している。基板1、10は第1導電型である。高濃度拡散層領域11は基板1、10上に形成され、第1導電型である。第1ウェル4は基板1、10上に形成され、高濃度拡散領域11の一方側に設けられ、第1導電型である。第2ウェル3は基板1、10上に形成され、高濃度拡散領域11の他方側に設けられ、第1導電型と逆導電型となる第2導電型である。第2ウェル3と高濃度拡散領域11との間、及び、第2ウェル3と基板1、10との間でデカップリング容量が形成される。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

単一のプロセスを用いて高性能ロジックおよびアナログ回路をイネーブルするプロセス/設計方法論

【課題】混合信号プロセスにおいてアナログ回路の性能を向上させる方法および装置を提供すること

【解決手段】順方向バイアスおよび修正された混合信号プロセスを用いた回路設計を用いて、アナログ回路性能を向上させる方法が提示される。複数のNMOSトランジスタおよびPMOSトランジスタを含む回路が規定される。NMOSトランジスタのボディ端子は、第1の電圧ソースに連結され、PMOSトランジスタのボディ端子は、第2の電圧ソースに連結される。回路内のトランジスタは、各選択されたNMOSトランジスタのボディ端子に該第1の電圧ソースを適用することと、各選択されたPMOSトランジスタのボディ端子に該第2の電圧ソースを適用することとによって、選択的にバイアスされる。一実施形態において、第1の電圧ソースおよび第2の電圧ソースは、順方向バイアスおよび逆方向バイアスをトランジスタのボディ端子に提供するように修正可能である。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域におけるイオン濃度のばらつきを抑制すること。

【解決手段】半導体装置の製造方法は、半導体基板にイオンを注入するための第1開口を有し、第1層ウェルを形成するための第1マスクを半導体基板上に形成する工程と、第1マスクを用いて半導体基板に第1イオンを注入して、第1領域及び第2領域を有する第1層ウェルを形成する工程と、半導体基板にイオンを注入するための第2開口を有し、第2層ウェルを形成するための第2マスクを半導体基板上に形成する工程と、第2マスクを用いて半導体基板に第2イオンを注入して、第1層ウェルより下方に位置する第2層ウェルを形成する工程と、を含む。第1領域を第2領域より第1層ウェルの外縁寄りに形成する。第1イオンを注入する際に、第1マスクの第1内壁面で反射した第1イオンを第1領域に供給する。第2イオンを注入する際に、第2マスクの第2内壁面で反射した第2イオンを第2領域に供給する。

(もっと読む)

半導体集積回路

【課題】ESD保護回路の面積を増大させることなく、サージに対する耐性に優れた半導体集積回路を実現する。

【解決手段】半導体集積回路は、互いに隣接する入出力セル1及び入出力セル2間には、アノードが入出力端子3に接続され、且つ、カソードが入出力端子7に接続されたサイリスタ13と、カソードが入出力端子3に接続され、且つ、アノードが入出力端子7に接続されたサイリスタ14とが構成されている。

(もっと読む)

高電圧バイポーラベースESD保護構造

【課題】面積効率の良い高電圧の単極性ESD保護デバイスを提供する。

【解決手段】ESD保護デバイス300は、p型基板303と、基板内に形成され、カソード端子に接続されるn+及びp+コンタクト領域310、312を包含し、第1のpウェル308−1と、基板内に形成され、アノード端子に接続されるp+コンタクト領域311のみを包含する第2の別個のpウェル308−2と、第1及び第2半導体領域を取り囲み且つこれら半導体領域を分離するように基板内に形成された、電気的にフローティングのアイソレーション構造304、306、307−2とを含む。カソード及びアノードの端子に、トリガー電圧レベルを上回る正電圧が印加されると、ESD保護デバイスは、構造を通り抜ける低インピーダンス経路を提供してESD電流を放電するよう、内在サイリスタをスナップバックモードに入らせる。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供することにある。

【解決手段】半導体基板10内に形成された第1導電型の第1の不純物領域32、46と、半導体基板内に形成され、第1の不純物領域に隣接する第2導電型の第2の不純物領域34、48と、第2の不純物領域内に形成された第1導電型のソース領域30a、44aと、第1の不純物領域内に形成された第1導電型のドレイン領域30b、44bと、ソース領域とドレイン領域との間における第1の不純物領域内に、第2の不純物領域から離間して埋め込まれた、二酸化シリコンより比誘電率が高い絶縁層14と、ソース領域とドレイン領域との間における第1の不純物領域上、第2の不純物領域上及び絶縁層上に、ゲート絶縁膜22を介して形成されたゲート電極24a、24bとを有している。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】同一の極性を有する複数の薄膜FETの閾値電圧に差をつけて、半導体装置の性能の最適化を図ることができる。

【解決手段】半導体基板1と、半導体基板1上に設けられた埋め込み絶縁膜2と、埋め込み絶縁膜2上に形成された薄膜n型FET100と、埋め込み絶縁膜2上に形成された薄膜p型FET101と、埋め込み絶縁膜2上に形成された薄膜n型FET100bと、薄膜n型FET100のチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域4と、薄膜p型FET101のチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域5と、薄膜n型FET100bのチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域4bと、を備え、p型ウェル領域4、4b、5は、n型ウェル領域40によって囲まれており、かつ互いに接触していない。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

半導体装置及びサンプルホールド回路

【課題】ON状態での低いオン抵抗とOFF状態での小さいオフリーク電流を持つMOSトランジスタスイッチを用いた半導体装置及びサンプルホールド回路を実現する。

【解決手段】PMOSトランジスタM11がON状態の場合には、PMOSトランジスタM12がON状態になりPMOSトランジスタM11のバックゲート端子をPMOSトランジスタM11のソース端子に接続し、PMOSトランジスタM11がOFF状態の場合には、PMOSトランジスタM13がON状態になりPMOSトランジスタM11のバックゲート端子を電源電圧端子VDD1に接続する。

(もっと読む)

半導体装置

【課題】スイッチング損失を低減した半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、ベース層と、ベース層上に設けられた第2導電形半導体層と、第2導電形半導体層の表面からベース層側に向けて延び、ベース層には達しない複数の第1のトレンチの内壁に設けられた第1の絶縁膜と、第1の絶縁膜を介して第1のトレンチ内に設けられると共に第2導電形半導体層の表面に接する第1の電極とを備えている。第2導電形半導体層は、第1のトレンチで挟まれた第1の第2導電形領域と、第1の第2導電形領域とベース層との間および第1のトレンチの底部とベース層との間に設けられ、第1の第2導電形領域よりも第2導電形不純物量が少ない第2の第2導電形領域とを有する。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

半導体装置

【課題】同期整流方式のDCDC変換装置において、短絡防止期間中に、同期整流用FETのドレインが負電圧となると、基板−ドレインの間に電流が流れ、基板の電位が揺すられる。同期整流用FETを内蔵した素子の場合、この基板の電位の揺れは制御回路の誤動作を招く。

【解決手段】P型基板とバックゲートとが分離されたNチャネルMOSFETを2段縦積みにした構造を有する複合素子を、同期整流用FETとして用い、複合素子の上段側FETを、メイン側FETがオフかつ下段側FETがオフとなる短絡防止期間において、オフとする。

(もっと読む)

半導体素子

【課題】ゲート閾値の変動を抑制または防止できる半導体素子を提供する。

【解決手段】半導体素子1は、n型エピタキシャル層8と、n型エピタキシャル層8の表層部に形成されたボディ領域12と、ボディ領域12の表層部に形成されたn型ソース領域16と、n型エピタキシャル層8上に形成されたゲート絶縁膜19と、ゲート絶縁膜19上に形成されたゲート電極20およびゲート保護ダイオード30とを含む。ゲート保護ダイオード30は、第1のp型領域31とn型領域32と第2のp型領域33とを含む。第1のp型領域31とn型領域32によって第1のダイオード30Aが構成されている。n型領域32と第2のp型領域33によって第2のダイオード30Bが構成されている。第1のp型領域31はゲート電極20に接続されている。第2のp型領域33はソース電極27を介してソース電極27に接続されている。

(もっと読む)

81 - 100 / 940

[ Back to top ]