Fターム[5F048BF18]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 基板(ウェル)コンタクト領域 (940)

Fターム[5F048BF18]に分類される特許

121 - 140 / 940

半導体装置

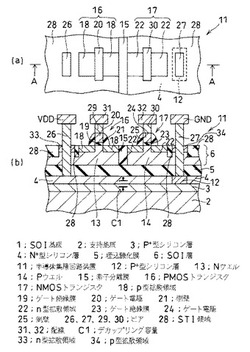

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

半導体装置

【課題】ラッチ回路を有する半導体装置におけるデータの破壊を抑制する。

【解決手段】ラッチ回路に含まれる第1トランジスタP4と、ラッチ回路に含まれ、第1トランジスタP4と共通のウェル40内に形成された、第1トランジスタP4と同じ導電型の第2トランジスタP1と、第1トランジスタP4と第2トランジスタP1との間に設けられ、ウェル40を電源に接続するウェルコンタクトWCと、を備える。第1トランジスタP4側のウェル40内で発生した電荷は、ウェルコンタクトWCに流れるため、第1トランジスタP4におけるソフトエラーの影響が、第2トランジスタP1に伝搬することを抑制することができる。これにより、ラッチ回路内における2箇所のノードにおいて、同時に論理の反転が生じることを抑制することができるため、データの破壊を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】フィールドストップ領域のキャリア濃度が低減することを防止することができる半導体装置の製造方法を提供すること。

【解決手段】ドリフト領域1となる半導体基板のおもて面の表面に、半導体装置100のおもて面素子構造を形成する。ついで、ドリフト領域1の裏面を研削する。ついで、ドリフト領域1の裏面の一部に、P(リン)をイオン注入する(第1注入工程)。ついで、炉アニールを行い、第1注入工程においてドリフト領域1の裏面に注入したPを活性化する。これにより、ダイオード120のn+型領域10が形成される。ついで、ドリフト領域1の裏面の全体に、Se(セレン)をイオン注入する(第2注入工程)。第2注入工程は、第1注入工程が行われた後に行う。ついで、炉アニールを行い、第2注入工程においてドリフト領域1の裏面に注入したSeを活性化する。これにより、フィールドストップ領域11が形成される。

(もっと読む)

電力用半導体装置

【課題】消費電力を低減することができる電力用半導体装置を得る。

【解決手段】高耐圧ダイオードDBによりコンデンサCBを充電してハイサイド駆動回路10aの駆動電圧を得る電力用半導体装置において、高耐圧ダイオードDBは、P−型半導体基板12と、P−型半導体基板12の表面に設けられたN型カソード領域14と、N型カソード領域14内に設けられたP型アノード領域16と、P型アノード領域16内に設けられたP+型コンタクト領域20及びN+型コンタクト領域22と、N型カソード領域14に接続されたカソード電極24と、P+型コンタクト領域20及びN+型コンタクト領域22に接続されたアノード電極26とを有する。

(もっと読む)

半導体装置及び駆動方法

【課題】絶縁層上に形成された部分空乏型のトランジスターにおいて、ヒストリー効果を低減し、なおかつ高いON/OFF比、及び急峻なサブスレッショルド特性を実現する。

【解決手段】絶縁層上の半導体層に形成された第1導電型のソース領域、第1導電型のドレイン領域、及び、第2導電型のボディ領域と、第1ゲート絶縁膜と、第1ゲート電極と、を含む部分空乏型の第1トランジスターと、絶縁層上の半導体層に形成された第2導電型のソース領域、第2導電型のドレイン領域、及び、第1導電型のボディ領域と、第2ゲート絶縁膜と、第2ゲート電極と、を含む第2トランジスターと、を具備し、第1トランジスターの第2導電型のボディ領域は、第2トランジスターの第2導電型のソース領域及び第2導電型のドレイン領域の内の一方に接続されている。

(もっと読む)

静電気保護用のMOS型半導体装置

【課題】ESD素子のESD耐量を向上させる。

【解決手段】ESD素子21は半導体基板1表面に形成したP型ウェル領域2上にゲート絶縁膜を介して、一方向に延びた複数本のゲート電極3が相互に平行に設けられており、P型ウェル領域2の表面におけるゲート電極3の直下域がチャネル領域9になっている。そして、チャネル領域9間の領域がN+ソース領域5又はN+ドレイン領域4となっており、N+ソース領域5とN+ドレイン領域4とは交互に配列されている。そして、並列して隣接するゲート電極3間に位置するN+ドレイン領域4を分割し、かつ隣接するゲート電極3を接続するようにゲート電極接合領域10を設ける。なお、ゲート電極接合領域10の直下域にはチャネル領域9と同一の不純物濃度を有する領域11が設けられている。

(もっと読む)

半導体装置

【課題】貫通電流を低減させることができる相補型の論理回路を用いることで、消費電力を抑えることができる半導体装置の提案を目的の一とする。或いは、貫通電流を低減させることができる相補型の論理回路を用いることで、発熱を抑えることができる半導体装置の提案を目的の一とする。

【解決手段】通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられたnチャネル型トランジスタ、或いはpチャネル型トランジスタを、相補型の論理回路に用いる。そして、オフ電流が極めて小さい絶縁ゲート電界効果型トランジスタをスイッチング素子として用い、上記第2のゲート電極の電位を制御する。上記スイッチング素子として機能するトランジスタは、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含む。

(もっと読む)

半導体装置の製造方法

【課題】高耐電圧により大電流化が可能で、オン抵抗が低く高速動作が可能で、高集積化と省エネルギーが可能で、素子間分離の容易な、電気熱変換素子駆動用の半導体装置を提供する。

【解決手段】電気熱変換素子とそれに通電するためのスイッチング素子とがp型半導体基体1に集積化されている。スイッチング素子は、半導体基体1の表面に設けられたn型ウェル領域2と、それに隣接して設けられチャネル領域を提供するp型ベース領域6と、その表面側に設けられたn型ソース領域7と、n型ウェル領域2の表面側に設けられたn型ドレイン領域8,9と、チャネル領域上にゲート絶縁膜を介して設けられたゲート電極4とを有する絶縁ゲート型電界効果トランジスタである。ベース領域6は、ドレイン領域8,9を横方向に分離するように設けられた、ウェル領域2より不純物濃度の高い半導体からなる。

(もっと読む)

半導体集積回路装置

【課題】ESD保護回路を備え外部端子数を効率よく配置できる半導体集積回路装置を提供する。

【解決手段】第1、第2電源電圧を供給する第1、第2電源パッドに対応した第1、第2電源セル、第1信号パッドに対応した入出力セル、第1電源電圧を供給する第1電源線、第2電源電圧を供給する第2電源線を有する。入出力セルは、信号入出力を行う回路、静電保護回路及び第1電源線と第2電源線との間に設けられた第1MOSを有する。第1電源セルは、第1電源パッドの正静電気に応答して第1MOSを一時的にオンにさせる時定数回路、第1電源パッドに向かう電流を流す一方向性素子を有する。第2電源セルは、第2電源パッドの正静電気に応答して第1MOSを一時的にオンにさせる時定数回路、第2電源パッドに向かう電流を流す一方向性素子を有する。第1MOSのゲートとウェルは時定数回路と接続される。

(もっと読む)

交流スイッチ

【課題】高耐圧の用途に適用可能な交流スイッチ(半導体リレー)を提供する。

【解決手段】交流スイッチ1は、ソース(S)同士を接続した第1化合物半導体MOSFET11および第2化合物半導体MOSFET12と、第1化合物半導体MOSFET11のドレイン(D)に接続された第1出力端子13と、第2化合物半導体MOSFET12のドレイン(D)に接続された第2出力端子14とを含む。交流スイッチ1は、オフ時の第1出力端子13および第2出力端子14の間の耐圧が400V以上(より好ましくは600V以上)であり、オン時の第1出力端子13および第2出力端子14の間の抵抗が20mΩ以下(より好ましくは10mΩ以下)である。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOS型トランジスタなどの半導体装置が動作中に生ずる経時的な特性変動を抑制すると共に、高耐圧かつ低オン抵抗が実現される半導体装置およびその製造方法を提供する。

【解決手段】 N型半導体層102に、深さが1μmより小さいP型の第1ドレインオフセット領域103と、深さが第1ドレインオフセット領域103より小さく、不純物濃度が第1ドレインオフセット領域103より大きいP型の第2ドレインオフセット領域105と、第1ドレインオフセット領域103より深いN型のボディ領域106と、N型のソース領域107およびドレイン領域104とを設ける。またLOCOS酸化膜からなる絶縁膜110と、ゲート絶縁膜108を介して形成されたゲート電極109とをN型半導体層102上に備える構造とする。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間の絶縁膜にて構成される寄生容量を充放電する変位電流による回路誤動作を防止する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成すると共に、活性層2cの埋込絶縁膜2b側にn型ガードリング埋込層42c等と同じ導電型の深いn型拡散領域42b等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。n型ガードリング42c等とp型ウェル42d等は、それぞれ逆バイアスまたは同電位となるように電位固定する。

(もっと読む)

スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法

【課題】複数のスタンダードセルを有する半導体装置のチップ面積をさらに小さくする。

【解決手段】半導体装置SD1は第1および第2スタンダードセルSC1,SC2を備える。第1スタンダードセルSC1は、拡散領域An11、拡散領域An11に対向する機能素子領域FE1、および金属層MT11を有する。第2スタンダードセルSC2は、拡散領域An11に連続する拡散領域An21、拡散領域An21に対向する機能素子領域FE2、ならびに拡散領域An21および機能素子領域FE2の間に形成された拡散領域CR21を有する。金属層MT11および機能素子領域FE2は、拡散領域An11、拡散領域An21、および拡散領域CR21通して電気的に接続される。

(もっと読む)

半導体集積回路の設計方法

【課題】フォトリソグラフィ工程で生じる光近接効果に起因するゲート長のばらつきとゲートの寄生容量のばらつきを抑制し、標準セルの実際の特性を反映させたライブラリを設計可能とし、これにより設計マージンを小さくして高性能な半導体集積回路を提供する。

【解決手段】標準セルSc1を配列して半導体集積回路を設計する方法において、標準セルSc1を構成するゲートパターン5の端部に、該ゲートパターン5と垂直な方向にダミーパターン3を配置し、該ダミーパターン3の配置により、ゲートパターン5の端部での該ゲートパターンの占有密度の低下を補う。

(もっと読む)

半導体装置

【課題】最小加工寸法がフィン幅となるFinFETの構造において、極めて制御が困難なリング形状の加工を不要として、加工ばらつきに起因する特性ばらつきの小さなユニットセルを提供する。

【解決手段】ユニットセルは、半導体基板1上に形成された開ループ構造のゲート電極Gと、前記ゲート電極Gの内方となる領域にフィン状に形成されたドレイン領域2と、前記ゲート電極Gの外方となる領域に形成されたフィン状のソース領域3とを有する。前記ドレイン領域2の上にはドレインコンタクト2aが形成され、前記ソース領域3上にはソースコンタクト3aが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】電源配線の電位の変動に起因するボディ領域の電位の変動を抑制し得る半導体装置を得る。

【解決手段】シリコン層4の上面内には、パーシャルトレンチ型の素子分離絶縁膜5が選択的に形成されている。電源配線21は、素子分離絶縁膜5の上方に形成されている。電源配線21の下方において、素子分離絶縁膜5には、絶縁層3の上面に達する完全分離部分23が形成されている。換言すれば、半導体装置は、電源配線21の下方において、シリコン層4の上面から絶縁層3の上面に達して形成された完全分離型の素子分離絶縁膜を備えている。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる静電気保護装置の面積を大きくすることなく、その破壊耐量及び維持電圧を大きくする。

【解決手段】第1導電型である半導体基板1と、半導体基板の上又は上部に形成された第2導電型である第1拡散層3と、第1拡散層の上部に形成され、第1導電型である第2拡散層5と、第2拡散層の上部に形成され、第2導電型である第3拡散層6と、第1拡散層の上部で且つ第2拡散層から間隔をおいて形成された第2導電型である第4拡散層8と、少なくとも第3拡散層の下に、第2拡散層と間隔をおき且つ下端部が第1拡散層の下端部よりも下に位置するように形成された第1導電型の第5拡散層2とを備えている。第3拡散層から第5拡散層までの最短距離と、第5拡散層から第4拡散層までの最短距離及び第1拡散層の下端部から第4拡散層までの最短距離のいずれか短い方の距離との和は、第3拡散層から第4拡散層までの最短距離よりも小さい。

(もっと読む)

半導体装置

【課題】占有面積の小さい、SGTを用いた2段以上に直列に接続されたCMOSインバータ結合回路を提供する。

【解決手段】CMOSインバータ結合回路は、SGTを用いた2段以上に直列に接続されたCMOSインバータから構成される。複数のCMOSインバータは、基板のソース拡散層106a、107aを共用する。ゲート配線111a〜111f上に形成されるコンタクト121の構造が異なるCMOSインバータが交互に隣接して配置されている。CMOSインバータ同士は、最小間隔で配置されている。CMOSインバータの出力端が次段のCMOSインバータのコンタクト121を介して、次段のCMOSインバータの配線層125に接続される。

(もっと読む)

SeOI上の疑似インバータ回路

【課題】メモリアレイのワードライン・ドライバ回路として使用できる、大きくなく、低消費電力の回路を提供する。

【解決手段】半導体・オン・インシュレータ(SeOI)基板上に形成された回路であって、電源電位を印加する為の第1、第2の端子間に第2のチャネル型のトランジスタと直列の第1のチャネル型のトランジスタを含み、トランジスタの各々が薄層におけるドレイン領域およびソース領域と、ソース領域とドレイン領域間に延びるチャネルと、チャネルの上方に配置されたフロント・コントロール・ゲートとを備え、各トランジスタが、トランジスタのチャネルの下方のベース基板に形成され、かつトランジスタの閾値電圧を調整する為にバイアスされうるバック・コントロール・ゲートを有し、トランジスタのうちの少なくとも1つが閾値電圧を十分に調整するバックゲート信号の作用の下、空乏モードで動作するように構成される。

(もっと読む)

121 - 140 / 940

[ Back to top ]