Fターム[5F048BF18]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 基板(ウェル)コンタクト領域 (940)

Fターム[5F048BF18]に分類される特許

41 - 60 / 940

トランジスタ及び半導体装置

【課題】SEU耐性が高く、高性能で低価なトランジスタ及び半導体装置を提供すること。

【解決手段】絶縁性基板12上に形成されたシリコン層と、シリコン層に形成され、第1導電型であるボディ(P−)15、第2導電型であるソース(N+)13、ドレイン(N+)14からなる部分と、ボディ(P−)15及びソース(N+)13にボディ(P−)15と同一導電型で接合され、ソース(N+)13と同じもしくは高い電位が供給されるボディ端子(P+)16と、を具備する。ボディ(P−)15において放射線によって発生した負電荷は、ボディ端子(P+)16を介して当該トランジスタ外に流出する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型トランジスタの特性にばらつきが生じることを抑制する。

【解決手段】半導体基板100には縦型MOSトランジスタ20が形成されている。半導体基板100の表面上には、第1層間絶縁膜300及び第1ソース配線312が形成されている。第1ソース配線312は、第1層間絶縁膜300上に形成されており、平面視で縦型MOSトランジスタ20と重なっている。第1層間絶縁膜300にはコンタクト302が埋め込まれている。コンタクト302は、縦型MOSトランジスタ20のn型ソース層140と第1ソース配線312とを接続している。そして第1ソース配線312には、複数の開口316が形成されている。

(もっと読む)

半導体装置

【課題】 出力回路用、或いは、アナログ回路用の2種類の特性に夫々特性が最適化されてなるトランジスタを備えた半導体装置を低コストで提供する。

【解決手段】

同一基板101上に、出力回路用の第1のトランジスタ1aと、アナログ回路用の第2のトランジスタ1bが搭載された半導体装置であって、各トランジスタのゲート絶縁膜が、ドリフト領域107上面の一部の領域において、膜厚の厚い厚膜絶縁膜108bとなっており、ボディ領域103に向かって延伸するドリフト領域107を、第1のトランジスタ1aでは当該厚膜絶縁膜108bのボディ領域103側境界Aを超えて延伸させ、第2のトランジスタ1bでは当該厚膜絶縁膜108bのボディ領域側境界Aよりも内側にとどまるように延伸させる。

(もっと読む)

仮想ボディ・コンタクト型トライゲート

【課題】FETデバイスにおける閾値電圧をより良く制御できるデバイスの提供。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

(もっと読む)

半導体装置、半導体ウエハ、及びこれらの製造方法

【課題】トランジスタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】SOI基板101は、P型半導体層102の上にN型半導体層104が形成された半導体基板12、その上に形成されたBOX層106、及びBOX層上に形成されたSOI層108を有する。第1素子分離絶縁層110bは、SOI基板101に埋め込まれ、下端16がP型半導体層102に達し、第1素子領域(NFET領域30)と第2素子領域(PFET領域40)とを分離する。P型トランジスタ130bは、第1素子領域40に位置し、チャネル領域120bを有し、N型トランジスタ130aは、NFET領域30に位置し、チャネル領域120aを有する。第1バックゲートコンタクト134bは、第1素子領域40に位置する第2導電型層層104に、第2バックゲートコンタクト134aは、第2素子領域30に位置する第2導電型層104に接続される。

(もっと読む)

半導体装置、半導体装置の製造方法、電子装置、及び車両

【課題】縦型バイポーラトランジスタのSOA(安全動作領域)が狭くなることを抑制する。

【解決手段】p型ベース層150は、厚さ方向の不純物プロファイルにおいて、第1のピーク、第2のピーク、及び第3のピークを有している。第1のピークは、最も半導体基板100の表面側に位置している。第2のピークは、第1のピークよりも半導体基板100の裏面側に位置しており、第1のピークよりも高い。第3のピークは、第1のピークと第2のピークの間に位置している。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

半導体装置、半導体パッケージ、および半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】N型基板10と、N型基板10の一面側に設けられたP型ウェル40と、P型ウェル40に設けられたP型高濃度不純物領域42と、P型ウェル40に設けられたN型のソース・ドレイン領域を有するMOSトランジスタ20と、N型基板10の一面側に設けられ、かつ一方がP型高濃度不純物領域42と電気的に接続し、他方が接地されているソース・ドレイン領域を有するMOSトランジスタ30と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体装置

【課題】 ESD対策のための特別な工程や専用マスクを増やすことなく、ESD放電能力の向上を図る事が可能な半導体装置を実現する。

【解決手段】

基板上の所定の領域に、MOSFET構造のHVトランジスタ23と保護抵抗回路25からなる高耐圧用のESD保護素子21、及び、MOSFET構造のLVトランジスタ24と保護抵抗回路26からなる低耐圧用のESD保護素子22が形成されている。当該保護抵抗回路25(26)は、ゲート電極8b(8d)を挟んで互いに対抗するようにウェル2(3)の表層に分離形成される抵抗ドリフト領域16(17)の双方が、同導電型の低濃度ドリフト領域5c(5d)により電気的に接続されていることを除き、HVトランジスタ23(LVトランジスタ24)と同一の構造である。

(もっと読む)

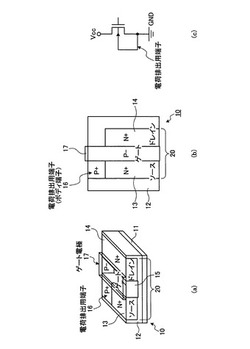

半導体装置

【課題】ブートストラップ方式のドライブ回路を有する半導体装置において、ブートストラップダイオードの順バイアス時にp-基板側に流れるホールによるリーク電流を抑制することができる半導体装置を提供することにある。

【解決手段】ブートストラップダイオードDb下にSON構造の空洞3を形成し、ブートストラップダイオードDbとグランド電位(GND)となるGNDp領域4との間のn-エピ層2にその空洞3に達するフローティングp領域5を形成することで、外部のブートストラップコンデンサC1充電時のp-基板1へのホールによるリーク電流を抑えることができる。

(もっと読む)

半導体装置及びDC−DCコンバータ

【課題】耐久性が高い半導体装置及びDC−DCコンバータを提供する。

【解決手段】実施形態に係る半導体装置は、高電位側電源電位に接続するための第1の配線と、前記高電位側電源電位に接続するための、前記第1の配線とは別の第2の配線と、前記第1の配線に一端が接続され、他端が出力端子に接続されるスイッチングトランジスタと、前記高電位側電源電位と前記低電位側電源電位との間で前記スイッチングトランジスタと並列に接続される保護素子とを備える。前記保護素子は、前記第1の配線に接続される、第1のp形半導体領域と、前記第2の配線に接続される、前記第1のp形半導体領域に接したn形半導体領域と、前記n形半導体領域に接し、前記第1のp形半導体領域から離隔し、前記低電位側電源電位に接続するための配線に接続される第2のp形半導体領域と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

半導体装置

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

半導体装置

【課題】たとえばDC−DCコンバータ等の電源または電力変換機器のスイッチング等に使用されるパワーMOSFET等の絶縁ゲートを有するパワー系能動素子は、スイッチングの高速化に伴い、ゲート容量を極力小さくする必要がある。このためには、チャネルとならない部分のゲート電極を取り去り、スプリットゲートとする手法が有効とされている。しかし、Nチャネル型パワーMOSFETを例に取り説明すると、その反作用として、チャネルを形成するP型ボディ領域の端部に電界が集中するため、パンチスルー耐圧が低下する等の問題が発生する。

【解決手段】本願の一つの発明は、プレーナ−バーティカル型パワーMOSFET等の絶縁ゲートを有するパワー系能動素子を有する半導体装置に於いて、各アクティブセル内のスプリットゲート間にトレンチ内に延在するフィールドプレート、すなわち、トレンチフィールドプレートを設けたものである。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

41 - 60 / 940

[ Back to top ]