Fターム[5F058BA05]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成の目的、効果 (3,596) | イオン汚染防止 (120)

Fターム[5F058BA05]に分類される特許

21 - 40 / 120

選択的窒素化の方法

ここに、半導体装置の形成方法が提供された。ある実施の形態において、半導体装置の形成方法は、酸化物表面とシリコン表面とを有する基板を用意し、酸化物表面およびシリコン表面の双方の露出面に窒素含有層を形成し、酸化物表面上から窒素含有層を選択的に除去することによって窒素含有層を酸化する工程を有する。別の実施の形態において、シリコン特徴部上に形成された窒素含有層の残余部分上に酸化物層が形成される。また、ある実施の形態において、酸化物表面が半導体装置の1つまたはそれ以上のフローティングゲートに隣接して配置されている浅いトレンチ分離領域(STI)の露出した表面である。ある実施の形態において、シリコン表面は、半導体装置のシリコンまたはポリシリコンのフローティングゲートの露出面である。  (もっと読む)

(もっと読む)

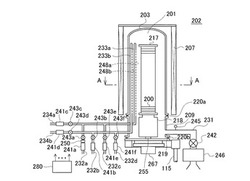

半導体装置の製造方法及び基板処理装置

【課題】処理室内壁等へのダメージを抑制しつつ、高誘電率膜中へのボロンの混入を抑制する半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】処理室201内に基板200を搬入する工程と、処理室201内に処理ガス232a,bを供給して基板200上に高誘電率膜を形成する処理を行う工程と、処理後の基板を処理室201内から搬出する工程と、処理室201内にボロンを含むハロゲン系ガス232cを供給して処理室201内に付着した高誘電率膜を含む堆積物を除去し処理室201内をクリーニングする工程と、処理室201内に酸素系ガス232dを供給してクリーニング後に処理室内に残留するボロンを除去もしくは固定する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】配線材料の拡散を抑えながら、金属配線の微細化を図ることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に層間絶縁膜を形成する工程(a)と、層間絶縁膜に配線を形成する工程(b)と、配線の上面及び層間絶縁膜の上面に有機溶液を塗布する工程(c)と、工程(c)の後に、配線の上面及び層間絶縁膜の上面にシリル化溶液を塗布する工程(d)と、工程(d)の後に、基板を加熱する工程(e)と、少なくとも配線の上面上に第1のライナー絶縁膜を形成する工程(f)とを備えている。

(もっと読む)

金属層間誘電体による拡散防止バリヤ層を有する集積回路およびその製造方法。

【課題】ライン間キャパシタンスを減少できる構造を有する集積回路および不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止できる集積回路の製造方法を提供する。

【解決手段】低誘電率材料中での不純物の移動を防止できるキャップ層あるいはバリヤ層により、不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止する。集積回路は第一の誘電体層と集積回路のより上層の導電層間に拡散防止バリヤ層を堆積して製造される。拡散防止バリヤ層はその次の金属層で不純物を含む誘電体層へその場で形成され、さらに、研磨を含む処理が多層誘電体構造に対してなされる。キャップ層あるいはバリヤ層にその場堆積は不純物を含む層を雰囲気にさらすのを防止し、そしてキャップ層あるいはバリヤ層により、水分、水素あるいはそのたのものにより、層が汚染されるのを防止することができる。

(もっと読む)

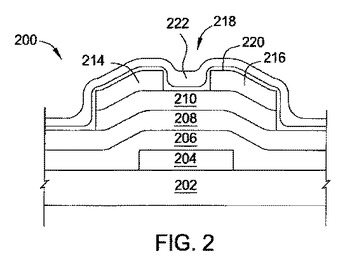

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備える平板表示装置

【課題】酸素を含む化合物半導体を活性層とする薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、基板10上に形成されたゲート電極12と、ゲート絶縁膜13によりゲート電極12と絶縁され、ゲート電極12を覆うようにゲート絶縁膜13上に形成された、酸素を含む化合物半導体からなる活性層14と、活性層14の上部に形成された保護層15と、活性層14と接触するソース電極16a及びドレイン電極16bと、を備え、保護層15が、チタン酸化物(TiOx)またはチタン酸窒化物(TiOxNy)で形成される。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する、シリサイド化される金属を含有する複数の電気素子要素と、複数の電気素子要素を覆い、電気素子要素に含まれる金属が実質的にシリサイド化しない温度で薄膜形成したシリコンを含む保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、保護絶縁膜は、シリコンおよび窒素を含有できる。保護絶縁膜は、260℃以下の温度で薄膜形成した窒化シリコン膜であってよく、好ましくは100℃以下の温度で薄膜形成した窒化シリコン膜である。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】半導体装置の製造方法に於いて、簡便な方法により、処理容器の内壁面をプラズマによりコーティングし、内壁面から酸素等の汚染原子が放出されることを抑止し、成膜品質を向上させる。

【解決手段】基板5を処理する処理容器1の内面を、プラズマ処理により反応ガス19でコーティング処理する工程と、前記処理容器内に基板を搬入する工程と、前記反応ガスを用いて基板をプラズマ処理する工程と、前記処理容器内から基板を搬出する工程とを有する。

(もっと読む)

酸素含有前駆体を用いる誘電体バリアの堆積

低誘電率及び優れた電気特性等の改良されたバリア誘電体特性を有する、ケイ素、炭素、酸素及び水素を有する前駆体を含む誘電体バリアフィルムを堆積させるための方法を与える。この方法は、相互接続構造のためのダマシン又は二重ダマシン集積で、又は他の誘電体バリア用途で用いられるバリア層に関して重要となるであろう。この例では、バリア性能を改良する特定の構造特性が注目される。  (もっと読む)

(もっと読む)

誘電体膜の形成方法

【課題】薄い絶縁物の分子層で覆われたSi基板表面にCVD法により誘電体膜を形成する際のインキュベーション時間をなくし、得られる誘電体膜の均一性を向上させると同時に、誘電体膜の膜厚方向の組成を制御する。

【解決手段】Si基板上への誘電体膜の形成方法は、前記Si基板上に第一の金属の気相分子化合物を実質的に一様に吸着させ、前記Si基板上を前記第一の金属の気相分子化合物により覆う第一の工程と、前記Si基板を覆う前記第一の金属の気相分子化合物を酸化雰囲気中で分解し、前記Si基板上に前記第一の金属を含む第一の誘電体分子層を形成する第二の工程と、前記Si基板上に第二の金属の気相分子化合物を実質的に一様に吸着させ、前記Si基板上を前記第二の金属の気相分子化合物により覆う第三の工程と、前記Si基板を覆う前記第二の金属の気相分子化合物を酸化雰囲気中で分解し、前記第一の誘電体分子層上に前記第二の金属を含む第二の誘電体分子層を形成する第四の工程と、を含む

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の信頼性を向上させることができる製造方法を提供する。

【解決手段】半導体基板1に形成される半導体素子を覆う絶縁膜11が、埋め込み特性が良好とされる熱CVD法等によって形成される。その絶縁膜11を覆うように、耐湿性に優れているとされるプラズマCVD法によって絶縁膜14が形成される。その絶縁膜11および絶縁膜14を貫通するようにプラグ13が形成される。さらに、その絶縁膜14上に、誘電率が比較的低いLow−k膜からなる絶縁膜16が形成され、その絶縁膜16に、ダマシン技術によって、プラグ13に電気的に接続される配線20が形成される。

(もっと読む)

半導体装置の製造方法

【課題】溝を埋め尽くすように形成されるCu層中のMnの残留量の増加を生じることなく、溝の側面上における合金膜の膜剥がれの発生を防止することができる、半導体装置の製造方法を提供する。

【解決手段】SiおよびOを含む絶縁材料からなる第2絶縁層6に、第2溝11が形成される。次に、スパッタ法により、第2溝11の内面に、CuMn合金からなる合金膜18が被着される。この合金膜18は、第2溝11の内面に接する部分のMn濃度が相対的に高く、その表層部分のMn濃度が相対的に低くなるように形成される。次いで、合金膜18上に、Cuからなる第2配線14が形成される。第2配線14の形成後、熱処理により、第2配線と第2絶縁層6との間に、MnSiOからなる第2バリア膜13が形成される。

(もっと読む)

半導体装置の製造方法

【課題】バリア膜を良好に形成することができながら、Cu配線中のMnの残留量を低減することができる、半導体装置の製造方法を提供する。

【解決手段】SiおよびOを含む第2絶縁層6に、第2溝11およびビアホール12が形成された後、Mnからなる金属膜18が第2溝11およびビアホール12の側面および底面に被着される。次いで、金属膜18中のMnと第2絶縁層6中のSiおよびOとを結合させるための熱処理が行われる。この熱処理の結果、第2溝11およびビアホール12の内面上に、MnSiOからなるバリア膜が形成される。

(もっと読む)

III−V族化合物半導体基板の製造方法、エピタキシャルウエハの製造方法、III−V族化合物半導体基板およびエピタキシャルウエハ

【課題】酸化膜の厚みを精度よく制御でき、かつエピタキシャル層を形成したときに表面荒れを抑制するIII−V族化合物半導体基板の製造方法、エピタキシャルウエハの製造方法、III−V族化合物半導体基板およびエピタキシャルウエハを提供する。

【解決手段】III−V族化合物半導体基板の製造方法は、以下の工程が実施される。まず、III−V族化合物半導体からなる基板が準備される(S11)。そして、この基板が酸性溶液で洗浄される(S12)。そして、洗浄する工程後に、湿式法により基板上に酸化膜が形成される(S13)。

(もっと読む)

シリコン・ウエーハのパッシベイションのための堆積方法

基板(4)が、基板キャリア・プレート(3)の高い位置に設けられた基板サポート(31)の上に取り付けられる。この基板を有する基板キャリア・プレートは、次に、プラズマ反応装置(8)の中に置かれる。高い位置に設けられた基板サポートのために、基板の両側がプラズマ(6)に曝され、それにより、電気的なパッシベイション・レイヤ(7)で被覆される。 (もっと読む)

金属酸窒化物TFT用キャッピング層

キャッピング層は、汚染からアクティブチャネルを保護するために、薄膜トランジスタ(TFT)のアクティブチャネルの上に堆積してもよい。キャッピング層は、TFTの性能に影響するかもしれない。キャッピング層があまりに多量の水素、窒素、又は酸素を含んでいるならば、TFTの閾値電圧、サブスレショルドスロープ、及び移動度に否定的に影響を与えるかもしれない。窒素、酸素、及び水素含有ガスの流速の比率を制御することによって、TFTの性能が最適化されるかもしれない。更に、電力密度、キャッピング層堆積圧、及び温度も、TFT性能を最適化するために制御してもよい。  (もっと読む)

(もっと読む)

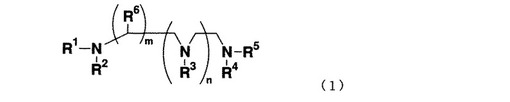

窒化炭素含有膜、その製法、及びその用途

【課題】PECVD装置に適した化合物を原料として窒化炭素膜を形成し、窒素含有量が高く、ガスバリア及び半導体用の絶縁膜として使用できる膜を提供する。

【解決手段】下記一般式(1)

(式中、R1,R2,R3,R4,R5,R6は、水素原子または炭素数1〜20の炭化水素基を表し、互いに結合していても良い。m、nは、0〜20の整数を表す。)で示される化合物を原料として用い、プラズマ励起化学気相成長法により窒化炭素含有膜を製造し、それを用いてガスバリア膜や半導体デバイスを製造する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】層間絶縁膜からメモリセルへの水素原子の拡散を抑えて、メモリセルの動作の信頼性を向上させること。

【解決手段】メモリセル(ゲート電極5、ソース・ドレイン領域5a、5b)と層間絶縁膜6の間にてメモリセルを覆うカバー膜5を有する半導体記憶装置であって、カバー膜5は、シリコン窒化膜5bの表面に水素吸蔵膜5aが被覆されるとともに、シリコン窒化膜5bの底面に水素吸蔵膜5cを有する膜である。水素吸蔵膜5a、5bは、Si2N2Oを含むシリコン窒化酸化膜である。

(もっと読む)

半導体装置およびその製造方法

【課題】十分なEM耐性および配線間TDDB寿命を確保しつつ、層間絶縁膜の低誘電率化を行っても絶縁膜ライナー膜厚を薄くすることができ、配線間の実効比誘電率Keffを低減した高速で高信頼性な配線を得ることができる。

【解決手段】第1の絶縁膜1には配線溝M1が形成されており、配線溝M1内にはCu膜2bが設けられている。Cu膜2bの上にはSiCN膜3a、SiCO膜3bおよびSiOC膜4aが順に設けられており、SiOC膜4aはSiCN膜3aおよびSiCO膜3bよりも低誘電率な絶縁膜である。SiCO膜3bの上面には、高密度化処理が施されて高密度膜3cが形成されている。

(もっと読む)

高信頼性銅配線及びその製造方法

【課題】銅配線を用いる半導体装置において、銅配線の酸化を防ぐと共に、配線間誘電率を低下させる。

【解決手段】半導体装置10は、半導体基板上に形成された第1の層間絶縁膜11と、第1の層間絶縁膜11上に埋め込まれて形成され、銅を含む導電膜12bを有する配線12と、配線12上を含む第1の層間絶縁膜11上に形成された絶縁性バリア膜15と、絶縁性バリア膜15上に形成され、低誘電率膜からなる第2の層間絶縁膜16と、導電膜12bと絶縁性バリア膜15との間に導電膜12上を覆うように形成され、銅よりも酸化還元電位の大きい元素を含む合金層17とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高融点金属元素を含むバリアメタル膜と組みあわせてCu配線パターンのバリアメタル構造を形成するCu−Mn合金層において、ストレスマイグレーション耐性を向上させると同時に、Cu配線パターンの抵抗を低減する。また、さらには配線中のボイド欠陥を低減する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上方に形成された酸素を含む絶縁膜と、前記絶縁膜に形成された凹部と、前記凹部の内壁に形成された銅を含む第1の膜と、前記第1の膜上方であって、前記凹部に埋め込まれた銅を含む第2の膜と、前記第1の膜と前記第2の膜の間にマンガンを含む酸化層と、を有する。さらに、前記構造に対し、電解メッキ法で銅配線を形成し、引き続き80℃〜120℃の温度で短時間の熱処理を行う。

(もっと読む)

21 - 40 / 120

[ Back to top ]