Fターム[5F058BA09]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成の目的、効果 (3,596) | 段差被覆性の改善 (222)

Fターム[5F058BA09]に分類される特許

141 - 160 / 222

半導体デバイスの製造方法

【課題】原料とアルコールを交互に処理室に流して薄膜を形成する方法において、スループットの悪化やコストアップを招くことなく、段差被覆性やローディング効果を改善する。

【解決手段】H終端された表面を有するシリコンウエハを処理室内に搬入する工程と、前記処理室内に第1ガスとしてアルコールを供給するアルコール供給工程と、前記処理室内から第1ガスを排出する第1パージ工程と、前記処理室内へ第2ガスとして原料ガスを供給する原料供給工程と、前記処理室内から第2ガスを排出する第2パージ工程と、少なくとも上記アルコール供給工程、第1パージ工程、原料供給工程、および第2パージ工程を1サイクルとし、このサイクルを所定回数繰り返して、前記シリコンウエハ上に所望の薄膜を生成する工程と、前記所望の薄膜を生成したシリコンウエハを前記処理室内から搬出する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】所望の特性を有するトランジスタを精度よく形成する。

【解決手段】トランジスタのエクステンション領域を形成するためのオフセットスペーサとしてシリコン窒化膜を用いる場合に、レジスト膜を除去する工程の前に、シリコン窒化膜表面に酸素プラズマ処理により酸化保護表面を形成しておく。

(もっと読む)

埋込み層に低抵抗コンタクトを形成する打込み領域を含んだ半導体デバイスの製作方法および関連したデバイス

半導体デバイスを製作する方法は、第1のドーパント濃度を有する第1の伝導型の第1の半導体層を形成すること、および第1の半導体層上に第2の半導体層を形成することを含む。第2の半導体層は、第1のドーパント濃度よりも低い第2のドーパント濃度を有する。第2の半導体層を貫通して延びて第1の半導体層に接触する第1の伝導型の打込み領域を形成するように、第2の半導体層中にイオンが打ち込まれる。第1の電極が第2の半導体層の打込み領域上に形成され、第2の電極が、第2の半導体層の非打込み領域上に形成される。関連したデバイスも述べられる。  (もっと読む)

(もっと読む)

STI用の二酸化シリコンの高品質誘電体膜の形成:HARPII−遠隔プラズマ増強型堆積プロセス−のための異なるシロキサンベースの前駆物質の使用

【課題】 基板上に形成されるギャップ内に誘電体層を堆積させる方法を提供する。

【解決手段】 方法は、有機シリコン前駆物質と酸素前駆物質を堆積チャンバに導入するステップを含む。有機シリコン前駆物質のC:Si原子比は、8未満であり、酸素前駆物質は、堆積チャンバの外で生成される原子状酸素を含む。前駆物質が反応して、ギャップ内に誘電体層を形成する。ギャップを誘電材料で充填する方法も記載する。これらの方法は、C:Si原子比が8未満の有機シリコン前駆物質と酸素前駆物質を供給するステップと、前駆物質からプラズマを生成させて、ギャップ内に誘電材料の第一部分を堆積させるステップとを含んでいる。誘電材料がエッチングされてもよく、誘電材料の第二部分がギャップ内に形成されてもよい。誘電材料の第一部分と第二部分がアニールされてもよい。

(もっと読む)

半導体製造装置、半導体製造方法及び電子機器

【課題】薄膜の絶縁物バリアー膜を緻密にして、上記リーク電流の増加を十分に防止できるようにする。

【解決手段】ウェハ7に形成されている配線接続孔に対して絶縁体バリアー膜を形成する手段1031等と、絶縁体バリアー膜に紫外線を照射する手段3等とを有する。詳しくは、ウェハ7が載置されるヒーター6が設置される第一領域Bと、ヒーター6上のウェハ7に紫外線を照射するランプ3が設置される第二領域Aとの間を仕切る仕切り板1068と、第二領域Aに配置されていてクリーニングを行うプラズマ発生用の電極1064とを備える。

(もっと読む)

アニール用治具及びアニール方法

【課題】基板へのパーティクル等の汚染粒子の付着を大幅に減少させることができ、液晶用基板のような大型の基板を処理する場合でも治具内部の基板の処理空間に結露が発生せず、治具に吸着や破損が生じず、均熱空間に収納可能な基板枚数を増大できるアニール用治具及びアニール方法を提供する。

【解決手段】本発明のアニール用治具10Aは、容器本体12の上部が蓋部材16によって閉じられたときの容器本体12と蓋部材16との接触部18に、水蒸気などの処理用ガスの通過を許容し所定の粒径以上のパーティクル等の汚染粒子の通過を阻止する微細流路が形成される。容器本体12は、処理空間11と外部とを連通し基板1が載置部13に載置されたときに基板1によって塞がれる連通路14を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、先に形成されている絶縁膜(例えば、ゲート絶縁膜など)の品質に悪影響を及ぼさず、また、欠陥が少ない絶縁膜をトレンチに埋め込むことができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】反応ガスを分解して基板のトレンチに絶縁膜の埋め込みを行う工程を備えた半導体装置の製造方法であって、前記反応ガスと、少なくともD2(重水素)ガスを含む希釈ガスとを供給して、前記絶縁膜の埋め込みを行うことを特徴とする半導体の製造方法が提供される。

(もっと読む)

ナノラミネート構造誘電膜の形成方法

【課題】半導体装置の大容量化に伴い、キャパシタ誘電膜の製造方法に関し、高い誘電率を有し、かつ高カバレジで平滑な誘電膜の製造方法を提供する。

【解決手段】キャパシタの下部電極上にナノラミネート構造SrO/TiO膜を表面反応律速状態の分子層堆積法で形成させる。TiO膜及びSrO膜は、各々温度150℃以上400℃以下、圧力10Torr以上大気圧以下で、各々1分子層以上、20分子層以下で交互に層状に形成させる。これにより、高誘電率、高カバレジでしかも結晶性異物を発生させないナノラミネート構造SrO膜/TiO膜を得ることができる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】特性を劣化させることなく平坦化が可能な薄膜トランジスタを提供する。

【解決手段】ゲート電極22を覆ってゲート絶縁膜21上に、水素化窒化シリコン膜により層間絶縁膜25を形成する。層間絶縁膜25上に、BPSGとTEOSとのいずれか一方により中間膜を形成する。中間膜を500℃近傍に加熱して流動化させることで平坦化用の平坦化膜26を形成する。中間膜を加熱した際でも、活性層12とゲート絶縁膜21との間の欠陥準位に水素化窒化シリコン膜により形成した層間絶縁膜25から水素原子を充分に供給するので、特性を劣化させることなく平坦化が可能になる。

(もっと読む)

半導体装置の製造方法

【課題】 浅い不純物拡散領域におけるドーパント不純物の拡散を抑制し得る半導体装置の製造方法を提供する。

【解決手段】 半導体基板10上にゲート絶縁膜18を介してゲート電極20を形成する工程と、ゲート電極をマスクとして半導体基板内にドーパント不純物を導入することにより、ゲート電極の両側の半導体基板内に不純物拡散領域28、36を形成する工程と、半導体基板上に、ゲート電極を覆うようにシリコン酸化膜38を形成する工程と、シリコン酸化膜を異方性エッチングすることにより、ゲート電極の側壁部分にシリコン酸化膜を有するサイドウォールスペーサ42を形成する工程とを有する半導体装置の製造方法であって、シリコン酸化膜を形成する工程では、ビスターシャルブチルアミノシランと酸素とを原料として用い、熱CVD法により、500〜580℃の成膜温度で、シリコン酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】アスペクト比が異なる複数の凹部内に効率よく、かつ、容易に膜を埋め込むことができるとともに、凹部に埋め込む膜の埋め込み性の向上、およびクラックや剥がれの抑制を図ることができる半導体装置の製造方法を提供する。

【解決手段】シラン35と過酸化水素36とを基板1上で反応させて流動性を有する液相のシラノール37を生成させる。シラノール37を、基板1に設けられたアスペクト比が所定の値以上である第1の凹部5a内を満たすまで導入するとともにアスペクト比が所定の値未満である第2の凹部5b内にその底部から中間部まで導入する。各凹部5a,5b内のシラノール37を脱水縮合させてシリコン酸化膜8に転換し、凹部5aをシリコン酸化膜8により埋め込むとともに凹部5bの底部から中間部までシリコン酸化膜8を設ける。シリコン酸化膜8よりも膜密度が高い絶縁膜9を凹部5bの中間部から上部を埋め込むまで設ける。

(もっと読む)

シリコン含有前駆物質と原子酸素を用いた高品質流動状二酸化シリコンの化学気相堆積

基板上に酸化シリコン層を堆積する方法が記載される。方法には、堆積チャンバに基板を準備するステップと、堆積チャンバの外部で原子酸素前駆物質を生成させるステップと、原子酸素前駆物質をチャンバへ導入するステップとが含まれ得る。方法には、堆積チャンバにシリコン前駆物質を導入するステップであって、シリコン前駆物質と原子酸素前駆物質が最初にチャンバ内で混合される前記ステップが含まれ得る。シリコン前駆物質と原子酸素前駆物質が反応して、基板上に酸化シリコン層を形成する。基板上に酸化シリコン層を堆積させるシステムも記載される。 (もっと読む)

化合物半導体装置及びその製造方法

【課題】 化合物半導体装置及びその製造方法に関し、パッシベーション効果を保ったままで絶縁膜とレジストとの密着性を改善して、デバイス特性及び信頼性を向上する。

【解決手段】 化合物半導体基体1の表面の少なくとも一部を化合物半導体基体1に接する側4の被覆性が表面側3より高く、且つ、表面側3のレジスト膜に対する密着性が化合物半導体基体1に接する側4より高い窒化珪素系絶縁膜2で被覆する。

(もっと読む)

総合プロセスモジュレーション(IPM)HDP−CVDによるギャップ充填のための新規な解決法

【課題】 ギャップ充填性能が改善された、プロセスチャンバ内に配置された基板上に酸化シリコン膜を堆積させる方法が提供される。

【解決手段】 ハロゲン源、フルーエントガス、シリコン源、酸化ガス反応種を含むプロセスガスがプロセスチャンバに流し込まれる。少なくとも1011イオン/cm3のイオン密度を有するプラズマがプロセスガスから形成される。酸化シリコン膜が、1.0%未満のハロゲン濃度で基板の上に堆積される。酸化シリコン膜は、同時堆積成分とスパッタリング成分を有するプロセスを用いてプラズマにより酸化シリコン膜が堆積される。プロセスチャンバへのシリコン源の流量に対するプロセスチャンバへのハロゲン源の流量は、実質的に0.5〜3.0である。

(もっと読む)

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、半導体基板の主表面側の下地領域 350に形成された凹部351内全体にシリコン窒化膜352を形成する工程と、前記シリコン窒化膜352を酸化して該シリコン窒化膜352をシリコン酸化膜353に変換することにより、前記凹部内全体に絶縁領域を形成する工程とを有することを特徴とする。

(もっと読む)

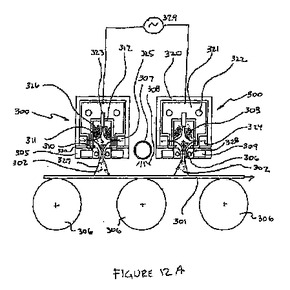

デュアルプラズマビーム源および方法

一対のプラズマビーム源は、交流電源の両端に接続されて、基板上に材料を析出させるためのプラズマイオンビームを交互に生成する。各プラズマビーム源は、第1の幅を有する放電キャビティと、そこから外側に延びてイオンビームを放出するノズルを備える。ノズルの開口又は出口は第2の幅を有し、第2の幅は第1の幅よりも狭い。略互いに向き合う複数の磁石は、各放電キャビティに隣接して配置されて、放電キャビティ内に磁界ヌル領域を生成する。イオン化ガスは、各放電キャビティに注入される。交流電源は、各放電キャビティ内の電極に接続され、各プラズマビーム源は、交互に陽極又は陰極の役割をする。陰極としては、少なくとも1つのマグネトロン放電領域が、放電キャビティ内に維持される。動作においては、高密度の均一なプラズマビームが陰極源から放射し、イオンビームが陽極源から放射する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタを備える半導体装置に関して、膜の表面の粗さ等によるキャパシタの信頼性及び特性の劣化を抑制する。

【解決手段】基板の上にキャパシタ用の下部電極膜を形成し、前記下部電極膜上に強誘電体膜を成膜同時結晶化によって形成し、前記強誘電体膜上にダミー膜を形成し、平坦化処理を通じて前記ダミー膜と前記強誘電体膜の一部とを除去して前記強誘電体膜の表面を平坦化し、前記強誘電体膜上にキャパシタ用の上部電極膜を形成する事を特徴とする半導体装置の製造方法。

(もっと読む)

薄膜形成方法

【課題】薄膜の成膜性を向上させつつ、薄膜を形成させる基材への熱影響を抑制することができる薄膜形成方法を提供する。

【解決手段】大気圧下でのプラズマCVDにより、基材Aの表面に薄膜を形成する薄膜形成方法であって、プラズマCVDにおけるプラズマを発生させるための印加電圧の周波数が5〜90kHzの範囲内に設定され、かつ、薄膜形成時の基材Aの温度が25〜90℃の範囲内に設定される。

(もっと読む)

半導体装置の製造方法

【課題】オゾンTEOS膜をCVD装置で成膜する場合に、高い成膜レートを安定して確保すると共に、均一性良く良好な膜質のオゾンTEOS膜の成膜を可能とする半導体装置の製造方法を提供する。

【解決手段】配線構造が形成された半導体基板上に層間絶縁膜を形成する半導体装置の製造方法であって、配線構造が形成された半導体基板上にプラズマCVDシリコン酸化膜を成膜する第1の層間絶縁膜形成工程と、該第1の層間絶縁膜形成工程により成膜したプラズマCVDシリコン酸化膜の表面改質のためのプラズマ処理を行う表面改質工程と、該表面改質工程により表面の改質が行われたプラズマCVDシリコン酸化膜の上にオゾンTEOS膜を成膜する第2の層間絶縁膜形成工程とを有し、さらに、前記表面改質工程において、表面改質のためのプラズマ処理を行う前に、該プラズマ処理を行う装置内に堆積した堆積物の除去を行う。

(もっと読む)

半導体装置の製造方法

【課題】表面に凸状部を有する半導体基板の表面に、前記凸状部の高さよりも膜厚が薄く、かつその表面が平坦な膜を有する半導体装置の製造方法を提供する。

【解決手段】表面に凸状部300を有する半導体基板100の前記表面に高密度プラズマ−化学気相成長法によりシリコン酸化膜450を堆積させる堆積工程と、堆積させたシリコン酸化膜の表面が前記凸状部の頂上よりも低い高さになるように等方性エッチングにより前記シリコン酸化膜をエッチングするエッチング工程とを備える。

(もっと読む)

141 - 160 / 222

[ Back to top ]