Fターム[5F058BB01]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成基板、処理対象 (706) | 化合物半導体 (165)

Fターム[5F058BB01]の下位に属するFターム

GaAs (27)

Fターム[5F058BB01]に分類される特許

61 - 80 / 138

酸化装置、酸化方法、面発光レーザ素子、面発光レーザアレイ、光走査装置、画像形成装置、光伝送モジュール及び光伝送システム

【課題】酸化距離のばらつきが小さい酸化装置を提供する。

【解決手段】水蒸気を発生させる水蒸気発生装置と、該水蒸気発生装置で発生した水蒸気を酸化温度近くまで加熱する水蒸気加熱装置5030と、該水蒸気加熱装置5030で加熱された水蒸気が供給され、該水蒸気の温度を維持するヒータを有する酸化反応器5040と、開閉可能な隔壁5060を介して酸化反応器5040と連結された準備室5050と、酸化対象物を加熱するヒータを有し、酸化対象物が載置されるテーブル装置と、該テーブル装置を駆動し、酸化開始時に酸化対象物を準備室5050から酸化反応器5040に移動させ、酸化終了後に酸化対象物を酸化反応器5040から準備室5050に移動させる駆動装置とを備えている。

(もっと読む)

半導体素子の製造方法および半導体素子

【課題】オン抵抗の増加を抑制できる、絶縁ゲート型電界効果部を有する半導体素子の製造方法および半導体素子を提供する。

【解決手段】絶縁ゲート型電界効果部を有する半導体素子の製造方法であって、以下の工程を備えている。まず、半導体層11aが形成される。そして、半導体層11a上に、窒化絶縁膜15が形成される。そして、窒化絶縁膜15上に、ゲート電極16が形成される。上記窒化絶縁膜15を形成する工程では、主要成分としてアンモニアを含まない原料ガスを用いて、または物理蒸着法を用いて、窒化絶縁膜15を形成する。

(もっと読む)

半導体装置の製造方法

【課題】安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上にGaN系半導体層を形成する工程と、ALD装置内で、ゲート絶縁膜の成長温度に比べ高い温度で熱処理を実施し、前記GaN系半導体層の表面のフッ素を除去する工程S20と、前記フッ素を除去する工程S20の後、前記ALD装置内で、前記GaN系半導体層の表面に前記ゲート絶縁膜を形成する工程S16と、前記ゲート絶縁膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜におけるリーク電流を抑制し、安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上10にGaN系半導体層15を形成する工程と、GaN系半導体層上15に、TMAと、O2またはO3とを用い、酸化アルミニウムからなるゲート絶縁膜18をALD法により形成する工程と、ゲート絶縁膜18の上にゲート電極24を形成する工程と、を含む。本半導体装置の製造方法によれば、ゲート絶縁膜中のリーク電流を抑制し、安定なFET特性を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】 特性に優れたMOSトランジスタを得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 第1の酸化性雰囲気での第1の熱酸化処理によってSiC領域17上にゲート酸化膜21を形成する工程と、第1の熱酸化処理の後に、第1の酸化性雰囲気の酸素濃度よりも低い酸素濃度を有する第2の酸化性雰囲気において5nm/時以下の酸化速度で第2の熱酸化処理を行い、ゲート酸化膜の膜厚を増加させる工程と、膜厚の増加したゲート酸化膜上にゲート電極22を形成する工程とを備える。

(もっと読む)

トンネル素子およびその製造方法。

【課題】大きなトンネル電流が流れ、かつ接合抵抗の制御性のよいトンネル素子およびその製造方法を提供すること。

【解決手段】本発明は、GaAsを含む半導体膜10と、半導体膜10上に設けられた酸化ガリウム膜20と、酸化ガリウム膜20上に設けられた導電性膜30と、を具備し、酸化ガリウム膜20は、半導体膜10および導電性膜30の一方から他方にトンネル電流が流れるトンネル絶縁膜であるトンネル素子およびその製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】MIS−HEMTにおいて、閾値電圧の低下を抑制する。

【解決手段】半導体装置は、基板19と、この基板上に形成されており、電子走行層13及び電子供給層15が順次積層されて形成された積層構造体17とを含む下地11を具えている。この下地の下地面には、互いに離間し、かつ対向して第1及び第2主電極が形成されている。そして、下地面11aの、これら第1主電極41a及び第2主電極41b間に挟まれた領域内に、ゲート形成用凹部27が形成されている。更に、半導体装置はゲート絶縁膜29を具えている。そして、このゲート絶縁膜は、最小でも2.9g/cm3の結晶密度で形成されている。また、半導体装置は、ゲート絶縁膜が形成された前記ゲート形成用凹部を埋め込むゲート電極43を具えている。

(もっと読む)

半導体レーザ

【課題】高出力長時間駆動時の共振器端面における端面保護膜の膜剥がれを抑制でき、COD耐性の高い、高出力かつ長寿命の窒化物半導体レーザ素子を提供すること。

【解決手段】活性層5の端面からレーザ光を出射する半導体レーザであって、レーザ光が出射される端面上に設けられるとともに、単層または多層の誘電体膜からなる保護膜20を備える。保護膜20中の水素濃度分布は略平坦である。活性層5は、Gaを構成元素として含むIII族窒化物半導体からなる。保護膜20は、少なくとも活性層5の端面と直接接する第一保護膜21と、第一保護膜21に接する第二保護膜22とからなる。第二保護膜22の水素濃度に対する第一保護膜21の水素濃度の比は、0.5以上かつ2以下である。

(もっと読む)

炭化ケイ素半導体装置およびその製造方法

【課題】高いチャネル移動度を再現性良く実現することができる炭化ケイ素半導体装置およびその製造方法を提供する。

【解決手段】{0001}面に対して50°以上65°以下の範囲内で傾いている表面を有する炭化ケイ素からなる半導体層と、半導体層の表面に接触するように形成された絶縁膜とを備え、半導体層と絶縁膜との界面から10nm以内の領域における窒素濃度の最大値が1×1021cm-3以上であって、半導体層の表面内において<−2110>方向に直交する方向±10°の範囲内にチャネル方向を有する炭化ケイ素半導体装置とその製造方法である。

(もっと読む)

III−V族化合物半導体基板の製造方法、エピタキシャルウエハの製造方法、III−V族化合物半導体基板およびエピタキシャルウエハ

【課題】酸化膜の厚みを精度よく制御でき、かつエピタキシャル層を形成したときに表面荒れを抑制するIII−V族化合物半導体基板の製造方法、エピタキシャルウエハの製造方法、III−V族化合物半導体基板およびエピタキシャルウエハを提供する。

【解決手段】III−V族化合物半導体基板の製造方法は、以下の工程が実施される。まず、III−V族化合物半導体からなる基板が準備される(S11)。そして、この基板が酸性溶液で洗浄される(S12)。そして、洗浄する工程後に、湿式法により基板上に酸化膜が形成される(S13)。

(もっと読む)

トランジスタ

【課題】トラッピングを少なくするためにAlGaN層を薄くし、またゲート漏洩を減少させるために層を追加して最大駆動電流を増加させるようにする。

【解決手段】高比抵抗半導体層20と、この高比抵抗半導体層20上に設けられたバリア半導体層18と、このバリア半導体層18に接触するするとともに、バリア半導体層18の表面部を被覆していないソースおよびドレインコンタクト13,14と、バリア半導体層18の被覆されていない表面上に設けられた絶縁層24と、この絶縁層24上に設けられ、ゲート漏洩のバリアを形成するゲートコンタクト16とを備えている。

(もっと読む)

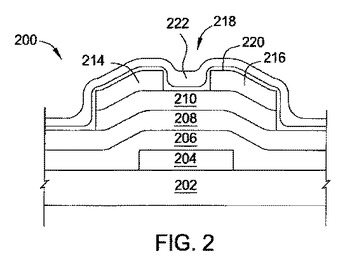

金属酸窒化物TFT用キャッピング層

キャッピング層は、汚染からアクティブチャネルを保護するために、薄膜トランジスタ(TFT)のアクティブチャネルの上に堆積してもよい。キャッピング層は、TFTの性能に影響するかもしれない。キャッピング層があまりに多量の水素、窒素、又は酸素を含んでいるならば、TFTの閾値電圧、サブスレショルドスロープ、及び移動度に否定的に影響を与えるかもしれない。窒素、酸素、及び水素含有ガスの流速の比率を制御することによって、TFTの性能が最適化されるかもしれない。更に、電力密度、キャッピング層堆積圧、及び温度も、TFT性能を最適化するために制御してもよい。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】GaN基板表面の窒素抜けを抑制し、耐圧の高い半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明の半導体装置の製造方法は、窒化ガリウムを含む半導体層を準備する工程と、半導体層の表面を水素ガスにより処理する表面処理工程と、表面処理工程後の上記表面を酸化する酸化工程とを備える。

(もっと読む)

半導体基板、半導体基板の製造方法および半導体装置

【課題】半導体−絶縁体界面の界面準位が低減した半導体基板とその製造方法および半導体装置を提供する。

【解決手段】砒素を含む3−5族化合物の半導体層と、酸化物、窒化物または酸窒化物の絶縁層と、を備え、前記半導体層と前記絶縁層との間に砒素の酸化物が検出されない半導体基板が提供される。当該第1の形態において半導体基板は、前記半導体層と前記絶縁層との間に存在する元素を対象としたX線光電子分光法による光電子強度の分光観察において、砒素に起因する元素ピークの高結合エネルギー側に、酸化された砒素に起因する酸化物ピークが検出されないものであってよい。

(もっと読む)

n型の化合物半導体基板と金属膜の積層体と、そのリーク電流の低下方法

【課題】 n型の化合物半導体と金属膜が積層されている積層体において、化合物半導体と金属膜の間に流れるリーク電流を低下させる方法を提供する。

【解決方法】 n型の化合物半導体基板6に金属膜2を積層した後に、化合物半導体基板6に正電圧を印加して金属膜2を陽極酸化する。この際に、化合物半導体基板6と金属膜2の間にリーク電流30が流れる。リーク電流30は結晶欠陥32に集中し、結晶欠陥32の存在箇所に対応する金属膜2の表面2aに厚い酸化物34が形成される。酸化物34が形成されることによって、リーク電流30が結晶欠陥32に沿って流れにくくなり、化合物半導体基板6と金属膜2の間に流れるリーク電流30を低下させることができる。

(もっと読む)

半導体装置の製造方法

【課題】シリコンリッチ窒化シリコン膜に起因した不安定な現象を抑制すること。

【解決手段】本発明はGaN系またはInP系化合物半導体からなる半導体層11の上に屈折率が2.2以上の第1窒化シリコン膜12を形成する工程と、第1窒化シリコン膜12より屈折率の低い第2窒化シリコン膜14を第1窒化シリコン膜12上に形成する工程と、半導体層11を露出させた領域にソース電極16およびドレイン電極18を形成する工程と、第1窒化シリコン膜12および第2窒化シリコン膜14が形成された状態でソース電極16およびドレイン電極18を熱処理する工程と、ソース電極16とドレイン電極18との間の半導体層11上にゲート電極を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、デバイス特性及び信頼性を向上させる。

【解決手段】半導体装置を、半導体基板6上に形成された化合物半導体積層構造1と、少なくとも化合物半導体積層構造1の表面に露出している部分を覆う第1絶縁膜4と、第1絶縁膜4上に形成された第2絶縁膜5とを備えるものとし、第2絶縁膜5を第1絶縁膜4よりも水素を多く含むものとする。

(もっと読む)

半導体光素子を作製する方法

【課題】埋め込み層の成長に際して異常成長を低減可能な、半導体光素子を作製する方法を提供する。

【解決手段】誘導結合型プラズマCVD装置を用いて、そのバイアス電力PBIASを制御することによって膜応力を調整して、複数のIII−V化合物半導体層を含む半導体積層上に、厚さ2マイクロメートル以上のシリコン酸化膜を成長する。シリコン酸化膜のマスクを半導体積層上にエッチングにより形成する。このマスクを用いて半導体積層をドライエッチングして光導波路構造のための半導体メサを形成する。マスクを用いて半導体メサの埋め込み成長を行う。マスクのシリコン酸化膜の室温における膜応力は、−250MPa〜−150MPaである。膜応力は、摂氏500度〜摂氏700度の温度範囲で−200MPa〜ゼロMPaである。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】シートキャリア濃度を向上させると共に、シートキャリア濃度の向上効果を有効に利用する電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板11の上に形成された第1の窒化物半導体層13と、第1の窒化物半導体層13の上に形成され、第1の窒化物半導体層13と比べてバンドギャップが大きい第2の窒化物半導体層14と、第2の窒化物半導体層14の上に形成された結晶性の窒化シリコンからなる第1の絶縁膜15と、第1の絶縁膜15の上に形成された第2の絶縁膜16とを備えている。第2の絶縁膜16の上には、ゲート電極21が形成されている。ゲート電極21の両側方にはソース電極22及びドレイン電極22が形成されている。

(もっと読む)

III族窒化物半導体を用いた電界効果トランジスタ

【課題】絶縁膜と半導体層の界面準位を効果的に低減し,大電流を流すことのできるIII族窒化物半導体を用いた電界効果トランジスタを提供する。

【解決手段】GaN系MOSFETは、基板1と、基板1上に形成されたバッファ層2と、バッファ層2上に形成されたp型GaN層の半導体層3と、半導体層3のチャネル領域上にSiO2から成るゲート酸化膜5を介して形成されたゲート電極8と、ソース電極6及びドレイン電極7と、半導体層3のチャネル領域の両側に形成され、ソース電極6及びドレイン電極にそれぞれオーミック接触するコンタクト領域4s及び4dとを備える。ゲート酸化膜5であるSiO2をバッファードふっ酸(BHF約7%)でエッチングした場合のエッチングレートを、1 nm/sec以上3 nm/sec以下とした。

(もっと読む)

61 - 80 / 138

[ Back to top ]