Fターム[5F058BH02]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成後の処理 (2,470) | 熱処理(後処理) (1,507) | 雰囲気 (896)

Fターム[5F058BH02]の下位に属するFターム

Fターム[5F058BH02]に分類される特許

101 - 120 / 207

炭化珪素半導体装置およびその製造方法

【課題】炭化珪素半導体装置のチャネル移動度の向上を図る。

【解決手段】ゲート酸化膜形成工程の降温時に、ウェット雰囲気を維持したまま、終端・脱離温度(800〜900℃)以下まで降温させる。これにより、ゲート酸化膜とチャネル領域を構成するp型ベース層の界面のダングリングボンドをHもしくはOHの元素で終端させることが可能となる。このため、高いチャネル移動度の反転型ラテラルMOSFETとすることが可能となる。

(もっと読む)

SiC形成方法、膜形成方法、チャンバへのSiC形成方法、半導体製造装置の製造方法、SiC形成装置及びこれらで形成された膜構造

【課題】基板上やチャンバ内壁面にSiCの形成を可能とする。

【解決手段】チャンバ10内の基板22aへ珪素を供給すると共に、チャンバ10内へハロゲン含有ガスを供給し、ハロゲン含有ガスを解離して炭素含有部材20bから基板22aへ炭素を供給することによって基板22aにSiCを形成する。

(もっと読む)

絶縁膜形成用組成物、ならびにシリカ系膜およびその形成方法

【課題】吸湿性が低く、低比誘電率であり、かつ機械的強度に優れた絶縁膜形成用組成物ならびにシリカ系膜およびその形成方法を提供する。

【解決手段】(A)成分;下記一般式(1)で表される化合物100〜10モル%及び(B)成分;下記一般式(2)で表される化合物0〜90モル%を加水分解縮合して得られたポリマーと、有機溶媒と、を含有する。R1aX3−aSi−(R3)c−SiX’3−bR2b ・・・・・(1) (式中、R1、R2は、水素原子、アルキル基、アルケニル基、アルキニル基を表し、X、X’はハロゲン原子を表し、R3は酸素原子、フェニレン基または−(CH2)m−で表される基(mは1〜6の整数)を表し、a、bは0〜3の整数を示し、cは0または1を示す。)R4dSiX”4−d ・・・・・(2) (式中、R4は前記R1、R2と同じ基を表し、X”はハロゲン原子またはアルコキシル基を表し、dは0〜3の整数を示す。)

(もっと読む)

絶縁膜形成用組成物、ならびにシリカ系膜およびその形成方法

【課題】高集積化および多層化が望まれている半導体素子などにおいて好適に用いることができ、貯蔵安定性に優れ、かつ、低比誘電率であり、機械的強度に優れた絶縁膜の形成に用いることができる絶縁膜形成用組成物、シリカ系膜およびその形成方法を提供する。

【解決手段】絶縁膜形成用組成物は、(A)成分;下記一般式(1)で表される化合物および下記一般式(2)で表される化合物の群から選ばれた少なくとも1種のシラン化合物50〜100モル%と、(B)成分;他の加水分解性シラン化合物0〜50モル%とを加水分解縮合して得られた加水分解縮合物と、有機溶媒と、を含み、pHが3.0〜5.0の範囲にあり、かつ、含有水分量が2質量%以下である。

Si(OR1)4 ・・・・・(1)

(式中、R1は1価の有機基を示す。)

R2a(R3O)3−aSi−(R6)c−Si(OR4)3−bR5b ・・・(2)

(式中、R2〜R5は同一または異なり、それぞれ1価の有機基を示し、aおよびbは同一または異なり、0〜1の数を示し、R6は酸素原子、フェニレン基または−(CH2)m−で表される基(ここで、mは1〜6の整数である。)を表し、cは0または1を示す。)

(もっと読む)

PSZ膜の熱処理方法及びこれを適用した半導体素子の素子分離膜形成方法

【課題】素子分離膜形成材料としてPSZ物質を用い、PSZ物質に多量で含有された不純物を容易に除去しながらボイドやシームのない素子分離膜を形成する方法を提供する。

【解決手段】酸素ガスが供給されるチャンバの内部にPSZ膜が形成されたウェハをローディングさせる段階と、前記チャンバの内部の温度を工程温度まで上昇させる段階と、水蒸気をチャンバの内部に供給し、前記酸素ガスの量と前記水蒸気の量の割合が1:1〜50:1の条件を維持する状態で前記PSZ膜を硬化させる段階と、前記チャンバの内部をパージさせる段階と、アンローディング温度まで下降させる段階と、前記ウェハを前記チャンバの外部にアンローディングさせる段階を含んでPSZ膜を熱処理し、半導体素子の素子分離膜を形成する。

(もっと読む)

処理方法および記憶媒体

【課題】良好な処理特性を維持しつつ従来よりも高スループットでシリル化処理を行うことができる処理方法を提供すること。

【解決手段】被処理基板を処理室に搬入後、SiとCH3との結合を有するガスを処理室内に導入し、被処理基板に対してシリル化処理を施す処理方法であって、処理室内にSiとCH3との結合を有するガスを供給して処理室内の圧力を上昇させ、所定圧力に到達してから処理室内の圧力を搬出圧力まで低下させるまでの間、SiとCH3との結合を有するガスの供給による前記処理室内の圧力と供給時間を、所定のシリル化処理を施すことが可能な範囲とする。

(もっと読む)

低誘電率膜の改質剤及び製造方法

【課題】 半導体デバイス製造時に使用される低誘電率膜の比誘電率を低下させるための改質剤、およびその改質剤を用いて改質された低誘電率膜を製造する方法を提供する。

【解決手段】 半導体デバイスに使用される低誘電率膜の比誘電率を低下させるための改質剤であって、一般式(1)

R3−xHxSiN3 (1)

(RはC1〜C4のアルキル基、nは0〜3の整数)で表されるケイ素化合物を有効成分として少なくとも一種類以上含有する低誘電率膜の改質剤。

(もっと読む)

フラッシュメモリの製造方法

【課題】高圧湿式熱処理を通じてブロッキング絶縁膜内のトラップサイトを除去することで電荷のブロッキング効率を向上させることができるフラッシュメモリの製造方法を提供する。

【解決手段】 本発明は、半導体基板上にトンネリング絶縁膜を形成する段階と、トンネリング絶縁膜上に電荷貯蔵膜を形成する段階と、電荷貯蔵膜上にブロッキング絶縁膜を形成する段階と、ブロッキング絶縁膜が形成された半導体基板に対して高温熱処理を遂行する段階と、高温熱処理が遂行された半導体基板に対して低温湿式熱処理を遂行する段階とを有し、低温湿式熱処理は、2〜100気圧の雰囲気で遂行し、前記ブロッキング絶縁膜の酸素欠陥を修復し、界面欠陥を修復するために水蒸気を用いるフラッシュメモリの製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】 電流駆動力が大きく、誘電率の大きなシリコン酸化膜とシリコン窒化膜の積層膜を作る。

【解決手段】 半導体装置の製造方法は、シリコン酸化膜の上にアモルファスシリコン膜を形成する工程と、前記アモルファスシリコン膜をアニールして単結晶シリコン膜を形成する工程とを有する。

(もっと読む)

高次シラン組成物、膜付基板の製造方法、電気光学装置および電子デバイス

【課題】液相プロセスを用いて、安定かつ所望な膜厚の膜を形成することができる高次シラン組成物、かかる高次シラン組成物により製造される膜付基板の製造方法、膜付基板を備える電気光学装置および電子デバイスを提供すること。

に関するものである。

【解決手段】高次シラン組成物は、高次シラン化合物と、置換または無置換の炭化水素系溶媒を含む溶媒とを含有し、前記溶媒として、前記高次シラン化合物が溶解し得るように、屈折率が1.53以上のものを選択する。また、炭化水素系溶媒は、比誘電率が10以下であるのが好ましい。

(もっと読む)

ゲート絶縁膜、ゲート絶縁膜の評価方法、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合においても、SBDが生じ難いゲート絶縁膜、かかるゲート絶縁膜の評価方法を提供する。

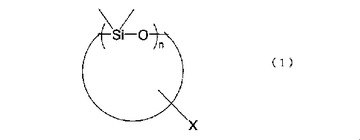

【解決手段】ゲート絶縁膜3は、下記一般式(1)で表される構造を有しており、下記一般式(1)で表される構造中のnが3または4であるものの総数をAとし、nが5以上であるものの総数をBとしたとき、{A/(A+B)}×100が1.2%以下なる関係を満足することにより、ソフトブレークダウンが生じるまでに流れる総電荷量が、40C/cm2以上となるよう構成されている。

[式中、nは2以上の整数を表す。また、Xは水素原子または水酸基を表す。]

(もっと読む)

酸化シリコン薄膜の製造装置及び形成方法

【課題】本願発明の課題は、可塑性を有するプラスチック基板等に対して、基板の耐熱温度以下における低温印刷プロセスにより、現在電子デバイスとして使用されているものと同等の高い絶縁性能を有する酸化シリコン薄膜を用いる半導体薄膜素子及びその形成方法を提供することである。

【解決手段】可塑性を有するプラスチック基板上にシラザン構造又はシロキサン構造を含むケイ素化合物の塗布膜を形成し、該塗布膜を酸化シリコン薄膜に転化し、該薄膜を絶縁層又は封止層の一部とすることにより半導体薄膜素子を形成する。

(もっと読む)

熱処理方法、熱処理装置及び記憶媒体

【課題】塗布膜を焼成する際に発生するパーティクルの抑制効果のより高い熱処理方法、熱処理装置及び前記方法を記憶した記憶媒体を提供する。

【解決手段】基板を反応容器3内に搬入して、基板に塗布されたポリシラザン膜等の塗布膜に熱処理を施して絶縁膜へと焼成するにあたって、反応容器3内の圧力を6.7kPa(50torr)以上26.7kPa(200torr)以下に減圧した状態で、この反応容器3内の温度を予熱温度から焼成を行う処理温度まで昇温する。

(もっと読む)

容量素子を有する半導体装置及びその製造方法

【課題】 半導体装置の大容量化に適したリーク電流が少なく、かつ高い誘電率を有する誘電膜の製造方法を提供する。

【解決手段】

第1の電極層上に酸化ストロンチュウムの非晶質膜を1原子層から数原子層の厚さ形成し、酸化ストロンチュウムの非晶質膜上に酸化チタンの非晶質膜を1原子層から数原子層形成し、酸化ストロンチュウム非晶質膜と酸化チタン非晶質膜との積層膜を結晶化開始温度に近い温度で熱処理を行い、積層膜を内部に複数の結晶粒を含む単層のチタン酸ストロンチュウム非晶質膜に変換することによって誘電体膜を形成する。積層膜は、交互に形成された酸化ストロンチュウム非晶質膜と前記酸化チタン非晶質膜を複数有してもよい。半導体装置は、内部に複数の結晶粒を含む単層のチタン酸ストロンチュウム非晶質膜を誘電体膜とするキャパシタを含む。

(もっと読む)

ゲートスタック構造の順次処理のクラスター化方法

シリコンおよび酸素を備えるゲート誘電体を形成するための方法が提供される。該ゲート誘電体はまた、窒素または別の高k材料を含んでもよい。一態様では、該ゲート誘電体を形成するステップは、酸化シリコン層を形成するために酸化雰囲気において基板をアニーリングする工程と、気相堆積法によって該酸化シリコン層上に窒化シリコン層や高k層を堆積する工程と、該窒化シリコン層や高k層の上部表面を酸化する工程と、該基板をアニーリングする工程とを含む。該ゲート誘電体は、集積処理システム内に形成されてもよい。 (もっと読む)

半導体装置の製造方法

【課題】積層構造の容量絶縁膜を有するキャパシタの形成に際して、酸化金属膜と下部電極を構成する多結晶シリコン膜との間に介在させる酸窒化シリコン膜の厚みの制御性を高める。

【解決手段】下地11上に下部電極12を構成する多結晶シリコン膜を形成する工程と、下部電極12上に、酸窒化シリコン膜15を形成する工程と、酸窒化シリコン膜15上に、酸化タンタル膜16を形成する工程と、酸化タンタル膜16を熱処理する工程と、酸化タンタル膜16上に、上部電極14を構成するTiN膜を形成する工程とを有する。酸化タンタル膜16を熱処理する工程は、酸窒化シリコン膜15を形成する工程で使用する最も高い基板温度よりも低い基板温度で行う。

(もっと読む)

低誘電率非晶質シリカ系被膜の形成方法および該方法より得られる低誘電率非晶質シリカ系被膜

【課題】 比誘電率が3.0以下と小さく、しかもヤング弾性率が3.0 GPa以上の被膜強度を有する低誘電率非晶質シリカ系被膜を基板上に安定的に形成する方法に関する。

【解決手段】 (a)テトラアルキルアンモニウムハイドロオキサイド(TAAOH)の存在下で加水分解して得られる有機ケイ素化合物の加水分解物を含む液状組成物を基板上に塗布する工程、(b)必要に応じて、前記基板を装置内に収納し、該基板上に形成された被膜を25〜340℃の温度条件下で乾燥する工程、(c)前記装置内に過熱水蒸気を導入し、前記被膜を105〜450℃の温度条件下で加熱して加熱処理する工程、および(d)必要に応じて、前記装置内に窒素ガスを導入して、前記被膜を350〜450℃の温度条件下で焼成する工程を含む各工程で少なくとも処理することを特徴とする低誘電率非晶質シリカ系被膜の形成方法。

(もっと読む)

低誘電率非晶質シリカ系被膜の形成方法および該方法より得られる低誘電率非晶質シリカ系被膜

【課題】 比誘電率が3.0以下と小さく、しかもヤング弾性率が3.0 GPa以上の被膜強度を有する低誘電率非晶質シリカ系被膜を基板上に安定的に形成する方法に関する。

【解決手段】 (a)テトラアルキルアンモニウムハイドロオキサイド(TAAOH)の存在下で加水分解して得られる有機ケイ素化合物の加水分解物を含む液状組成物を基板上に塗布する工程、(b)前記基板を装置内に収納し、該基板上に形成された被膜を25〜340℃の温度条件下で乾燥する工程、(c)前記装置内に水蒸気を導入し、前記被膜を105〜450℃の温度条件下で加熱して加熱処理する工程、および(d)前記装置内に窒素ガスを導入して、前記被膜を350〜450℃の温度条件下で焼成する工程を含む各工程で少なくとも処理することを特徴とする低誘電率非晶質シリカ系被膜の形成方法。

(もっと読む)

半導体装置の製造方法及び装置

【課題】ダングリングボンドを水素ではなく重水素で終端することができ、かつ900℃に達するような高温処理を必要とすることなく、十分な重水素を導入することができる半導体装置の製造方法及び装置を提供する。

【解決手段】半導体基板1の表面に酸化膜を形成する酸化膜形成工程S11と、次いで、半導体基板を大気圧よりも高い圧力の高圧重水蒸気2に晒す高圧重水蒸気処理工程S12とを有し、これにより、あらかじめ形成した酸化膜中に重水素を導入する。

(もっと読む)

MIS型半導体装置

【課題】 金属酸化物又は金属酸窒化物からなる高誘電率膜を半導体材料と直接接合させても1011 cm-2eV-1台の界面準位密度を維持できるMIS型半導体装置を得ることを課題とする。

【解決手段】 金属酸化物又は金属酸窒化物と半導体材料の接合界面において、半導体原子と異種原子との結合が一分子層以下であることを特徴としたMIS型半導体装置によって解決される。

(もっと読む)

101 - 120 / 207

[ Back to top ]