Fターム[5F064BB35]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082) | 安全 (357)

Fターム[5F064BB35]に分類される特許

41 - 60 / 357

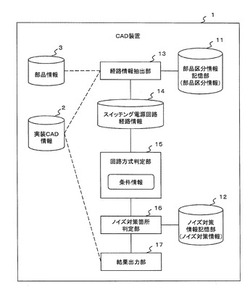

スイッチング電源回路方式判定処理方法,CAD装置およびCADプログラム

【課題】 CAD装置で,スイッチング電源回路の方式を自動的に判別することを目的とする。

【解決手段】 CAD装置1は,判別対象とするスイッチング電源回路が配置されている基板に実装される部品およびネットの情報を示す実装CAD情報2,ならびに前記基板に配置される各部品の部品種別,部品内部の透過接続情報およびピン属性を示す部品情報3をもとに,スイッチング電源回路から開始かつ終了する経路を抽出し,該経路に接続する部品および接続関係を示すスイッチング電源回路経路情報14を生成する経路情報抽出部13と,スイッチング電源回路の経路に接続する部品および接続関係にもとづいてスイッチング電源回路の方式を定める条件をもとに,スイッチング電源回路経路情報14から,判定対象のスイッチング電源回路の方式を判定する回路方式判定部15とを備える。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

レイアウト設計方法、レイアウト設計プログラム及びレイアウト設計装置

【課題】被クリップセルとクリップセル間の配線引き回しを抑え、配線引き回しに起因した不具合を回避する。

【解決手段】レイアウト設計において、ネットリストを用い、被クリップセルと、その被クリップセルに接続されるクリップセルとを抽出し(ステップS1)、抽出された被クリップセルとクリップセルとを関連付けた関連付け情報を生成する(ステップS2)。そして、生成された関連付け情報に基づき、被クリップセルとクリップセルとを隣接させる等して一体で配置し(ステップS3)、配置された被クリップセルとクリップセルとを配線で接続する(ステップS4)。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

書き込み制御回路及び半導体装置

【課題】電気的に1回限りの書き込みが行われる記憶素子への誤書き込みを抑制する。

【解決手段】電圧検出部12は、電気的に1回限りの書き込みが行われる記憶素子(電気ヒューズ素子2)へ供給される書き込み電圧を検出し、書き込み電圧が所定の閾値電圧以上となると、書き込み制御部11に、書き込み信号に係わらず電気ヒューズ素子2への書き込みを停止させることで、書き込み電圧に異常が発生し、過電圧になることによる誤書き込みを抑制できる。

(もっと読む)

半導体装置

【課題】電源遮断がされる領域同士の場合であっても生じる、電源遮断移行時および復帰時の貫通電流の問題を解決しつつアイソレーション回路を不要とする半導体装置を提供する。

【解決手段】半導体装置は、第1の電源線601と、第1のスイッチ605を介して第1の電源線に接続される第2の電源線101、および第2の電源線に接続されるマクロセルコア508を有するマクロセルと、第2のスイッチ603を介して第1の電源線に接続される第3の電源線602と、第3の電源線に接続され、マクロセルコアの入力または出力の少なくともいずれかに接続される回路ブロック501とを備え、第2の電源線と第3の電源線とが接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】銅を主成分とする配線層を有し、かつヒューズの切断によって特性の悪化を招くことのない半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、銅を主成分とするメタル配線34と、メタル配線34よりも上層に形成された最上層配線5と、メタル配線34と最上層配線5との間を接続するためのプラグ9が形成されるプラグ形成層10に少なくとも一部が形成され、銅以外の金属材料を主成分とする導電性材料で形成されたヒューズ膜4とを含む。

(もっと読む)

チャージアップダメージの検証方法および検証装置

【課題】 配線と非配線とを分けて扱い、マクロ等にも半導体集積回路全体にも適用できるアンテナルールを用いるチャージアップダメージの検証方法等を提供できる。

【解決手段】 配線層毎のアンテナ比の上限値を、注目配線層の階層数と総配線層数とに基づいて設定する第1のステップS10、半導体集積回路のレイアウトデータに基づいて、配線層毎に所与のゲートにチャージアップダメージを与えるノードの面積を演算し、下位の配線層に含まれる同一のノードの面積との積算値を求める第2のステップS20、半導体集積回路のモジュール毎に、注目モジュールに含まれる所与のゲートにチャージアップダメージを与えるノードについて、注目モジュールの最上位配線層までの面積の積算値と所与のゲートの面積とに基づいてアンテナ比を求め、注目モジュールの最上位配線層におけるアンテナ比の上限値と比較する第3のステップS30を含む。

(もっと読む)

集積回路内における、インターフェースデバイスの面積効率の良い配列

【課題】過度にシステムの中にスキューを増加させずに、増加した数の入力/出力デバイスを有するシステムを提供する。

【解決手段】論理回路を備えるコアと、処理コアからおよび処理コアへ信号を伝送するための、複数のインターフェースデバイスであって、2つのタイプのインターフェースデバイスを備える、複数のインターフェースデバイスと、コアに電力を送達するための、電力インターフェースデバイスである、1つのタイプと、コアと集積回路の外部のデバイスとの間で、データ信号を伝送するための信号インターフェースデバイスである、第2のタイプと、を備え、複数のインターフェースデバイスは、コアの外縁に向かう外側列、およびコアの中心により近い外側列の内側にある内側列の、2列に配設され、内側列は、2つのタイプのインターフェースデバイスのうちの一方を備え、外側列は、2つのタイプのインターフェースデバイスのうちの他方を備える、集積回路が開示される。

(もっと読む)

半導体装置

【課題】積層チップシステムにおいて、各チップのIO回路の大きさを、そのドライブ能力やESD耐性能力を維持した上で、従来のサイズから縮小し、積層システムでは積層数に応じてIO数を変化させることができる半導体装置を提供する。

【解決手段】積層チップシステムにおいて、各チップは、各IO用の貫通ビア接続用パッド201に接続するIO回路202、スイッチ回路206にてIOチャネル207を構成し、このIOチャネル207を最大積層予定数のIOチャネル分まとめて接続してIOグループを構成し、このIOグループを1個以上持つ。各IO用の貫通ビア接続用パッド201は、貫通ビアにて別層のチップの同一位置のIO端子と接続される。インターポーザにおいては、実際の積層数が最大積層予定数に満たない場合はインターポーザ上で隣接するIOグループ内のIO用の接続用パッドが導体で接続されている。

(もっと読む)

半導体装置の設計支援装置、キャパシタ配置方法、及びプログラム

【課題】回路の周波数特性に応じたキャパシタが適切に配置されず、電源ノイズ耐性の高い半導体装置を設計することが困難であり、また必要な容量を満たすためにより多くのキャパシタセルを挿入する必要があった。

【解決手段】半導体装置の設計支援装置1は、LSIの配置配線情報201、及びLSIの遅延要素から成る遅延ライブラリ情報202に基づき、LSI内に配置されている各論理セルの負荷容量値をそれぞれ算出する負荷容量値算出部103と、負荷容量値算出部103で算出された負荷容量値に基づいて、各論理セルの周波数帯域をそれぞれ判定し、キャパシタを配置する対象となる論理セルの周辺部の空き領域に、当該判定結果に対応した周波数特性を有するキャパシタを配置するデカップリングキャパシタ配置部104とを備える。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

半導体集積回路の配線検証方法、配線検証装置、及び配線検証プログラム

【課題】高速に、且つ設計上の制約を増大させることなく配線のエレクトロマイグレーション耐性を検証することが可能な配線検証方法を提供することである。

【解決手段】本発明にかかる配線検証方法は、検証対象回路のネットリストと配線容量/抵抗情報とを用いて配線のIavg/Irms値を算出し、算出された配線のIavg/Irms値が予め定められたIavg/Irms規定値を超えている場合にIrms規定値を緩和し、緩和されたIrms規定値に応じてIavg規定値を制限し、予め定められたIrms規定値および緩和されたIrms規定値を用いて算出された配線寿命が予め定められた配線寿命の規定値を満たすか否かを検証し、算出された配線のIavg/Irms値のそれぞれが制限されたIavg規定値と緩和されたIrms規定値を超えているか再度検証する。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

半導体集積回路

【課題】例えばクラック発生などに起因する大量生産段階での低歩留りという問題を防止できる半導体集積回路を提供する。

【解決手段】パッドメタルの下に回路を有する半導体集積回路において、パッド開口部分のパッドメタルの少なくとも下全面に、互いに同一の電位を有する配線メタルを形成し、当該配線メタルの電位を上記パッドメタルと異なる電位に設定した。また、上記配線メタル、及び上記配線メタル以外の電位を有する別の配線メタルは、上記パッドメタルよりも下層に形成される。さらに、上記半導体集積回路の複数のパッドにおいて、バッド開口部分のパッドメタルの少なくとも下全面に形成された複数の配線メタルは互いに同一の電位に設定される。

(もっと読む)

半導体装置、液晶ディスプレイパネル及び携帯情報端末

【課題】外部駆動端子の狭ピッチ化に充分答えることができる半導体装置を提供する。

【解決手段】長方形の半導体基板の一方の長辺に沿ってそれぞれ配置された、複数の外部駆動端子(3A,3B,3C)、対応する前記外部駆動端子に接続されたESD保護回路(4A,4B,4C)、及び対応する外部駆動端子に接続された出力回路(5)を備え、複数個の外部駆動端子は、Y方向に沿って複数列であるn列で配置され、各列の間で外部駆動端子の位置が相互にずらされた千鳥状配置を有し、前記出力回路は、Y方向に交差するX方向にn個の外部駆動端子毎に対応して一列に配置されるn個の出力ユニット(5A,5B,5C)を有する。n列の千鳥状配置によって外部駆動端子を狭ピッチにできる。n個の外部駆動端子毎に対応される出力回路にはX方向に一列で配置されたn個の出力ユニットを配置することにより、n個分の出力ユニットの幅を1個分の幅に集約できる。

(もっと読む)

半導体装置

【課題】並列駆動構成のI/Oバッファから出力される信号を安定化し、信頼性を向上する。

【解決手段】I/Oセル2は、1つの出力信号を正転信号と反転信号からなる相補信号として出力する相補型I/Oセルからなり、2つのI/Oセル2が並列接続された構成からなる。2つのI/Oセル2の出力部となるインバータ6の出力部は、配線17によってそれぞれ接続されており、2つのI/Oセル2の出力部となるインバータ7の出力部は、配線18によってそれぞれ接続されている。配線17は、I/Oセル2の下辺側に2つのI/Oセル2を横断するように形成され。配線18は、該配線17の上方に形成されており、2つのI/Oセル2を横断するように形成されている。また、配線17の配線長と配線18の配線長は、略同等となるようにレイアウトされている。

(もっと読む)

半導体装置

【課題】ゲート電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにするアンチヒューズをメモリ素子として有する半導体装置を提供する。

【解決手段】基板10は第1導電型、例えばp型の半導体基板(例えばシリコン基板)である。アンチヒューズは、ゲート電極120及び第2導電型拡散層130を有している。第2導電型拡散層130は基板10に形成されており、例えばn型である。第1コンタクト122はゲート電極120に接続している。第2コンタクト142は第1コンタクト122と同一層に形成されており、基板10のうち第2導電型拡散層130が形成されていない領域に接続している。第2コンタクト142は第1コンタクト122に隣接している。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出する精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に形成された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンに接続され、導電パターンの回路定数により決定される発振周波数で発振する発振回路と、発振回路の発振周波数が事前に設定された範囲に含まれるか否かを判定し、発振周波数が事前に設定された範囲に含まれない場合に、導電パターンに改変が加えられたことを検出する検出回路とを有することを特徴とする半導体集積回路装置が提供される。

(もっと読む)

ESD検証装置、ESD検証方法およびESD検証プログラム

【課題】半導体回路内のパッド間の電流の流れやすさを精度よく解析する。

【解決手段】ESD保護素子が接続された2つのパッド間の一方側から他方側に流れる電流の流れ易さを数値化した第1テーブル作成手段と、反対向きの電流の流れ易さを数値化した第2テーブル作成手段と、第1及び第2テーブルを合成して、最も電流が流れ易い経路を数値化した第3テーブル作成手段と、第3テーブルに基づいて、任意のパッド間で、ESD保護素子を経由する全経路について、電流の流れ易さを数値化した第4テーブル作成手段と、全ESD保護素子を削除した状態で、任意のパッド間の電流の流れ易さを数値化した第5テーブル作成手段と、第4及び第5テーブルとに基づいて、任意のパッド間で、ESD保護素子を通過する経路と通過しない経路の電流の流れ易さの比較結果が一致しない場合に、対応するパッド同士の組合せと、パッド間の経路とを提示する手段4と、を備える。

(もっと読む)

41 - 60 / 357

[ Back to top ]