Fターム[5F064DD12]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子、セル、ブロックの方向、角度 (184)

Fターム[5F064DD12]に分類される特許

1 - 20 / 184

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

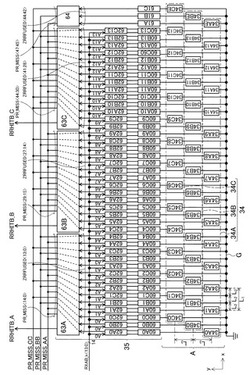

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

レイアウトデータ作成装置及び半導体装置

【課題】従来のようにピラーの分割単位が小数点数とならず、単位ピラートランジスタのピラーの径の変更を行う必要が無くなり、半導体装置を製造するプロセスを複雑化することなく、ピラー型のトランジスタによりセルを、セルロウ内に効率的に配置するレイアウトデータ作成装置を提供する。

【解決手段】本発明のレイアウトデータ作成装置は、集積回路における複数の単位ピラー型トランジスタで構成されるピラー型トランジスタを、配置領域内に配置可能な単位ピラー型トランジスタの整数単位に分割し、配置領域内に配置するサブピラー型トランジスタを生成するトランジスタ調整部2を備えている。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、レイアウトの面積効率の低下を抑制可能となる、マルチハイトセルのレイアウト構造を提供する。

【解決手段】標準論理セル10は、電源配線または接地配線となるメタル配線12を共有するようにY方向に隣接して配置された第1および第2回路領域A1,A2を備えている。X方向において、第1回路領域A1の両端部の位置x1a,x1bと第2回路領域A2の両端部の位置x2a,x2bとは、少なくともいずれか一方が異なっている。すなわち、標準論理セル10の外形形状CFは、第1および第2回路領域A1,A2の外形形状が矩形であるにもかかわらず、非矩形となっている。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体装置

【課題】周辺回路領域を整形された形状とすることによりチップ面積を縮小する。

【解決手段】Y方向に延在する複数のデータバスDBがピッチP1でX方向に配列されたメモリセル領域40と、対応する複数のデータバスDBにそれぞれ接続された複数のバッファ回路BCが設けられたバッファ領域61とを備える。バッファ領域61上においては、Y方向に延在する複数のデータバスDBがピッチP2でX方向に配列され、ピッチP2はピッチP1よりも小さい。本発明によれば、データバスDBの配列ピッチをバッファ領域上において縮小していることから、他の回路ブロックに割当可能な面積を十分に確保することが可能となる。これにより、当該回路ブロックの幅拡大や形状の変形が不要となることから、無駄な空きスペースが生じにくく、チップ面積を縮小することが可能となる。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】再配線層形成工程、メタルポスト形成工程及び樹脂封止工程を経てウェハレベルで樹脂封止される半導体装置について、パッケージング工程で発生する応力を利用してPMOSFETの電流駆動能力を制御する。

【解決手段】メタルポスト21の形成に起因して半導体基板に圧縮応力が生じる範囲内にPMOSFET31が配置されている。PMOSFET31はそのチャネル方向がメタルポスト23の配置範囲の重心O及びPMOSFET31のチャネル領域の配置範囲の重心Gを通る直線と直交する向きに配置されている。重心Gで、メタルポスト21の形成に起因して半導体基板に生じる圧縮応力は、重心Gの位置で、重心Gと中心Oを通る直線に直交する方向に印加される。重心Gでの圧縮応力の方向とPMOSFET31のチャネル方向は一致するので、PMOSFET31の電流駆動能力は、当該圧縮応力が印加されない場合に比べて向上する。

(もっと読む)

半導体装置および半導体集積回路の設計方法

【課題】本発明は、半導体集積回路を備えた半導体装置および半導体集積回路の設計方法に関し、IO領域を有効に利用しつつパッケージの高さ寸法の増大を有効に抑えた接続を可能とする。

【解決手段】半導体基板の表面の第1の辺に沿って、第1のIOセルと、第2のIOセルとを交互に配置したIO領域を有し、第1のIOセルは、第1の辺から所定の距離の位置に配置されたボンディングパッドを有し、第2のIOセルは、第1のIOセルのボンディングパッドより第1の辺から遠い位置にボンディングパッドを有し、かつ、第1のIOセルの少なくとも1つは、第1の辺から所定の距離の位置に配置された第1のボンディングパッドに加えて、第2のIOセルのボンディングパッドより第1の辺から遠い位置に、第2のボンディングパッドを有する第3のIOセルに置きかえられている。

(もっと読む)

半導体装置

【課題】被測定素子の配置密度を高めることが可能な半導体装置を提供する。

【解決手段】異なる層に設けられた列配線M1および行配線M2からなる単位アレイ配線21と、異なる層に設けられた列配線M3および行配線M4からなる単位アレイ配線22とを、互いに異なる層に設ける。複数の単位アレイ配線21,22には、それぞれ、複数の被測定素子11,12のいずれか一つを接続する。複数の単位アレイ配線21,22どうしを部分的に重ね合わせて(オーバーラップさせて)配置することにより、被測定素子11,12の配置密度を高めることが可能となる。

(もっと読む)

半導体集積回路

【課題】内側のセル列と外側のセル列とでセルの形状が同じ場合において、内側のセル列におけるセルの配列ピッチを外側のセル列におけるセルの配列ピッチより大きくしなくても外側のセル列のセルに接続される配線のための領域を確保することができる。

【解決手段】半導体集積回路は、半導体チップの外周11に沿って配置される複数の第1セル40と、複数の第1セル40の内側で外周11に沿って配置される複数の第2セル40とを具備する。複数の第1セル40及び複数の第2セル40は同一の長方形形状に形成される。複数の第1セル40のそれぞれの長辺4aは外周11に平行である。複数の第2セル40のそれぞれの長辺4aは外周11に垂直である。

(もっと読む)

レイアウト設計装置

【課題】アナログレイアウト設計の自動化による設計工期の短縮を図ることが可能なレイアウト設計装置を提供すること。

【解決手段】レイアウト設計装置21は、回路データ24の中から特性を一致させる必要があるトランジスタ、抵抗、容量素子群を抽出し、トランジスタ、抵抗、容量素子群の接続関係に基づいてトランジスタ、抵抗、容量素子群に含まれる複数のトランジスタ、抵抗、容量素子によって構成される所定の機能を有する回路、たとえば差動回路、差動負荷回路およびミラー回路を特定する。そして、特定された回路の種別に応じてレイアウト制約30を生成し、レイアウト制約30に基づいて配置配線を行なう。したがって、アナログ回路のレイアウト制約30を自動的に付加することができ、アナログレイアウト設計の自動化による設計工期の短縮を図ることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率の絶縁膜を有するnチャネル型トランジスタやpチャネル型トランジスタを有する半導体装置の製造方法において、nチャネル型トランジスタのゲート絶縁膜の側面への異物の付着を抑制する。

【解決手段】半導体基板の主表面上の、p型不純物領域PWLに機能用nチャネル型トランジスタが、n型不純物領域NWLに機能用pチャネル型トランジスタが形成される。p型不純物領域PWLの、平面視における機能用nチャネル型トランジスタ以外の領域に形成される複数の第1の周辺用トランジスタは、周辺用n型ゲート構造体と周辺用p型ゲート構造体とが混在するように形成される。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体装置

【課題】2つの入力端子の配置形態を工夫することにより配線層の増設スペースを確保しスタンダードセルの原価低減を図る。

【解決手段】入力端子34bはゲート配線2bに接続され、入力端子34cはゲート配線2cに接続される。また、入力端子34b、34cは、Y方向に互いに近接して配置され、入力端子34bの第2コンタクト配線4bは、第1コンタクト配線3bと隣接し、且つ該第1コンタクト配線3bに対しX方向に延在する。入力端子34cの第2コンタクト配線4cは、第1コンタクト配線3cと隣接し、且つ該第1コンタクト配線3c対して第2コンタクト配線4bとは逆のX方向に延在する。即ち、入力端子34bの第1コンタクト配線3bと入力端子34cの第2コンタクト配線4cとはY方向に互いに対向して配置され、入力端子34bの第2コンタクト配線4bと入力端子34cの第1コンタクト配線3cはY方向に互いに対向して配置される。

(もっと読む)

半導体チップ、半導体装置及びLSI設計装置

【課題】チップコストの低下とチップ歩留りの向上とを同時に実現する。

【解決手段】実施形態に係わる半導体チップは、パッド領域11及び方形でないゲート領域12を備える第1のレイアウトL1と、第1のレイアウトL1を180°回転させた第2のレイアウトL2とを備える。第1及び第2のレイアウトL1,L2は、点対称かつ重なり合わずに結合されることによりチップレイアウトを構成する。チップレイアウトは、方形のチップ領域内に配置され、第1及び第2のレイアウトL1,L2は、それぞれ独立に動作するLSIを構成する。

(もっと読む)

半導体装置、液晶ディスプレイパネル及び携帯情報端末

【課題】外部駆動端子の狭ピッチ化に充分答えることができる半導体装置を提供する。

【解決手段】長方形の半導体基板の一方の長辺に沿ってそれぞれ配置された、複数の外部駆動端子(3A,3B,3C)、対応する前記外部駆動端子に接続されたESD保護回路(4A,4B,4C)、及び対応する外部駆動端子に接続された出力回路(5)を備え、複数個の外部駆動端子は、Y方向に沿って複数列であるn列で配置され、各列の間で外部駆動端子の位置が相互にずらされた千鳥状配置を有し、前記出力回路は、Y方向に交差するX方向にn個の外部駆動端子毎に対応して一列に配置されるn個の出力ユニット(5A,5B,5C)を有する。n列の千鳥状配置によって外部駆動端子を狭ピッチにできる。n個の外部駆動端子毎に対応される出力回路にはX方向に一列で配置されたn個の出力ユニットを配置することにより、n個分の出力ユニットの幅を1個分の幅に集約できる。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

1 - 20 / 184

[ Back to top ]