Fターム[5F064EE16]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 配線の方向、角度 (398)

Fターム[5F064EE16]に分類される特許

1 - 20 / 398

スタンダードセル、および、半導体集積回路

半導体装置

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

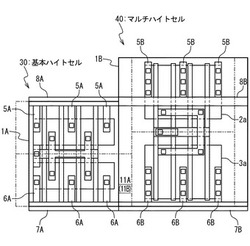

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

半導体装置の設計方法及び半導体装置の製造方法

【課題】半導体装置の歩留まりが低下することを抑制する。

【解決手段】配線パターンを示す配線パターンデータを取得する(ステップS10)。次いで、配線パターンデータを解析して、第1方向パターン及び第2方向パターンを特定する(ステップS20)。第1方向パターンは、第1の方向に延伸するパターンであり、第2方向パターンは、第1の方向に直交する方向に延伸するパターンである。次いで、第1方向パターと第2方向パターンの交点を検出する。そして、この交点から延伸するパターンのうち、ビア、コンタクト及び他のパターンのいずれにも接続していないパターンを不要パターンとして検出し、検出した不要パターンを除去する(ステップS30)。そしてその後、設計した配線パターンに対して光近接効果補正を行う(ステップS40)。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

局所優先方向アーキテクチャ、ツール、及び機器

【課題】「局所優先方向」配線モデルを使用してネットをルーティングするための機器を提供する。

【解決手段】本発明の一部の実施形態は、1つ又はそれよりも多くのEDAツール(プレーシング、ルーティングなどのような)と共に使用される「局所優先方向(LPD)」配線モデルを提供する。LPD配線モデルは、少なくとも1つの配線層が、各々が特定の配線層とは異なる優先方向を有する一組の領域を有することを可能にするものである。更に、各領域は、その組における少なくとも1つの他の領域の局所優先方向とは異なる局所優先方向を有する。更に、少なくとも2つの領域は、2つの異なる多角形形状を有し、その組における領域は、その組における別の領域を取り囲むことはない。

(もっと読む)

配線支援方法及び装置

【課題】配線すべき複数の信号線を、ユーザの指定する目的に従って適切にグループ化する。

【解決手段】配線すべき複数の信号線を複数のグループに分けるための方法は、ユーザから、複数の信号線のグループ化の条件の指定を受け付けるステップと、指定された、グループ化の条件と、データ格納部に格納されている、複数の信号線の始点端子群と終点端子群との配置パターンとに基づいて、複数の信号線のグループ化の処理を切り替えて実施する実施ステップとを含む。

(もっと読む)

半導体装置

【課題】配線間の影響を抑制することができる多層配線を有する半導体装置を実現する。

【解決手段】本発明の実施形態における半導体装置は、下層の配線層に第1の方向に沿って形成された信号配線11と、下層の配線層と絶縁膜を介して配置される上層の配線層に第1の方向と交差する第2の方向に沿って形成された基準電位配線13と、 上層の配線層に基準電位配線13に沿って近接して形成されたシールド線14a、14bと、を有し、信号配線11と基準電位配線13の交差部15cにおいて基準電位配線13とシールド線14a、14bとの距離が他の部分に比べてより狭くなっていることを特徴とする。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

撚り合わされた導線を有する集積回路インダクター

【課題】集積回路インダクターを提供すること。

【解決手段】第1の端子と、第2の端子と、第1の端子と第2の端子との間に連結された伝導性経路とを備え、伝導性経路は、集積回路上に複数の撚り合わされた伝導性線を含む、インダクター。撚り合わされた伝導性線は、集積回路上に少なくとも1つの金属層から形成された少なくとも第1の伝導性線と、集積回路上に少なくとも1つの金属層から形成された少なくとも第2の伝導性線とを含む、インダクター。

(もっと読む)

メモリセル

【課題】拡散層等のバルクが固定であってメタル層、コンタクト層の少なくとも何れか1層を変更して複数の仕様に対応可能なメモリセルを提供すること。

【解決手段】メモリユニットが列方向に沿って鏡面対称に行方向に沿って並置されて、2行2列に配置されメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第4拡散層を備え一対の記憶ノードが構成される。第1および第2ワード線は第1〜第4拡散層の両端部外方に配置される。第1及び第2ワード線の間に行方向に沿って第1のメタル配線領域が確保され、第1メタル層が配線可能とされる。列方向に隣接配置されるメモリユニットの境界領域でありは第3、第4拡散層が配置される列方向の位置には列方向に沿って第2のメタル配線領域が確保され、第2メタル層が配線可能とされる。

(もっと読む)

半導体集積回路

【課題】電荷転送効率が高い転送トランジスタを備える半導体集積回路を提供することを目的とする。

【解決手段】実施形態に係る半導体集積回路は、ゲート電極を有し、当該ゲート電極及び一の拡散層が第1配線でダイオード接続された転送トランジスタと、クロック信号が供給されるクロック信号線とを備え、前記クロック信号線の一部である第1部分クロック信号線の少なくとも一部が前記ゲート電極上に形成されていることを特徴とする。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体装置設計装置、及びプログラム

【課題】より多くのI/Oセルを配置することができるようにする。

【解決手段】多層配線層には、電位供給用接続配線230が設けられている。電位供給用接続配線230は、平面視で外周セル列20を構成するI/Oセル200のいずれか、および内周セル列30を構成するI/Oセル200のいずれかと重なっている。そして電位供給用接続配線230は、外周セル列20の下方に位置する電源電位供給配線222を、内周セル列30の下方に位置する電源電位供給配線222に接続するとともに、外周セル列20の下方に位置する接地電位供給配線224を、内周セル列30の下方に位置する接地電位供給配線224に接続している。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、レイアウトの面積効率の低下を抑制可能となる、マルチハイトセルのレイアウト構造を提供する。

【解決手段】標準論理セル10は、電源配線または接地配線となるメタル配線12を共有するようにY方向に隣接して配置された第1および第2回路領域A1,A2を備えている。X方向において、第1回路領域A1の両端部の位置x1a,x1bと第2回路領域A2の両端部の位置x2a,x2bとは、少なくともいずれか一方が異なっている。すなわち、標準論理セル10の外形形状CFは、第1および第2回路領域A1,A2の外形形状が矩形であるにもかかわらず、非矩形となっている。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

1 - 20 / 398

[ Back to top ]