Fターム[5F064EE35]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線材料 (810) | 金属 (713) | シリサイド (43)

Fターム[5F064EE35]に分類される特許

1 - 20 / 43

半導体装置

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

半導体装置の配線抵抗算出装置

【課題】配線に多数のスルーホールが存在する場合にも、多数のスルーホール分割要素に分割されることを回避し、分割要素の数の増大を抑制し、配線抵抗の算出時間を短縮する装置の提供。

【解決手段】第1配線層と第2配線層の配線を接続する複数のスルーホールを有する領域に、複数のスルーホールを含む枠図形FF1を設定し、枠図形を複数の枠領域FR1〜3に分割する。各枠領域内の複数のスルーホールを合成して1つのスルーホールにまとめ、各枠領域内にはそれぞれ1つの合成スルーホールCT1〜3が設定される。各枠領域に1つに設定されたスルーホールの位置を基準として、第1配線層、第2配線層における枠図形に対応する配線抵抗を分割した抵抗値RL11〜14、RL21〜22と、各枠領域内で1つに設定されたスルーホールの抵抗値RCT1〜3とを用いて、抵抗回路網を作成し、抵抗回路網を1つの抵抗RSに合成する。

(もっと読む)

半導体装置

【課題】 配線に対するエレクトロマイグレーションの影響を排除する点で、従来の構造は十分とはいえない。

【解決手段】 半導体基板の上に第1の配線が配置されている。半導体基板の上であって、第1の配線とは異なる高さに第2の配線が配置されている。第1のビアが、第1の配線と第2の配線とを高さ方向に接続する。第2のビアが、高さ方向に関して第1のビアとは反対側において第1の配線に接続される。第1の配線は、第1のビアとの接続点から基板面内の第1の方向に延在し、第2のビアは、第1のビアよりも第1の方向にずれた位置に配置されており、第2のビアは、高さ方向に電流を流す電流路として作用しない。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性を損なうことなく更なる集積化を実現し得る半導体装置を提供する。

【解決手段】第1のトランジスタL1のゲート電極を含み、第1のコンタクト層48aを介して第2のトランジスタL2のソース/ドレイン拡散層20に電気的に接続される、直線状の第1のゲート配線16aと、第2のトランジスタL2のゲート電極を含み、第2のコンタクト層48bを介して第1のトランジスタのソース/ドレイン拡散層22に電気的に接続される、第1のゲート配線と平行な直線状の第2のゲート配線16bと、第1のゲート配線及び第2のゲート配線を覆うように形成された絶縁膜であって、第1のゲート配線と第2のトランジスタのソース/ドレイン拡散層とを露出し、長辺方向が第1のゲート配線の長手方向である第1の開口部46aが形成された絶縁膜と、第1の開口部内に埋め込まれた第1のコンタクト層とを有している。

(もっと読む)

アンチヒューズ構造およびアンチヒューズ構造の製造方法

【課題】低い印加電圧(3V以下)で導通状態を変更可能なアンチヒューズ素子(アンチヒューズ構造)を提供する。

【解決手段】本発明のアンチヒューズ構造100は、第一配線3と、前記第一配線3上に順次積層された、不純物を含有した第一の多結晶シリコン膜6、第一のタングステンシリサイド膜7、第一の窒化タングステン膜8からなる第一のアンチヒューズ部20aと、前記第一のアンチヒューズ部20a上に接続された第二配線10と、を具備してなることを特徴とする。

(もっと読む)

半導体装置及びその設計方法

【課題】シリサイド配線の寄生抵抗による影響を許容できる範囲に抑制しながら、チップ面積の低減を実現する。

【解決手段】半導体装置は、半導体基板10上に、セル高さAHのセルA及びセル高さBHのセルBを備えている。セルAは、P型ソース領域13PS及びP型ドレイン領域13PDと、ゲート電極16Aとを含むP型MISトランジスタと、N型基板コンタクト領域13NSCとを有している。セルBは、P型ソース領域13PS及びP型ドレイン領域13PDと、ゲート電極16Bとを含むP型MISトランジスタと、P型電源供給領域13PSPと、該P型電源供給領域13PSPと接続するように、P型ソース領域13PSが引き出されてシリサイド化されたP型引き出し領域13PSTとを有している。セル高さAHは、セル高さBHよりも大きい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性および集積性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板1)と、シリコン基板1に設けられた第1のトレンチ3と、第1のトレンチ3に埋め込まれた受動素子層10と、第1のトレンチ3と受動素子層10との間に設けられた第1の絶縁膜(シリコン窒化膜4)と、を備え、上面視において、第1のトレンチ3形成の周縁部分と第1の絶縁膜(シリコン窒化膜4)の周縁部分とが略一致している。

(もっと読む)

半導体装置およびその製造方法

【課題】配線として用いられる金属シリサイド層の断線の発生を抑えつつ、微細化を可能にする半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板のタップ領域40、トランジスタ領域36、及びシリサイド配線領域38に形成された活性領域と、シリサイド配線領域38上からトランジスタ領域36上に亘って形成されたゲート電極21と、活性領域上に設けられた金属シリサイド層44aとを備えている。シリサイド配線領域38の少なくとも一部上におけるゲート電極21と金属シリサイド層44aとの距離は、トランジスタ領域36上におけるゲート電極と金属シリサイド層44aとの距離よりも小さい。

(もっと読む)

非等長コンタクトを用いた電気的にプログラム可能なヒューズ及びその製造方法

【課題】改良された熱特性を有する非等長コンタクトを含む電気的にプログラム可能なヒューズ、及びその製造方法を提供する。

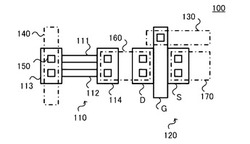

【解決手段】その上に形成されたシリサイド層を有するポリシリコン層から形成されたアノード・コンタクト領域110及びカソード・コンタクト領域118と、カソード・コンタクト領域とアノード・コンタクト領域とを導電接続する、プログラミング電流を印加することによってプログラム可能なヒューズリンク116と、カソード・コンタクト領域のシリサイド層上又はカソード・コンタクト領域とアノード・コンタクト領域の両方のシリサイド層上にそれぞれ所定の構成で形成された複数の非等長コンタクト120とを含む、電気的にプログラム可能なヒューズである。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

半導体装置

【課題】ポリシリコン配線構造を利用する場合にプログラム後の抵抗値のばらつきがなく高抵抗値化が図れ、良好なプログラム特性や高信頼性を有する半導体装置を提供する。

【解決手段】第1の端子部12aと、第2の端子部12cと、前記第1および第2の端子部の相互間を接続するヒューズリンク12bとを有する半導体装置であって、前記第1の端子部および前記ヒューズリンクは、不純物イオンがドープされたポリシリコン層とその上に積層された金属元素を含む層とを有し、前記第2の端子部は、前記ヒューズリンクとの接続端側に不純物イオンがドープされていないポリシリコン層とその上に積層された金属元素を含む層とを有する。

(もっと読む)

半導体集積回路装置

【課題】スタンダードセルを小型化することのできる技術を提供する。

【解決手段】電源電位Vddを供給し、第1方向に沿って形成された第1タップと、電源電位Vssを供給し、第1方向と交差する第2方向に第1タップと対向して配置され、第1方向に沿って形成された第2タップと、第1タップと第2タップとの間に形成されたスタンダードセル3において、第2方向における第1タップの中心と第2方向における第2タップの中心との間のセルの高さ(距離L)を[(整数+0.5)×第2層目の配線の配線ピッチ]または[(整数+0.25)×第2層目の配線の配線ピッチ]とする。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】半導体集積回路装置の集積度の向上を図ることのできる技術を提供する。

【解決手段】セルの高さ方向に隣接して配置されるセルrow上段の2入力NAND回路6とセルrow下段のインバータ回路1との間の結線に、2層目以上の配線を用いずに、1層目の配線M1よりも下層に位置し、2入力NAND回路6またはインバータ回路1を構成するMISFETのゲート電極7N2,7P2と一体化した導電体膜からなる配線8を用いる。

(もっと読む)

交差部のアレイを有する集積キャパシタ

集積回路(「IC」)のキャパシタ(100)は、ICの層に形成され、キャパシタの第1のノードに電気的に接続され、かつ第1のノードの一部分を形成する第1の複数の導電性交差部(102,104)と、ICの金属層に形成された第2の複数の導電性交差部(108,110)とを有する。第2の複数の導電性交差部の導電性交差部は、キャパシタの第2のノードに電気的に接続され、かつ第2のノードの一部分を形成し、第1のノードに容量結合する。  (もっと読む)

(もっと読む)

半導体装置

【課題】サイズおよびコストを抑えることができる半導体装置を提供する。

【解決手段】pMIS領域は、方向Xに沿って複数のスタンダードセルCffの各々を通る境界BRと、第1の外縁OTpとの間に形成されている。nMIS領域は、境界BRと第2の外縁OTnとの間に形成されている。電源配線VDおよび接地配線VSのそれぞれは、第1および第2の外縁OTp、OTnに沿って延びている。複数のpMIS配線M1pおよび複数のnMIS配線M1nのそれぞれは、方向Xに沿って延びかつ方向Yに沿ってピッチPminで配置された複数の第1の仮想ラインVLpおよび複数の第2の仮想ラインVLnの上に配置されている。複数の第1の仮想ラインVLpのうち境界BRに最も近いものと、複数の第2の仮想ラインVLnのうち境界BRに最も近いものとの間隔は、ピッチPminよりも大きい。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】小型化の進んだ回路セルでも回路信頼性の低下を防止できる回路レイアウトの設計方法を提供する。

【解決手段】ゲート電極1に電位差の大きい電源電位あるいは基準電位からのノイズの影響が及んで誤動作を起こしてしまうことを防ぐために、ゲート電極1に接続するプラグ5と電源電位あるいは基準電位が供給されるプラグ6との間は、プラグ5に電源電位あるいは基準電位からのノイズの影響が及ばない十分な距離だけ離間させるために、配線4下にて等間隔で配置されているプラグ6のうち、プラグ5(5A)と十分離間していない配置位置6Aに配置されるプラグ6のみを平面レイアウトの設計時に消去する。

(もっと読む)

1 - 20 / 43

[ Back to top ]