Fターム[5F064FF05]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択目的 (1,053) | 特性、機能の切り換え (623) | 抵抗値の切り換え (109)

Fターム[5F064FF05]に分類される特許

1 - 20 / 109

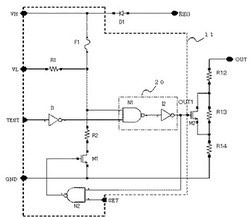

トリミング回路及び調整回路

【課題】ヒューズ素子の仮想切断を可能にすると共に、高電圧又は大電流によるヒューズ溶断の際に、周辺回路を破損する確率も低減できる信頼性の高いトリミング回路を提供する。

【解決手段】ヒューズトリミングを行うための回路であって、トリミングヒューズと、

前記トリミングヒューズに接続されるトリミング用のパッド端子と、仮想切断時に制御信号を入力するテスト端子と、入力端子の一方が前記テスト端子に接続され他方が前記トリミングヒューズに接続され、入力された制御信号に応じた制御信号を出力する制御回路と、を有し、前記トリミングヒューズの切断により、前記制御回路の他方の入力端子がGNDレベルへプルダウンする手段を備えたことを特徴とする。

(もっと読む)

半導体集積回路およびそれを用いた光センサ機器

【課題】修正前の特性値がその特性値の出現頻度分布における平均値±2×(標準偏差)の範囲に入る製造品に対するヒューズ溶断本数を少なくする。

【解決手段】素子アレイ14には抵抗アレイを設け、特性値の分布の平均値を素子アレイ14で得られる合成抵抗値の中央値に対応付け、トリミング情報生成回路12における上記中央値より大きい合成抵抗値に対応するトリミング情報の配列を、10進数で「15」〜「8」の降順に、上記中央値以下の合成抵抗値に対応するトリミング情報の配列を、10進数で「0」〜「7」の昇順に設定する。変換回路13は、トリミング情報生成回路12からのトリミング情報を変換して、素子アレイ14の抵抗アレイから各合成抵抗値を得るためにオフする抵抗を選択する素子選択情報を生成する。こうして、上記分布における「平均値±2σ」の範囲内に対応付けられトリミング情報を生成する場合のヒューズ溶断数を大幅に削減する。

(もっと読む)

半導体装置

【課題】多層配線プロセスでSOGエッチバックにて平坦化を行なうプロセスにて、ヒューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置の製造方法を提供する。

【解決手段】ヒューズ開口部からの水分侵入を防ぐためのメタル1層目のガードリングの下部まで多結晶シリコンが伸びているヒューズ形状にする。これによりヒューズの電極をとるためのメタル配線とガードリングのメタル配線の高さがそろい、SOG層がIC内部に到達することを防ぐことが可能となる。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

半導体装置

【課題】回路規模が増大化する。

【解決手段】抵抗値が順に小さい値となって直列接続される複数のヒューズを備えるヒューズ部と、前記ヒューズ部の複数のヒューズのそれぞれ一端と、第1の電源電圧との間に接続される複数の選択スイッチと、前記第1の電源電圧から所定の電位差を有するヒューズ溶断用電圧を、前記ヒューズ部の最も小さい抵抗値のヒューズ側に出力するヒューズ溶融電圧出力回路と、ヒューズ溶断時に、前記ヒューズ溶融電圧出力回路が前記ヒューズ溶断用電圧を出力し、前記ヒューズ部の最も大きい抵抗値のヒューズに接続される選択スイッチから最も小さい抵抗値のヒューズに接続される選択スイッチまでを順に導通させる制御回路と、を備える半導体装置。

(もっと読む)

トリミング回路及び半導体装置

【課題】ヒューズを切断するための電流を入力する専用の端子を必要としないトリミング回路及び半導体装置を提供する。

【解決手段】内部回路の外部端子であるパッドに接続された入力端子と、電源端子と出力端子との間に設けられたヒューズと、入力端子と出力端子との間に設けられたダイオードと、を備え、パッドにダイオードが順方向バイアスになるように電圧を印加して、トリミング回路のトリミングを行うように構成した。

(もっと読む)

抵抗変化素子の制御方法、および、半導体装置

【課題】抵抗変化素子の閾値電圧のばらつきを生じさせることなく、閾値電圧を低電圧化すること。

【解決手段】印加されたパルス電圧の極性に応じて抵抗値の異なる第1の状態と第2の状態との間で遷移する抵抗変化層と、抵抗変化層の一端に接続された第1の電極と、他端に接続された第2の電極とを備えた抵抗変化素子の制御方法であって、抵抗変化層を第1の状態から前記第2の状態へ遷移させる第1の極性とは逆の第2の極性を有する第1のパルス電圧を、抵抗変化層を第1の状態に保ちつつ、両電極間に印加した後、第1の極性を有する第2のパルス電圧を両電極間に印加して、抵抗変化層を第1の状態から第2の状態へ遷移させる。

(もっと読む)

半導体デバイスの電気的にプログラミング可能なヒューズモジュール

【課題】より小型なeヒューズモジュールを提供する。

【解決手段】半導体デバイスが、eヒューズモジュールおよびプログラミング電流生成器を有する。eヒューズモジュールが電気的にプログラミングするeヒューズ素子(226)のアレイを含む。プログラミング電流発生器が、複数の基準トランジスタ素子(M0〜M6)のセットと、基準トランジスタ素子(M0〜M6)を活性化させて、選択された基準電流を生成するセレクタ(254)と、アレイの選択されたeヒューズ素子(226)に、選択された基準電流に応じたプログラミング電流を印加して、eヒューズ素子(226)の抵抗をプログラミングするカレントミラー(M7、M8、M9)とを有する。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒューズ配線を溶断する際に素子分離構造や半導体基板に与えるダメージを抑制することができる半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板10と、半導体基板の主面の面内方向に互いに離間するように形成された一対の電極12A,12Bと、これら電極12A,12Bを被覆し、上面に凹部13cを有する下層絶縁膜13と、凹部13cに形成されたヒューズ配線20Cと、下層絶縁膜13及びヒューズ配線20Cを被覆する層間絶縁膜21と、層間絶縁膜21上に形成され、ヒューズ配線20Cの直上にレーザトリミング用の開口部1hを有する上層絶縁膜31とを備える。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体集積回路

【課題】 メモリの動作特性の向上を図る。

【解決手段】本実施形態の半導体集積回路は、第1の端子aが第1の電源スイッチを介して第1の電源に接続され、第2の端子bがノードN1に接続される第1の抵抗変化型メモリ素子R1と、第3の端子aがノードN1に接続され、第4の端子bが第2の電源スイッチを介して第2の電源に接続される第2の抵抗変化型メモリ素子R2と、電流経路の一端が第1のプログラム電源PV1に接続され、電流経路の他端がノードN1に接続される第1のスイッチM2と、電流経路の一端がノードN1に接続され、電流経路の他端が第1のプログラム電源PV1と異なる電圧値を出力する第2のプログラム電源PV2に接続される第2のスイッチM3と、を含んでいる。

(もっと読む)

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

半導体装置

【課題】トリミングデータによって調整可能な基準電圧発生回路を備えた半導体装置において、電源が立上がるまでの基準電圧のばらつきの影響を受けないようにする。

【解決手段】半導体装置10において、基準電圧生成部1は、外部電源電圧VCCに基づいて、トリミングデータTRM1に応じて調整された第1の基準電圧V1*およびこのトリミングデータTRM1に依存しない第2の基準電圧V2を生成する。不揮発性メモリ3は、第1の基準電圧V1*に基づく電圧によって動作し、上記のトリミングデータTRM1を記憶する。パワーオンリセット回路5は、電源立上げ時に外部電源電圧VCCが第2の基準電圧V2の定数倍に達したときにリセット信号の論理レベルを切替える。制御回路6は、リセット信号の論理レベルの切替に応答して、不揮発性メモリ3に記憶された上記のトリミングデータTRM1を基準電圧生成部1に読込ませる。

(もっと読む)

1 - 20 / 109

[ Back to top ]