Fターム[5F064GG01]の内容

ICの設計・製造(配線設計等) (42,086) | 製造プロセス技術 (798) | 拡散、イオン注入 (156)

Fターム[5F064GG01]に分類される特許

81 - 100 / 156

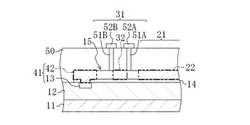

半導体装置及びその製造方法

【課題】FEOLレベルから正負とも低電圧の範囲で拡散工程中のチャージアップから被保護素子を保護し、且つ、拡散工程完了後は被保護素子の駆動に必要な正負両極性の高電圧を被保護素子に印加することが可能な半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11に形成され、被保護素子電極22を有する被保護素子21と、半導体基板11と電気的に接続された基板接続電極42を有する基板接続部41と、被保護素子電極22と基板接続電極42との間に形成されたヒューズ素子電極32を有するヒューズ素子部31とを備えている。ヒューズ素子電極32は、所定の電流を流すことにより切断可能に形成され、ヒューズ素子電極32が切断されていない状態において、被保護素子電極22、基板接続電極42及びヒューズ素子電極32は、一体に形成された導電膜15からなる。

(もっと読む)

半導体集積回路装置

【課題】ウェル近接効果に起因するトランジスタ特性のばらつきを抑えることが可能な半導体集積回路装置を提供する。

【解決手段】スタンダードセル10が横方向に配置されたスタンダードセル列11,12,13,…が、縦方向に並べて配置されている。各スタンダードセル列11,12,13,…は1列おきにフリップされており、スタンダードセル列11,12がNウェルを共有し、スタンダードセル列12,13がPウェルを共有している。スタンダードセル列11,12,13の端に位置するNMOSトランジスタ21,22,23からPウェルの端までの距離D1,D2,D3が、スタンダードセル列12,13に共有されたPウェルの幅W1以上になるように、拡げられている。

(もっと読む)

薄膜抵抗体、半導体装置及び薄膜抵抗体の製造方法

【課題】新たなマスク及びプロセス工程を追加することなく、製造バラツキに影響がなく、薄膜抵抗体の特性に影響を与えることなく、安定したレーザトリミングを可能にすること。

【解決手段】シリコン基板1上に形成された、レーザトリミングがなされる薄膜抵抗体は、厚さ3〜50nmの膜厚で形成された第1の薄膜抵抗体10と、第1の薄膜抵抗体10の上層に10〜30nmの厚さで形成されたシリコン酸化膜9と、シリコン酸化膜9の上層に厚さ50nm以上の膜厚で形成された第2の薄膜抵抗体10とを積層構造に有する。

(もっと読む)

アンチヒューズ素子及びこれを有する半導体装置

【課題】アンチヒューズ素子を絶縁破壊した後の抵抗値のばらつきを抑制する。

【解決手段】ゲート電極110と、デプレッション型のチャネル領域120と、ゲート電極110とチャネル領域120との間に設けられたゲート絶縁膜130と、チャネル領域120と接合する拡散層領域122とを備える。チャネル領域120から見て拡散層領域122とは反対側の領域には、拡散層領域122と同電位が与えられる他の電極を介することなく素子分離領域104が存在する。これにより、ゲート絶縁膜130にかかる電界が不均一となり、拡散層領域122に近くなるほど電界強度が高くなることから、拡散層領域122に近い部分ほど絶縁破壊が生じる確率が高くなる。

(もっと読む)

スイッチ素子を搭載した半導体装置及びその製造方法

【課題】スイッチ素子の小型化及び高密度配置によるスイッチ素子の高集積化が可能であり、更に、スイッチ素子を高信頼化することができるスイッチ素子を搭載した半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に多層配線が形成されており、この多層配線内に抵抗変化材料層205が形成されている。この抵抗変化材料層205は下層配線204と上層配線206とに接続されており、抵抗変化材料層205の周囲は、金属からなる防爆壁211により取り囲まれている。この防爆壁は、抵抗変化材料層の溶断時に飛散物質が隣接する抵抗片素子に付着することを防止すると共に、抵抗変化材料層を加熱するヒーターとしても機能する。

(もっと読む)

アンチヒューズ素子及びこれを有する半導体装置

【課題】アンチヒューズ素子を絶縁破壊した後の抵抗値のばらつきを抑制する。

【解決手段】ゲート電極110と、デプレッション型のチャネル領域120と、ゲート電極110とチャネル領域120との間に設けられたゲート絶縁膜130と、チャネル領域120と接合する拡散層領域122とを備える。ゲート電極110の端部111は、チャネル領域120と拡散層領域122の境界と平面視において実質的に一致しており、且つ、ゲート電極110の端部111がジグザグ形状を有していることを特徴とする。これにより、ゲート電極110の端部111を直線形状とした場合と比べて端部111の長さが長くなることから、ゲート絶縁膜130の端部が絶縁破壊される確率が高まる。

(もっと読む)

電圧レギュレーター及びその製造方法

【課題】電圧レギュレーターのチップサイズを減らすとともに、生産工程の短縮で製造原価を節減する電圧レギュレーター及びその製造方法を提供する。

【解決手段】本発明は、入力端子、出力端子、及び接地端子が備えられた電圧レギュレーターであって、前記入力端子を介して基準電圧を生成する基準電圧発生部と、複数の一定パターンに配列された金属配線、及び前記金属配線を選択的に相互に接続して活性化する導電性金属配線パターンで構成される活性抵抗、及びフィードバック抵抗によって出力端子の電圧を分配する電圧分配部と、前記基準電圧発生部の基準電圧、及び前記フィードバックされる電圧分配部の分配電圧を入力して差動増幅する増幅部と、前記入力端子を介して入力された電源を前記増幅部の出力電圧によって前記出力端子に伝達するトランジスタとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】電圧設定精度が高く、電圧調整自由度が大きい電圧設定回路や電圧検出回路を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、不純物拡散層である不純物拡散領域2が形成された半導体基板3と、半導体基板3上に形成された層間絶縁膜4と、層間絶縁膜4に形成されたコンタクトホール5に導電材料が充填されて形成されたコンタクトプラグ6と、層間絶縁膜4及びコンタクトプラグ6の上にポリシリコン膜を用いて形成された抵抗部7とを有している。

(もっと読む)

半導体装置及びその製造方法並びに半導体製造装置

【課題】プログラムされた情報のセキリュティが高く、半導体チップ毎に異なる情報をプログラムすることを簡単に可能とすること。

【解決手段】本発明は、半導体ウエハ内に配列された複数の半導体チップとなるべき領域12内にそれぞれ設けられたOTP−ROMセル配列21に対応するプログラムドット配列を有するプログラムヘッド80を、複数の半導体チップとなるべき領域12のうち1つの領域内のOTP−ROMセル配列21に合わせる工程と、プログラムヘッド80を用いOTP−ROMセル配列21を、複数の半導体チップとなるべき領域12ごとに異なるパターンでプログラムする工程と、を有することを特徴とする半導体装置の製造方法である。

(もっと読む)

MOSFET集積回路におけるプロセスによって誘起される性能変動の補償方法

MOSFET集積回路における、プロセスによって誘起される閾値電圧及び駆動電流の変動を自動的に補償する方法。前記方法の第1ステップは、アレイから解析対象のトランジスタを選択することである。前記方法は、アレイの複数のトランジスタに対して所望のループ処理を行う。次に、選択されたトランジスタの設計を解析する。この解析においては、近隣のレイアウトによって誘起される閾値電圧の変動を決定する工程と、近隣のレイアウトによって誘起される駆動電流の変動を決定する工程とが含まれる。前記方法は、次に、トランジスタのゲート長を変更することにより、何れかの決定された変動に対して補償を行う。前記方法には、更に、コンタクトの間隔を変更することにより補償が不十分な点を特定する工程を含めることができる。  (もっと読む)

(もっと読む)

MOSFETアレイにおけるレイアウト依存の閾値電圧変動の迅速な推定方法

集積回路レイアウトにおいて、レイアウトによって誘起される閾値電圧の変動を自動的に推定する方法。前記方法は、解析のために前記レイアウト内の拡散領域を選択する工程で始まる。続いて、システムが、選択された領域のSi/STIエッジと、チャネル領域と、前記チャネル領域に結合するゲート/Siエッジを特定する。次に、特定されたチャネル領域夫々における閾値電圧の変動を特定する。この工程には、縦方向の効果による閾値電圧変動を計算する工程と、横方向の効果による閾値電圧変動を計算する工程と、縦方向と横方向の変動を組み合わせて全体の変動を計算する工程が必要である。最後に、個々のチャネルにおける変動を組み合わせることにより変動の合計が決定される。  (もっと読む)

(もっと読む)

ゲート電極下に金属シリサイドのパイプを有する電気ヒューズ

【課題】 信頼性が向上しているとともに比較的低い電圧でプログラムされることが可能な電気ヒューズを提供する。

【解決手段】 電気ヒューズは、半導体基板と、導電性または一部導電性のポリシリコンを具備するゲートと、を具備する。半導体基板はゲートの近くにおいてアモルファス化されたパイプ領域を具備するとともにパイプ領域に隣接する第1、第2電極領域を具備する。電気ヒューズは、第1、第2電極領域内の半導体基板上の金属シリサイド層をさらに具備する。金属シリサイドは、ニッケル・シリサイド、コバルト・シリサイド、チタン・シリサイド、パラジウム・シリサイド、プラチナ・シリサイド、エルビウム・シリサイド、およびこれらの組合せからなる群から選択される。

(もっと読む)

半導体装置

【課題】絶縁状態をモニターできるトリミングヒューズを有する半導体装置を提供する。

【解決手段】第1の半導体領域11と、第1の半導体領域11内に形成され、第1の半導体領域11と逆導電型で、且つ第1の半導体領域11より不純物濃度が高い第2の半導体領域12と、第2の半導体領域12を含む第1の半導体領域11上に形成された絶縁膜13と、第2の半導体領域12上に絶縁膜13を介して形成された導電膜14と、第2の半導体領域12を外部回路に電気的に接続するためのコンタクト手段としてビア20、配線21、バッド22と、を具備する。

(もっと読む)

電子装置の製造方法、メモリ回路の動作方法、および電子装置

半導体基板(10)上に形成された誘電体層(12)を備える、電子装置。誘電体層(12)上には、代表長さを有するポリシリコンヒューズ構造(14)が形成される。ポリシリコンのヒューズ構造の第1部分(141)と第2部分(143)は、シリサイド化さる。ポリシリコンヒューズ構造(114)のうち、第1部分(141)と第2部分(143)の両方に隣接する第3部分(142)は、シリサイド化されない。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】デュアルダマシン(Dual-Damascene)法を用いた多層Cu配線の形成工程を簡略化する。

【解決手段】層間絶縁膜45上に形成したフォトレジスト膜51をマスクにして層間絶縁膜45をドライエッチングし、層間絶縁膜45の中途部に形成したストッパ膜46の表面でエッチングを停止することによって配線溝52、53を形成する。ここで、ストッパ膜46を光反射率の低いSiCN膜によって構成し、フォトレジスト膜51を露光する際の反射防止膜として機能させることにより、フォトレジスト膜51の下層に反射防止膜を形成する工程が不要となる。

(もっと読む)

半導体集積回路装置

【課題】ウェル近接効果に起因するトランジスタ特性のばらつきを抑えることが可能な半導体集積回路装置を提供する。

【解決手段】スタンダードセル10が横方向に配置されたスタンダードセル列11,12,13,…が、縦方向に並べて配置されている。各スタンダードセル列11,12,13,…は1列おきにフリップされており、スタンダードセル列11,12がP領域を共有し、スタンダードセル列12,13がNウェルを共有している。スタンダードセル列11,12,13の端に位置するPMOSトランジスタ21,22,23からNウェルの端までの距離D1,D2,D3が、スタンダードセル列12,13に共有されたNウェルの幅W1以上になるように、拡げられている。

(もっと読む)

半導体素子および半導体集積回路

【課題】ロジック動作がプログラム可能でかつ不揮発性記憶素子としても動作することが可能な半導体素子を提供することを可能にする。

【解決手段】基板2と、基板上に設けられた第1絶縁膜4と、第1絶縁膜上に設けられた電気抵抗変化膜6と、電気抵抗変化膜の両側面のうちの一方の側面側の第1絶縁膜上に、電気抵抗変化膜の一方の側面に接して設けられた第1電極8と、電気抵抗変化膜の両側面のうちの他方の側面側の第1絶縁膜上に、電気抵抗変化膜の他方の側面に接して設けられた第2電極10と、電気抵抗変化膜上に設けられた第2絶縁膜12と、第2絶縁膜上に設けられた第3電極14と、を備えている。

(もっと読む)

電気アンチヒューズ、製造方法およびプログラミング方法

【課題】電気アンチヒューズ、製造方法およびプログラミング方法を提供する。

【解決手段】非シリサイド化半導体材料の領域(150)を含むリンク(125)を有するアンチヒューズ(100)は、減少した体積抵抗を有する合金を形成するカソード(120)から非シリサイド化半導体材料の領域中への金属またはシリサイドの電気移動によって、減少した電圧および電流で、また減少した熱の生成を伴って、プログラムされ得る。カソード(120)およびアノード(110)は、好ましくは、そこ(例えば160)から、またそこ(例えば、150,110)へ材料が電気的に移動させられるところの領域を制御するように、形作られる。プログラミング後、(925,960での)材料の付加的な電気移動は、アンチヒューズを高抵抗状態に戻すことができる。アンチヒューズが製造される方法は、電界効果トランジスタの製造と完全にコンパチブルであり、アンチヒューズは絶縁構造上で有利に形成され得る。

(もっと読む)

カレントミラー回路

【課題】 インプロセス中で生じるチャージの影響を低減させることで、精度の良いカレントミラー比が得られるカレントミラー回路の構成を提供する。

【解決手段】 カレントミラーを構成する隣合うMOSトランジスタのゲート同士を、直接多結晶シリコンを用いて接続し、基板に接続されたヒューズをゲート部に接続することで、インプロセス中でカレントミラー回路を構成する隣り合うMOSトランジスタのゲートが受けるチャージの影響を同量に緩和させることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 完全空乏型SOIトランジスタを有する半導体装置において、ウエハ面内の閾値を安定化さることが可能な半導体装置の高歩留安定化システムを提供する。

【解決手段】 完全空乏型SOIトランジスタを有する半導体装置において、チャネルドープ量の異なる2つのSOINMOSトランジスタを並列に接続し、ヒューズトリミングで選択できることを特徴とする。

(もっと読む)

81 - 100 / 156

[ Back to top ]