Fターム[5F064GG01]の内容

ICの設計・製造(配線設計等) (42,086) | 製造プロセス技術 (798) | 拡散、イオン注入 (156)

Fターム[5F064GG01]に分類される特許

41 - 60 / 156

半導体装置およびその製造方法

【課題】基板上に抵抗素子を備える半導体装置において、シリコン抵抗素子の抵抗値の低下を防ぐ。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとシリコン抵抗素子を備える。抵抗素子は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層37と、からなる。絶縁膜30は、シリコン酸化膜、シリコン窒化膜、HfSiON、HfO2、ZrO2、HfAlO、Al2O3から選ばれる少なくとも一つを有する。

(もっと読む)

半導体装置

【課題】ポリシリコン配線構造を利用する場合にプログラム後の抵抗値のばらつきがなく高抵抗値化が図れ、良好なプログラム特性や高信頼性を有する半導体装置を提供する。

【解決手段】第1の端子部12aと、第2の端子部12cと、前記第1および第2の端子部の相互間を接続するヒューズリンク12bとを有する半導体装置であって、前記第1の端子部および前記ヒューズリンクは、不純物イオンがドープされたポリシリコン層とその上に積層された金属元素を含む層とを有し、前記第2の端子部は、前記ヒューズリンクとの接続端側に不純物イオンがドープされていないポリシリコン層とその上に積層された金属元素を含む層とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来のものと比較して回路面積が縮小されたヒューズ回路を提供することを課題とする。

【解決手段】ヒューズ素子と、該ヒューズ素子を溶断するに必要な電流を供給するために該ヒューズ素子の一端にそのドレイン領域又はソース領域が電気的に接続されているMOSトランジスタ素子とからなる、前記ヒューズ素子の選択的溶断により電気的にプログラム可能なヒューズ回路を備え、前記ヒューズ素子が前記MOSトランジスタ素子の形成領域の直上の絶縁膜上に位置することを特徴とする半導体装置により、上記課題を解決する。

(もっと読む)

半導体装置

【課題】FD型トランジスタで構成された電気回路において、電気回路に電力を供給する電源のスイッチングトランジスタを基板電圧で制御することができる半導体装置を提供する。

【解決手段】半導体装置は、基板上の第1のFinに形成された第1のトランジスタを含む電気回路と、半導体基板上の第2のFinに形成され、電気回路と電源供給線との間に接続された第2のトランジスタを含む電源回路と、基板に基板電圧を印加するための基板コンタクトとを備え、第1のFinの幅は、第1のトランジスタのチャネル部に形成される最大空乏層幅の2倍以下であり、第2のFinの幅は、第2のトランジスタのチャネル部に形成される最大空乏層幅の2倍よりも大きい。

(もっと読む)

トランジスタ性能に対するシャロートレンチアイソレーション(STI)の応力変動を低減するダミーフィル

【課題】MOSデバイスに加えられる応力の違いに起因するMOSデバイスの性能のドリフトを低減するダミーパターン設計を提供する。

【解決手段】チップ上に集積回路構造を形成する方法は、集積回路構造の設計からアクティブ層を抽出することと、アクティブ層の形状に適合する保護バンドを形成することとを含む。当該保護バンドは、アクティブ層を囲み、X軸方向では第1間隔で、かつY軸方向では第2間隔でアクティブ層から離れて配置される。当該方法はさらに、設計ルールに反する保護バンドの如何なる部分も除去することと、保護バンドの凸角部を除去することと、保護バンドの外側のチップの残りの空間にダミー拡散パターンを付与することとを含む。第1および第2間隔は、集積回路構造のSpiceモデル特性決定での同じ間隔として特定され得る。異なる粒度を有するダミー拡散パターンが、拡散密度がチップ上で実質的に均一になるように付与され得る。

(もっと読む)

半導体装置の製造方法及び設計支援装置

【課題】コンタクト領域の欠損を抑制する技術を提供する。

【解決手段】半導体装置の製造方法は、基板上方に導電膜を形成し、導電膜上に補助パターンを形成し、導電膜及び補助パターンを覆うように金属膜を形成し、金属膜をエッチバックし、補助パターンの側面にサイドウォール膜を形成し、補助パターンを除去し、導電膜及びサイドウォール膜の一部を覆い、一部を露出させるレジストパターンを形成し、レジストパターンをマスクとしてエッチングによりサイドウォール膜の露出している部分を除去し、サイドウォール膜をマスクとして導電膜をエッチングして、ゲート電極及びゲート電極と導通するコンタクト領域を形成し、露出している部分が除去されることにより導電膜上に残存するサイドウォール膜の形状は、ゲート電極及びコンタクト領域の形状に対応し、補助パターンの形状は、コンタクト領域の形状に対応するサイドウォール膜の少なくとも三辺と接する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】半導体集積回路装置の集積度の向上を図ることのできる技術を提供する。

【解決手段】セルの高さ方向に隣接して配置されるセルrow上段の2入力NAND回路6とセルrow下段のインバータ回路1との間の結線に、2層目以上の配線を用いずに、1層目の配線M1よりも下層に位置し、2入力NAND回路6またはインバータ回路1を構成するMISFETのゲート電極7N2,7P2と一体化した導電体膜からなる配線8を用いる。

(もっと読む)

半導体集積回路の検証装置、方法およびプログラム

【課題】意図的に導入された実験箇所を含む半導体集積回路装置のレイアウトデータから本来の欠陥のみを抽出する検証装置を提供すること。

【解決手段】検証装置は、設計者により意図的に導入された実験箇所を含む半導体集積回路のレイアウトデータを検証する装置であって、半導体集積回路に対する設計基準および実験箇所を含む1または2以上の検証ルールを生成する検証ルール生成部と、検証ルールに含まれる実験箇所を検証の対象から除外したレイアウトデータを検証ルールのそれぞれについて生成するレイアウトデータ生成部と、実験箇所を検証の対象から除外したレイアウトデータにおいて設計基準を満たさない箇所である欠陥を検証ルールのそれぞれについて抽出する欠陥抽出部とを備える。

(もっと読む)

半導体集積回路装置

【課題】高精度なトランジスタ間相対比を求められるアナログ回路を実現できる半導体集積回路装置を小型・低コストで提供する。

【解決手段】1つのウェル領域内にMOSトランジスタを1つのみ配し、複数のそのようなMOSトランジスタを組み合わせてアナログ回路ブロックを構成することで、ウェル領域とチャネル領域間距離を同一にすることができ、高精度な半導体集積回路装置とすることができる。

(もっと読む)

半導体装置

【課題】PIDの影響を遮断することのできるレイアウト手法を用いてアンテナダイオードを配置することにより、PIDに起因する電界効果トランジスタの特性劣化を防止して、信頼度の高い半導体装置を実現する。

【解決手段】第1アンテナダイオードAD1とnMISのゲート電極16とを第1層目の配線M1を介して電気的に接続し、第2アンテナダイオードAD2と他の半導体素子とを第1層目の配線M1から第4層目の配線(アナログブロック内の最上層配線から1層下の配線)M4を介して電気的に接続する。さらに第1アンテナダイオードAD1と電気的に繋がる第4層目の配線M4と第2アンテナダイオードAD2と電気的に繋がる第4層目の配線M4とをアナログブロック内の最上層配線である第5層目の配線25によって結線する。

(もっと読む)

半導体装置、半導体装置におけるアンチヒューズ素子のプログラム方法、及び半導体装置の製造方法

【課題】周辺回路にストレスを与えずに選択したアンチヒューズ素子を確実に導通させることのできる半導体装置を提供する。

【解決手段】アンチヒューズ素子(Maf)を含み、第一及び第二の電源(VDD、VSS)から電力が供給されて動作する半導体装置であって、ソースが第三の電源(VPPSV)に、ゲートが制御ノード(AFCTL)に接続されたドライバトランジスタ(PH0)と、一端がドライバトランジスタのドレインに他端が第四の電源(VBBSV)に接続されたアンチヒューズ素子と、第一及び第二の電源に接続され、アンチヒューズ素子の抵抗値を判定する判定回路と、を備え、第三及び第四の電源の電圧を、第一の電源と第二の電源との電圧範囲外の電圧としてアンチヒューズ素子を導通させる。

(もっと読む)

半導体装置及びその製造方法

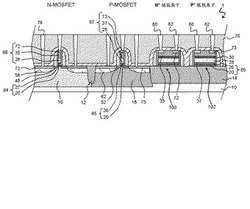

【課題】面積を大きくすることなく遅延量が増大された遅延セルを有する半導体装置を提供する。

【解決手段】Nウェル5に形成されたPMOSトランジスタ50bと、Pウェル6に形成されたNMOSトランジスタ50aとからなるCMOSインバータ50を有し、このNウェル5とPウェル6は上下方向に所定のパターンで配置されており、左右方向に沿って並ぶ、複数の遅延セル9及び通常論理セル17と、

それぞれが、左右方向に沿って、遅延セル9及び通常論理セル17に隣接して配置され、上下方向に所定のパターンで配置されたNウェル5とPウェル6とを有する、複数の空き領域セル8とを備え、

遅延セル9におけるウェルの配置パターンは、左右に隣接する空き領域セル8のパターンを反転したものであり、通常論理セル17におけるウェルの配置パターンは、左右に隣接する空き領域セル8におけるパターンと同じである。

(もっと読む)

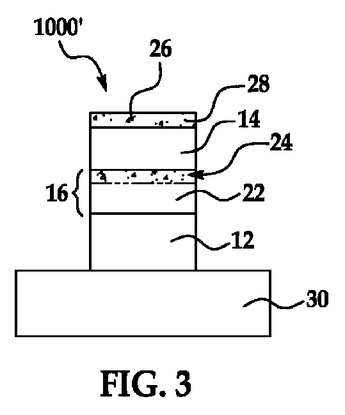

電気的に作動するデバイス及びそのデバイスにおけるドーパントの形成を制御する方法

電気的に作動するデバイスが、第1の電極、第2の電極並びに当該第1及び第2の電極間に堆積させた活性領域を備えている。当該デバイスは、i)第1の電極と活性領域との界面、又はii)第2の電極と活性領域との界面、又はiii)活性領域と第1及び第2の電極のそれぞれとの各界面で局在化された、少なくとも1つのドーパント導入剤又はドーパントをさらに含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】チップ内における配線領域の占有面積の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】ゲート電極、ソース領域およびドレイン領域をそれぞれが有する第1および第2のトランジスタ121,122と、第1トランジスタ121のソースおよびドレイン領域の一方と第2トランジスタ122のソースおよびドレイン領域の一方と互いに連結する拡散領域150とを備える半導体装置110を採用する。

(もっと読む)

パターン形成不良領域算出方法およびパターンレイアウト評価方法

【課題】段差パターンに起因するパターン形成不良領域を、段差パターンレイアウト面内で正確かつ短時間に算出する露光不良領域算出方法を得ること。

【解決手段】基板上の段差パターンとしてゲートG1を形成した後、ゲートG1よりも後にピラーパターンPを形成するとピラーパターンPがパターン形成不良となる領域を不良発生危険度マップ21として算出するために、基板面内でのゲートG1のパターンからの距離と露光不良領域となる可能性に関する情報との対応関係と、ゲートG1のパターン形成に用いたレイアウトと、を用いる。

(もっと読む)

回路シミュレーション装置、回路シミュレーション方法及びプログラム

【課題】回路シミュレーションの精度を向上する。

【解決手段】回路シミュレーション装置30は、集積回路のレイアウトデータから、対象MOSトランジスタ11のゲート12と対象MOSトランジスタ11に隣接するMOSトランジスタ15、16のゲート17、18との間のゲート間隔Ss、Sdを抽出し、抽出されたゲート間隔Ss、Sdから対象MOSトランジスタ11のトランジスタモデルパラメータvth0’を算出するパラメータ算出手段と、算出されたトランジスタモデルパラメータvth0’を用いて前記集積回路の回路シミュレーションを行う回路シミュレーション手段とを備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】閾値電圧が互いに同一であることを要求される2つのトランジスタにおいて、閾値電圧が異なる値になることを抑制する半導体装置の製造方法及び半導体装置を提供する。

【解決手段】第1素子形成領域12には第1トランジスタ202及び第2トランジスタ204が形成され、第2素子形成領域13には第3トランジスタ302が形成される。これら3つのトランジスタは同一導電型である。第1トランジスタ202及び第2トランジスタ204は同一の閾値電圧を有する。第1マスクパターンを用いて第1素子形成領域12に第1ウェル210を形成し、第2マスクパターンを用いて第2素子形成領域13に第2ウェル410を形成する。第1トランジスタ202のチャネル領域及び第2トランジスタ204のチャネル領域は基準線Lを介して線対称な形状を有している。また第1マスクパターンも、基準線Lを介して線対称な形状を有している。

(もっと読む)

半導体集積装置及び自動配置配線方法

【課題】セル内の抵抗成分を考慮して自動配置配線が行われた高密度セルを備えた半導体集積装置及び自動配置配線方法を提供する。

【解決手段】ライブラリ内に蓄積されたセルX1及びセルY2を含む2種類以上のセルから、所定の条件に基づいて選択されたセルが配列された半導体集積装置であって、ライブラリ内に格納された各々のセルの拡散抵抗値を示す情報に基づいて、隣接する列において自動配線配置における最大値ルールを満たすように選択されたセルX1、セルY2が配列されている。

(もっと読む)

半導体装置及びその製造方法

【課題】追加工程なくフューズ下に配線等を配置可能な半導体装置及びその製造方法を提供する。

【解決手段】この半導体装置は、絶縁層に設けられた複数の第1キャパシタ孔52と、第1キャパシタ孔52に形成された容量素子Cと、容量素子Cと結合するトランジスタTrとからなるDRAMセルと、絶縁層に設けられた複数の第2キャパシタ孔40と、第2キャパシタ孔40の間に形成されるフューズ素子(31、51)と、を備えている。

(もっと読む)

半導体集積回路の設計方法、製造方法、回路設計プログラム、及び半導体集積回路

【課題】レイアウト修正による遅延変動を抑制しつつ半導体集積回路のプラズマダメージを軽減する製造方法を提供する。

【解決手段】半導体集積回路の製造方法は、コンピュータによって実行され、第1ゲート電極21に接続する金属配線と、第1ゲート電極21とのアンテナ比を検証するステップと、アンテナ比の検証結果に基づいて半導体集積回路のレイアウトを変更するステップとを具備する。レイアウトを変更するステップは、複数の論理セルから、アンテナ比の検証結果に応じたゲート面積の論理セルを選択するステップと、論理セルを、論理動作しないフィルセル40として空き領域に配置するステップと、フィルセル内の第2ゲート電極41を金属配線に接続するステップとを備える。

(もっと読む)

41 - 60 / 156

[ Back to top ]