Fターム[5F064GG01]の内容

ICの設計・製造(配線設計等) (42,086) | 製造プロセス技術 (798) | 拡散、イオン注入 (156)

Fターム[5F064GG01]に分類される特許

141 - 156 / 156

ヒューズ素子の切断方法、ヒューズ素子及びヒューズ素子を有する半導体装置

【課題】 装置の信頼性低下を回避することができるヒューズ素子の切断方法を提供する。

【解決手段】 半導体基板上に形成されたヒューズ素子に、電気パルスを複数回印加し、該ヒューズ素子を切断する。

(もっと読む)

スタンダードセル構造

【課題】 スタンダードセルのレイアウト設計時にトランジスタ特性の精度を安定させる処理を加える。

【解決手段】 本発明は、PチャネルトランジスタとNチャネルトランジスタが電源電極と接地電極との間でチャネル幅方向に配置されたスタンダードセルであって、チャネル幅方向に沿って基本となる拡散領域が複数分離して形成されていることを特徴とするスタンダードセルを開示する。

(もっと読む)

異なるゲート酸化膜の厚さに関する方法および装置

パスゲートトランジスタのための向上されたオン−オフ変化を有する集積回路が、提供される。該集積回路は、コアトランジスタとパスゲートトランジスタとを含むコア領域を含む。コアトランジスタは、第1の厚さと関連付けられたゲート酸化膜を有し、パストランジスタは、第1の厚さよりも小さな厚さと関連付けられたゲート酸化膜を有する。一実施形態において、パスゲートトランジスタのゲート酸化膜のために用いられる材料は、4より大きな誘電率を有し、一方で、コアトランジスタのゲート酸化膜のために用いられる材料は、4以下の誘電率を有する。集積回路を製造するための方法も、提供される。  (もっと読む)

(もっと読む)

半導体装置の設計方法および半導体装置の製造方法

【課題】イオン注入工程での高精度なリソグラフィ技術を削減する。

【解決手段】半導体装置の設計方法は、トランジスタが形成される複数の半導体領域16,18をそれぞれが含む複数のスタンダードセルSCを複数の行に配置し、各行で隣接する2つのスタンダードセルの隙間を埋め込むように、複数の埋め込みセル13を配置し、複数の半導体領域16,18に対応し、かつトランジスタのしきい値電圧を調整するための複数のチャネルインプラ領域14を配置し、各行で隣接する2つのチャネルインプラ領域にデザインルールに基づく最小間隔違反が発生した場合に、該当する2つのチャネルインプラ領域を埋め込みセル13を用いて合成し、合成されたチャネルインプラ領域の形状を用いてマスク15を作成する。

(もっと読む)

半導体装置構造および半導体装置の製造方法

【課題】 塗布絶縁膜からの脱ガス反応を押さえ、塗布絶縁膜の変形やクラック等を回避して半導体装置としての信頼性向上をはかる。

【解決手段】 ヒューズ素子の側壁部もしくはそれを覆う絶縁談をテーパ形状に加工することにより、ヒューズ素子の近隣に存在する塗布絶縁膜との距離を大きくすることで塗布絶縁膜へ加わる熱ストレスを緩和し、塗布絶縁談からの脱ガス反応を押さえ塗布絶縁談の変形やクラック等を避ける。また、ヒューズ素子の側壁部もしくはそれを覆う絶縁膜にサイドスペーサを形成し、あるいはヒューズ素子の側壁部とさらにそれを覆う絶縁談にもサイドスペーサを形成することにより、一層、ヒューズ素子の近隣に存在する塗布絶縁膜との距離を大きくする。

(もっと読む)

混合された相互接続リソースを備えたFPGAアーキテクチャ

FPGAは、相互接続リソースが2つのグループに分けられたプログラム可能相互接続構造を含む。相互接続リソースの第1のサブセットは高スピードに対して最適化される。相互接続リソースの第2のサブセットは低電力消費に対して最適化される。実施例によっては、第1および第2のサブセットのトランジスタは異なるしきい値電圧を有する。スピードに対して最適化されている第1のサブセットのトランジスタは、低電力消費に対して最適化される第2のサブセットのトランジスタより低いしきい値電圧を有する。しきい値電圧の差は、異なるドーピングレベル、異なる電圧レベルにバイアスされた井戸を使用することによって、または他の既知の手段を使用することによって実現可能である。実施例によっては、相互接続リソースの第1のサブセットは、第2のサブセットより高い電圧レベルに結合されたバッファを含む。実施例によっては、第1のサブセットは、第2のサブセットのものより大きいトランジスタを使用して製造されたバッファを含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体装置において、製造工程を増加させることなく、保護回路が占める面積を縮小する。

【解決手段】電極パッド7の形成領域において、P型半導体基板3の表面にフィールド酸化膜21によって互いに分離されてN+拡散領域19a,19b,19cが形成されている。フィールド酸化膜21上及び絶縁膜23上に下層メタル配線層25a,25b,25cが形成されている。さらにその上に層間絶縁層27を介してVccライン13a、GNDライン13b及びメタル配線層13cが形成されている。Vccライン13a及びGNDライン13bは複数の電極パッド7の形成領域にまたがって連続して形成されている。さらにその上に層間絶縁膜29を介して電極パッド7が形成されている。Vccライン13aとN+拡散領域19a、GNDライン13bとN+拡散領域19b、及び電極パッド7とN+拡散領域19cはそれぞれ電気的に接続されている。

(もっと読む)

半導体集積回路、および、半導体集積回路の配置配線方法

【課題】 従来のスタンダードセル方式にて形成される半導体集積回路では、機能変更のための開発に膨大な期間を要する可能性があった。また、大規模な機能変更に対応できない可能性があった。

【解決手段】 上述した課題を解決すべく、本願発明の半導体集積回路では、半導体基板には、所定機能を実現するための複数のスタンダードセルと、所定機能を変更する際に用いられる予備スタンダードセルとが配置され、半導体基板は、複数のスタンダードセルが一列に並んで配置されるセル行を複数列備え、セル行には、前記スタンダードセルが配置されない空き領域が設けられ、予備スタンダードセルはこの空き領域に配置されている。

(もっと読む)

半導体装置

【課題】信頼性に優れる半導体装置を提供する。

【解決手段】半導体装置のSi基板120上には、フィールド酸化膜101が設けられている。フィールド酸化膜101上には、2本のヒューズ104が設けられている。Si基板120のうちヒューズ104の直下には、n型ウェル102が設けられている。n型ウェル102は、Si基板120のうちヒューズ104の直下の領域を囲む姿態にp型ウェル103が設けられている。Si基板120およびフィールド酸化膜101の上部には、絶縁膜105およびカバー絶縁膜108が設けられている。絶縁膜105およびカバー絶縁膜108には、ヒューズ104を囲むように、コンタクト106および配線107からなるシールリングが埋設されている。

(もっと読む)

半導体記憶装置及びその製造方法。

【課題】電気的に機能を切り替えるヒューズ素子を有する半導体記憶装置において、ヒューズの占める面積を小さくし、且つ、ヒューズ切断に使用する電源の信頼性が高い半導体記憶装置を提供する事を課題とする。

【解決手段】デバイスの機能切り替えにヒューズ素子を用いた半導体記憶装置において、同一工程からなる2配線間にボイドを設け、前記ボイド内に導電性材料を埋め込んだものを電気溶断ヒューズとして用いる事により解決する。

(もっと読む)

プログラマブル半導体デバイス

【課題】 プログラミングの間に隣接するデバイスまたは他の要素に対して巻き添え被害を引き起こさないプログラマブル半導体デバイスを提供すること。

【解決手段】 プログラマブル・デバイスは、基板(10)と、基板上の絶縁体(13)と、絶縁体上の細長い半導体材料であって、第1および第2の端部、ならびに上面Sを有し、第1の端部(12a)が第2の端部(12b)よりも実質的に広い、半導体材料と、上面上に配置された金属材料であって、半導体材料を介しておよび金属材料を介して流れることができる電流Iに応答して、上面に沿って物理的に移動可能な金属材料と、

を含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】 半導体装置の冗長用ヒューズの切断面で発生するESDサージを防止し、内部回路のトランジスタを保護することを目的とする。

【解決手段】 半導体基板1と、半導体基板1表面に形成されたフィールド絶縁膜2と、フィールド絶縁膜2上に形成されたヒューズ4と、ヒューズ4を覆う絶縁膜5と、絶縁膜5を覆うとともにヒューズ4の上方において開口部10が形成された絶縁膜8と、開口部10内で露出するように絶縁膜5上に形成され、基板電位または電源電位の何れかに接続された導電膜7と、を備えることを特徴とする半導体装置。

(もっと読む)

自動設計システム、自動設計方法及び半導体装置の製造方法

【課題】 電気的特性が均一なトランジスタを設計可能な自動設計システムを提供する。

【解決手段】 複数のトランジスタのレイアウトデータから複数のトランジスタのそれぞれの拡散領域の面積を計算する面積計算部101と、拡散領域のゲート長方向の寸法が最も小さいレイアウトデータを基準レイアウトデータとして定義する基準データ定義部102と、拡散領域のゲート長方向の寸法、面積、イオン注入条件及び熱処理条件に基づいて、実効チャネル長を予測する構造予測部201と、複数のトランジスタの総ての実効チャネル長と、基準レイアウトデータに基づく実効チャネル長との有意差がなくなるよう、複数のトランジスタのレイアウトデータに含まれる複数のゲート電極のレイアウトパターンのそれぞれのゲート長を補正する補正部400とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】電気的に切断されやすいヒューズ素子を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明のヒューズ素子4は、回路を遮断する部分である第1の領域4aと、第1の領域4aの両端に接し、第1の領域4aよりもパターン幅の広い第2の領域4bおよび第3の領域4cとからなる。ヒューズ素子4のうち第2の領域4b、第1の領域4aおよび第3の領域4cのうちの一部は厚膜絶縁膜2の上に設けられているのに対し、第3の領域4cのうちの他部は薄膜絶縁膜3の上に設けられている。ヒューズ素子4で発生した熱は、厚膜絶縁膜2を介して半導体基板1へ放熱しにくいのに対し薄膜絶縁膜3を介して放熱しやすいため、ヒューズ素子4内の温度変化および温度勾配が大きくなるため、第1の領域4aが電気的に切断されやすくなる。

(もっと読む)

電子的プログラマブル・アンチヒューズおよびそれにより形成された回路

【課題】 電子的プログラマブル・アンチヒューズおよびそれにより形成された回路を提供することにある。

【解決手段】 アンチヒューズ・デバイス(120)は、バイアス・エレメント(124)とアンチヒューズ・エレメント(128)との間に位置する出力ノード(F)を有する分圧器を形成するために、互いに直列に配置されたバイアス・エレメントとプログラマブル・アンチヒューズ・エレメントとを含む。アンチヒューズ・デバイスがそのプログラム化されていない状態にあるときに、バイアス・エレメントとアンチヒューズ・エレメントのそれぞれは非導電性になる。アンチヒューズ・エレメントがそのプログラム化された状態にあるときに、バイアス・エレメントは非導電性のままであるが、アンチヒューズ・エレメントは導電性になる。そのプログラム化されていない状態とプログラム化された状態とのアンチヒューズ・エレメントの抵抗の差により、1Vの電圧がアンチヒューズ・デバイスの両端間に印加されたときに出力ノードで見られる電圧の差が数百ミリボルト程度になる。この電圧差は、単純な感知回路を使用して容易に感知できるほど大きいものである。

(もっと読む)

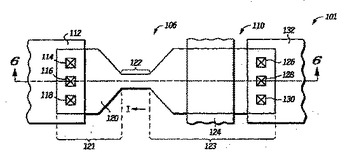

フューズ及びその形成方法

アクティブフューズはアクティブフューズ構造(120)を備え、この構造を使用して可変抵抗体(106)及び選択トランジスタ(110)の双方を形成する。一の実施形態では、アクティブフューズ構造は、半導体基板(140)の活性領域(160)の一部に形成され、選択ゲート(124)はアクティブフューズ構造の一方の端部(123)の上に配置されてアクティブフューズへの書き込みに使用する一体型選択トランジスタ(110)を形成する。共有型のアクティブフューズ構造を活性領域の内部に使用することによって、面積要件を縮小し、かつ検出マージンを大きくすることができる。  (もっと読む)

(もっと読む)

141 - 156 / 156

[ Back to top ]