Fターム[5F083AD04]の内容

半導体メモリ (164,393) | DRAM (5,853) | 読出しトランジスタ (1,433) | 水平方向以外のチャネルを有するもの (541) | トレンチゲートトランジスタ(単孔にゲートを埋込むもの) (266)

Fターム[5F083AD04]に分類される特許

121 - 140 / 266

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域における電界の部分的な集中を防止する。

【解決手段】半導体装置は、分離絶縁領域(6)に囲まれた活性領域に形成された第1の拡散領域と第2の拡散領域と、第1の拡散領域と第2の拡散領域との間に形成された溝状のトレンチ領域と、トレンチ領域上に形成されたゲート絶縁膜(10)と、トレンチ領域を埋め込むようにゲート絶縁膜上に形成されたゲート電極(11)と、ゲート絶縁膜と分離絶縁領域とで挟まれた領域のうち上層側に位置する領域に形成された保護絶縁膜(4)と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】レジストパターン露光時の分離マージン不足の解消と同時にドライエッチング加工の局所ばらつきを解消し、工程数の増大及び煩雑化を抑えたビットコンタクトの形成方法を提供する。

【解決手段】活性領域を含む半導体基板上に、活性領域と交差するワード配線形成工程、拡散層領域形成工程、ビットラインの形成高さまで第1の絶縁膜を形成する工程、第1の絶縁膜上に活性領域の延在方向上にライン状の開口を有するパターンをマスクとして第1の絶縁膜をエッチングし、半導体基板表面を露出する溝パターンを形成する工程、溝パターン内に導電膜を埋め込む工程、第1の絶縁膜上にビットコンタクト形成部上を通過するマスクパターンを形成する工程、マスクパターンをマスクとして、第1の絶縁膜及び導電膜をワード配線の上層絶縁膜が露出するまで除去し、ビットコンタクトと他のコンタクトとを分離する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの下部電極のダメージを抑制することができる半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置は、立設する複数の電極と、前記電極の立設を保持する第1の絶縁膜と、前記電極が貫通するように前記第1の絶縁膜に形成され、各々の前記電極の外周側面の少なくとも一部に接触する複数の孔部と、前記第1の絶縁膜に形成され、前記複数の孔部のうちその一部の孔部に連結する第1の開口と、前記第1の絶縁膜に形成され、前記複数の孔部のいずれの孔部に対してよりも前記溝部に近接する位置に配置すると共に前記複数の孔部のいずれにも連結しない第2の開口とを、備えたことを特徴とすることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ライナー用シリコン窒化膜を備えたSTI構造の素子分離領域の外周に、段部が形成されることのない半導体装置を提供する。

【解決手段】ライナー用シリコン窒化膜25を備えたSTI構造の素子分離領域27によって活性領域が区画された半導体基板21上に、シリコン酸化膜28を形成する工程と、前記シリコン酸化膜28上に、パターニングされたポリシリコン膜31を形成する工程と、前記ポリシリコン膜31をマスクにして、前記シリコン酸化膜28と前記半導体基板21とをエッチングして、溝パターンを形成する工程と、を備えていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】フッ酸に対する化学耐性を備え、650℃以下の低温で形成可能な窒化シリコンを堆積してキャパシタ電極のサポート用絶縁膜や薬剤浸透防止用の層間絶縁膜を備えた半導体装置の製造方法を提供する。

【解決手段】コンタクトプラグがその上端を露出するように埋込まれた下部層間絶縁膜上に、薬剤浸透防止用の窒化シリコンからなる第1層間絶縁膜を形成する工程と、第1層間絶縁膜上に第2層間絶縁膜を形成する工程と、第2層間絶縁膜上にキャパシタ素子の下部電極の立設を保持するための窒化シリコンからなるサポート用絶縁膜を形成する工程と、サポート用絶縁膜を一部残存させて、第2層間絶縁膜を湿式エッチングにより除去してキャパシタ素子の下部電極を形成する工程とを備え、第1層間絶縁膜及びサポート用絶縁膜の少なくとも一方を高密度プラズマCVD法で形成する半導体装置の製造方法とする。

(もっと読む)

キャパシタ用容量絶縁膜の製造方法

【課題】キャパシタ用容量絶縁膜として、比較的低温で容易に、ルチル結晶構造のTiO2膜を形成する方法を提供する。

【解決手段】半導体基板1上に酸化シリコン膜2を形成し、スパッタ法を用い、基板温度を300℃、チャンバー内をAr雰囲気で圧力0.5Paに保持した状態でTiターゲットのスパッタリングを行ってTi膜3を成膜し、該Ti膜3を酸素ガスを供給する熱処理炉を用いたファーネスアニールによって、アニール酸化を行い、ルチル結晶構造を有するTiO2膜4とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高集積であり且つビット線を埋め込む必要のない3次元トランジスタを有する半導体記憶装置を提供する。

【解決手段】ゲートトレンチを介して両側に位置する第1及び第2の拡散層とゲートトレンチの底面に形成された第3の拡散層とを有する活性領域と、第1及び第2の拡散層にそれぞれ接続された第1及び第2の記憶素子と、第3の拡散層に接続されたビット線と、ゲート絶縁膜を介してゲートトレンチの第1の側面を覆い、第1の拡散層と第3の拡散層との間にチャネルを形成する第1のゲート電極と、ゲート絶縁膜を介してゲートトレンチの第2の側面を覆い、第2の拡散層と第3の拡散層との間にチャネルを形成する第2のゲート電極とを備える。本発明によれば、ゲートトレンチの両側面にそれぞれ別のトランジスタが形成されることから、従来の2倍の集積度が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体界面のダングリングボンドを終端させて、リーク電流が少ない半導体装置の製造方法を提供する。

【解決手段】ボンディングパッド40が設けられる最上層の配線層39の上に、フッ素を含んだ介在層41としてCVD法によりよって形成されたフッ素含有酸化シリコン膜(SiOF)を設ける。この上にパッシベーション膜42としてプラズマCVD法により形成した窒化シリコン膜を設け、フッ素に対するバリアとする。この後熱処理を行い、フッ素をシリコン基板の表面に拡散させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル部でアスペクト比の高い下部電極の倒壊を防止するとともに、前記メモリセル部に隣接する周辺回路部への薬液の浸透を防止する半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】メモリセル部と、前記メモリセル部を囲む周辺回路部と、を有する半導体装置であって、前記メモリセル部は、複数の筒状の下部電極13と、下部電極13の側面を覆う第1の絶縁膜と、前記第1の絶縁膜を覆う上部電極15と、を有するキャパシタ30を備えたメモリセル本体部55と、メモリセル本体部55を囲む溝部73を備えたメモリセル外周部56と、を有しており、下部電極13の筒内に充填された第1の支持膜61と、第1の支持膜61の開口側の面に接面されるとともに複数の下部電極13を結ぶように延在された第2の支持膜62と、を有する半導体装置を用いることにより、上記課題を解決できる。

(もっと読む)

キャパシタ用絶縁膜、キャパシタ及び半導体装置

【課題】高い誘電率を示すキャパシタ用絶縁膜は、キャパシタに用いられた際にリーク電流が増大する。

【解決手段】2つの電極の間に挟まれて用いられるキャパシタ用絶縁膜を、チタン酸ストロンチウム又はチタン酸バリウムストロンチウムのチタンサイトの一部がハフニウム元素で置換された結晶から形成する。

(もっと読む)

半導体素子およびその製造方法

【課題】 サドルフィン形態のチャンネルを形成する際に、ゲートパターンとプラグとの間のブリッジ発生を防止することが可能な半導体素子およびその製造方法を提供する。

【解決手段】 半導体素子は、半導体基板と、半導体基板内に活性領域を限定するように形成された素子分離膜と、活性領域および素子分離膜に形成されたゲート用リセスパターンと、リセスパターン内およびリセスパターン上に形成されたゲートパターンと、ゲートパターンを覆うように形成されたゲートスペーサとを含み、ゲート用リセスパターンは、活性領域では第1深さを有し、素子分離膜では第1深さよりも深い第2深さを有し、ゲートパターンと素子分離膜のゲート用リセスパターン上部側面との間には空間が形成されて、ゲートスペーサが前記空間を埋め立てる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】酸素ガスを主に含有したガスでエッチングを行う必要がある金属材料を用いてピラー型電極を形成する際に、ピラー型電極のアスペクト比が高くなると製造が困難になるという課題があった。

【解決手段】層間絶縁膜上に第1〜第6の絶縁膜を積層した後、第1のフォトレジスト膜を形成する工程と、前記第1のフォトレジスト膜をマスクとして第1の溝部を形成する工程と、前記第1の溝部を充填するように電極材料を堆積する工程と、前記第4の絶縁膜上に第7〜第9の絶縁膜を形成した後、第2のフォトレジスト膜を形成する工程と、前記第2のフォトレジスト膜をマスクとして第2の溝部を形成すると共に、前記電極材料をピラー型に残存させる工程と、前記第8、前記第7、前記第4および前記第2の絶縁膜を除去して、前記電極材料からなるピラー型電極を露出する工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置およびその製造方法

【課題】筒型の下部電極の高さが高くなっても倒壊現象の発生を抑止する効果が十分に得られる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、内周壁及び外周壁を有する筒型の下部電極21と、容量絶縁膜22を介して下部電極21の外周壁を覆う上部電極23とを有する複数のキャパシタ20と、下部電極21の内周壁に囲まれた内部領域に充填される被充填部30aと、一部が内部領域内に位置し他の部分が内部領域外に位置するサポート膜30とを備え、支持部30bは、下部電極21の上端部21esにおける内周壁及び外周壁を覆うことにより、下部電極21の上端部21esを両側から挟む。

(もっと読む)

半導体装置及びその製造方法

【課題】十分な保持強度を備えることでキャパシタ下部電極の倒壊を防止し、製造が容易なサポート膜を備えた半導体装置を提供する。

【解決手段】設計ルールFの数値によってサイズが規定される6F2型のメモリセルを備えた半導体装置であって、前記メモリセルに含まれるキャパシタの下部電極がサポート膜で保持されており、該サポート膜は第1の方向に直線状に延在する第1のサポートパターン(14x)と、前記第1の方向と直交する第2の方向に直線状に延在する第2のサポートパターン(14y)との組合せのパターンで形成され、前記第1及び第2のサポートパターンの間隔は共に1.5F以上であり、前記第1又は第2のサポートパターンのいずれか一方の間隔は、前記第1又は第2のサポートパターンの他方の間隔よりも大きくなるように配置する。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ状態でのリーク電流を抑制したMOSトランジスタを有する回路領域と、オン状態でのドレイン電流を大きいMOSトランジスタを有する回路領域と、を備えた半導体装置を提供する。

【解決手段】第1のMOSトランジスタは、第1の不純物領域として、半導体基板内に設けられた第1の領域及び第1の領域の上方に突出するように設けられた第2の領域からなる第1のソース/ドレイン領域を有する。第2のMOSトランジスタは、半導体基板内に設けられた第2の不純物領域と、第2の不純物領域に接触して半導体基板の上方に突出する第3の不純物領域と、第3の不純物領域上に第4の不純物領域とを有する第2のソース/ドレイン領域を有する。第3の不純物領域は、第4の不純物領域よりも不純物濃度を低くし、第1の不純物領域は、第2の不純物領域よりも不純物濃度を低くする。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層が第1不純物拡散層まで拡がるのを抑制し、複数種類のトランジスタを自由に設計することが可能な半導体装置及びその製造方法を提供する。

【解決手段】少なくとも、基台部1Bの上に複数立設された柱状のピラー部1Cを含むシリコン基板1と、基台部1Bの側面1bを覆うように設けられるビット線6と、ピラー部1Cの側面を覆うゲート絶縁膜4と基台部1Bの上面1aにおいて、ピラー部1Cが設けられる位置以外の領域に設けられる第1不純物拡散層8と、ピラー部1Cの上面1dに形成される第2不純物拡散層14と、ビット線6とシリコン基板1との間に形成され、第1不純物拡散層8との間で高低差を有し、且つ、上端5aが、第1不純物拡散層8の上端8aよりも低い位置に配されてなる第3不純物拡散層5と、ピラー部1Cの側面1c側に設けられるワード線10の一部をなすゲート電極10Aと、が備えられる。

(もっと読む)

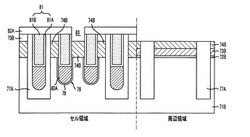

半導体装置

【課題】隣接するゲート電極間がショートすることを防止して、半導体装置の製造歩留まりを向上させる。

【解決手段】メモリセル領域に溝型ゲート電極構造のMOS型トランジスタ、周辺回路領域にはプレーナー型ゲート電極構造又は溝型ゲート電極構造のMOS型トランジスタが形成されるDRAMにおいて、ダミートランジスタ及び電界効果型トランジスタを第2の方向21に配列して、ダミートランジスタは第2の方向21に関して少なくとも一方の端に配置し、ダミートランジスタのゲート電極の埋設部36が電界効果トランジスタのゲート電極の埋設部36よりも第2方向21の幅が短い。

(もっと読む)

半導体装置

【課題】高温の酸化性雰囲気中でのSOD膜の改質を促進する。ライナー膜下部の素子や半導体基板が酸化されてダメージを受けることを防止する。

【解決手段】凹部と、凹部の内壁側面上に順に形成した、第1のライナー膜と、酸素原子を含有する第2のライナー膜と、凹部内に充填された絶縁領域と、を有し、第1のライナー膜は第2のライナー膜よりも耐酸化性が優れるものとした半導体装置。

(もっと読む)

キャパシタ用絶縁膜、キャパシタ素子、キャパシタ用絶縁膜の製造方法及び半導体装置

【課題】キャパシタ用絶縁膜として、10nm程度に薄膜化したチタン酸ストロンチウム(STO)膜においても、高い比誘電率を達成する。

【解決手段】X線回折法により測定した結晶面方位(200)と(111)のスペクトルの強度比率(200)/(111)が1.0〜2.3の範囲のSTO膜を用い、このSTO膜は、酸化チタン(TiOx)膜を所定の膜厚に堆積した後に、非晶質状態のSTO膜の堆積を行い、非活性ガス雰囲気中で熱処理を行って結晶化した状態のSTO膜とすることで得られる。

(もっと読む)

121 - 140 / 266

[ Back to top ]