Fターム[5F083AD04]の内容

半導体メモリ (164,393) | DRAM (5,853) | 読出しトランジスタ (1,433) | 水平方向以外のチャネルを有するもの (541) | トレンチゲートトランジスタ(単孔にゲートを埋込むもの) (266)

Fターム[5F083AD04]に分類される特許

81 - 100 / 266

半導体装置及びその製造方法

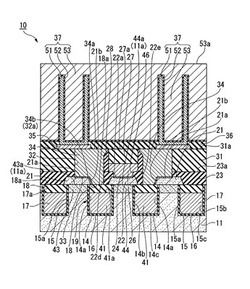

【課題】本発明は、コンタクトプラグと埋め込み型のゲート電極との間に配置される絶縁膜の厚さを十分に確保可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜16を介して、半導体基板11に形成された凹部14の凹部14の一部を埋め込むゲート電極41と、ゲート電極41の上端面41aを覆うように凹部14内を埋め込む絶縁膜18と、凹部14の一方の側面14a側に位置する半導体基板11の主面11aに形成された不純物拡散領域43と、不純物拡散領域43の上面43aを覆うシリコン層21と、半導体基板11の主面11aに形成された第1及び第2の層間絶縁膜23,31に内設され、シリコン層21の上面21aと接触し、かつ下端34bがシリコン層21の上面21aと絶縁膜18の上面18aとの間に配置されたコンタクトプラグ34と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】簡便な方法でキャパシタ容量の増大を図り、また、キャパシタと同層に形成されるコンタクトプラグの製造を容易とする。

【解決手段】メモリセル部の層間絶縁膜(10,20)にバリア膜とメタル膜の二層構造のコンタクトプラグをいったん形成し、その上に層間絶縁膜(21,22)を積層し、コンタクトプラグ上面を露出する開口を形成し、メタル膜を選択的に除去した後、残存するバリア膜と一体となったキャパシタの下部電極を形成する。周辺回路部では、上層配線31と下層配線6Bとを接続するコンタクトプラグを2段(41、42)とする。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化を行った場合であっても、下部電極の倒壊を防止して静電容量の大きいキャパシタ素子を容易に形成する。

【解決手段】半導体装置は、下部電極、容量絶縁膜、及び上部電極を有するキャパシタを複数、備える。各キャパシタの下部電極は、底部及び筒状の側壁部を有する。各下部電極の側壁部における底部側の端部の外壁側面上には、第1の支持部が設けられている。また、各下部電極の側壁部の第1の支持部で覆われていない外壁側面の少なくとも一部に接するように第2の支持部が設けられている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】本発明はコンタクト開口をエッチングにより形成する際の、埋込絶縁膜のエッチングを防ぐことが可能な半導体装置の構造の提供を目的とする。

【解決手段】本発明の半導体装置1は、半導体基板5と、前記半導体基板5の一面に形成されたトレンチ7内にゲート絶縁膜7Aを介して形成された埋込ワード線9と、前記トレンチ7内の前記埋込ワード線9上に順次積層された第一のライナー膜10、第一の埋込絶縁膜11、第二のライナー膜10aおよび第二の埋込絶縁膜11aからなる絶縁層20と、を具備してなることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ボーイング形状に形成される深孔をストレート形状にする。

【解決手段】シリコン窒化膜4上に、不純物ドープした第1のシリコン酸化膜5と、不純物非ドープの第2のシリコン酸化膜6の積層構造の層間絶縁膜に、ドライエッチングによりボーイング形状の第1のホール8を形成し、熱リン酸を用いたウエットエッチングによりシリコン窒化膜4と第1のシリコン酸化膜5とを後退させてボーイング部の下部を拡幅した第2のホール9を形成する。

(もっと読む)

半導体基板、半導体装置、および半導体装置の製造方法

【課題】半導体装置の製造工程において、十分にゲッタリング効果を得ることができる半導体基板を提供する。

【解決手段】半導体からなる基板本体8と、前記基板本体8上に形成されたリンを含有したシリコン酸化膜からなる絶縁層6と、該絶縁層6上に設けられた半導体層7と、を備えることを特徴とする半導体基板3を提供する。また、半導体からなる基板本体8と、前記基板本体8上に形成されたリンを含有したシリコン酸化膜からなる絶縁層6と、該絶縁層6上に設けられた半導体層7を備える半導体基板3と、前記半導体層7上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記半導体層7内であって、前記ゲート電極に対して自己整合となる位置に設けられた不純物拡散領域と、を有することを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】チャネル領域を従来よりも拡大することが可能な半導体装置を提供する。

【解決手段】埋め込みゲート用の溝部9,10のうち、活性領域6に形成される第1の溝部9よりも素子分離領域5に形成される第2の溝部10の深さを深くすることによって、第2の溝部10の底面の間から活性領域6の一部が突き出した第1のフィン部12aと、埋め込みゲート用の溝部9,10の少なくとも上面開口部よりも下部側において、第1の溝部9よりも第2の溝部10の第1の方向における幅を大きくすることによって、第2の溝部10の両側面の間から第1のフィン部12aに連続して活性領域6の一部が突き出した一対の第2のフィン部と12bとを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明ではフォトリソグラフィー技術解像限界付近のパターン形成を安定して形成すると共に、コンタクトプラグなどの構造物における目合わせずれや接触面積の縮小による接触電気抵抗の増大や接続不良を解決する。

【解決手段】半導体基板上に形成された絶縁材料層100に、第1の方向に延在し、底部の幅W1より上部の幅W2が広い第1の溝101を形成する工程と、第1の溝101内に、溝の上端より低い位置まで埋め込み層102を形成する工程と、埋め込み層102上に露出している第1の溝101の側壁を覆うサイドウォール103を形成する工程と、サイドウォール103をマスクとして埋め込み層102をエッチングして第1の方向に分離する工程と、

を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】本発明は、不純物拡散層と半導体基板との間に形成される空乏層中におけるGIDLを抑制することのできる半導体装置を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成された第2の溝32と、少なくとも第2の溝32の側面32aを覆うゲート絶縁膜38と、ゲート絶縁膜38を介して、第2の溝32の側面32aに形成され、その上端面45aが半導体基板11の表面11aより低い位置にあってゲート電極39となる第1の導電膜45と、第1の導電膜45に形成され、その上端面46aが第1の導電膜45の上端面45bよりも高く、かつ半導体基板11の表面11aより低い位置にあってゲート電極39となる第2の導電膜46と、第1の導電膜45の上端面45b、及び第1の導電膜45の上端面45bから突出した第2の導電膜46を覆うように、第2の溝32内に設けられた第2の絶縁膜と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】簡易な追加工程を設けることで、基板のベベル部から膜が剥離することを抑制する。半導体装置の製造歩留まりの低下を抑制すると共に、製造コストの増加を抑制する。

【解決手段】半導体基板上の全面に、1以上の膜を有する構造を形成した後、膜構造上にパターンを有する第1のマスクを形成する。ベベル部上の第1のマスクを覆うように第2のマスクを形成する。第1のマスク及び第2のマスクを用いて、膜構造をエッチングした後、残留した第1のマスク及び第2のマスクを除去する。

(もっと読む)

キャパシタおよびその製造方法、半導体装置

【課題】比誘電率が高く、リーク耐圧に優れた容量絶縁膜を用いたキャパシタを提供する。

【解決手段】下部電極1と、下部電極1上の容量絶縁膜2と、容量絶縁膜2上の上部電極3とを備えるキャパシタにおいて、容量絶縁膜2として、TiO2膜にZr又はAlが(Zr又はAl)/((Zr又はAl)+Ti)で表される原子数比で40%以下の濃度で均等に分布して添加された膜を使用する。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力を確保することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には素子分離領域と活性領域とが形成されており、ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31A、31Bと、ソース・ドレイン拡散層15、45とが備えられ、埋め込みゲート電極31A、31Bは、上部電極31aと下部電極31bとの積層構造とされ、且つ、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる。

(もっと読む)

キャパシタ素子とキャパシタ素子の製造方法および半導体装置

【課題】リーク電流の低減と静電容量の増加の両立を実現するキャパシタ素子とキャパシタ素子の製造方法および半導体装置を提供する。

【解決手段】本発明のキャパシタ素子は、少なくとも上面が第一の窒化金属からなる第一電極と、酸化ジルコニウム膜からなる容量絶縁膜と、ボロン、アルミニウム、ガリウムのいずれかが不純物としてドープされた酸化亜鉛膜からなる第一のバリア膜と、少なくとも下面が第二の窒化金属からなる第二電極と、がこの順で積層されてなることを特徴とする。

(もっと読む)

チャネルが埋込み誘電体層を通り抜けているメモリセル

【課題】浮動チャネルまたは浮動ゲートを持つFET(Field Effect Transistor(電界効果トランジスタ))により形成されたメモリセル、複数のメモリセルから成るメモリアレイの提供。

【解決手段】絶縁層BOXによってベース基板から隔てられた半導体材料の薄層を含むセミコンダクタ・オン・インシュレータ基板と、少なくとも基本的にセミコンダクタ・オン・インシュレータ基板の薄層中に配列されたソース領域S、ドレイン領域D、トレンチがその中に作られているチャネルC、トレンチ中のゲート領域Gを含むFETトランジスタを備え、トレンチが、絶縁層BOXを越えベース基板の深さの中に延びていること、チャネルが、絶縁層の下でソース領域とドレイン領域の間に延びていることを特徴とするメモリセル。複数のメモリセルを備えるメモリアレイ、およびメモリセルを製作するプロセス。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は補償容量部を設けたDRAMなどの半導体装置に関する。

【解決手段】本発明は、半導体基板の一面に形成された主トレンチ溝内に、ゲート絶縁膜を介しゲート電極が形成され、その両側にソース/ドレイン領域が形成されてなる主トランジスタ構造と、半導体基板の一面に形成された副トレンチ溝内に、ゲート絶縁膜を介しゲート電極が形成され、その両側にソース/ドレイン領域が形成されてなる補償容量用トランジスタ構造とが半導体基板に個々に形成され、主トランジスタ構造の主トレンチ溝の延在方向と補償容量用トランジスタ構造の副トレンチ溝の延在方向が平面視的に交差する方向に設定され、補償容量用トランジスタ構造のゲート絶縁膜周囲のチャネル領域に不純物拡散領域が形成されて補償容量トランジスタ構造の閾値電圧が主トランジスタ構造の閾値電圧より低くされてなることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】DRAM素子のような半導体装置において、半導体基板の溝部におけるゲート電極の埋設状態が良好となり、配線抵抗が低減され、素子特性に優れた半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の表面にゲート電極溝13を形成する工程と、ゲート電極溝13の内面に第1のバリア膜16aを形成する工程と、第1のバリア膜16aをエッチバックして、ゲート電極溝13の底面に第1のバリア膜16aの一部を残存させながら除去する工程と、ゲート電極溝13の内面と残存した第1のバリア膜16aの表面に第2のバリア膜16bを形成する工程と、第2のバリア膜16aの表面にタングステン膜を形成する工程と、このタングステン膜及び第2のバリア膜16bをエッチバックしてゲート電極溝13内にそれぞれ一部を残存させながら各膜を一括除去する工程と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造コストを増加させることなく、高アスペクト比のキャパシタ下部電極を保持するサポート膜構造を提供する。

【解決手段】サポート膜で保持された下部電極40を備えるキャパシタを複数含む半導体装置であって、前記サポート膜は、前記下部電極の高さ方向に複数層(例えば、16及び20の2層)形成され、各層のサポート膜は、前記下部電極間を接続するライン形状のパターンを有し、該パターンの延在方向が、隣接する二層間でそれぞれ異なることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離溝内に絶縁膜を埋め込んでなる素子分離膜に発生するボイドなどの埋め込み不良を防止する。

【解決手段】素子分離膜8によって区画された素子形成領域10aが、第1帯部141と第2帯部142と複数の素子形成部1aとを有し、複数の素子形成部1aは、第1帯部側の端部と第1帯部とが接続された複数の第1接続形成部10bと、第1帯部側の端部と第1帯部とが離間して配置された複数の第1離間形成部10dと、第2帯部側の端部と第2帯部とが接続された複数の第2接続形成部10cと、第2帯部側の端部と第2帯部とが離間して配置された複数の第2離間形成部10eとを含み、隣接する第1接続形成部10bの間に第1離間形成部10dが配置されているとともに、隣接する第2接続形成部10cの間に第2離間形成部10eが配置されている半導体装置とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】更なる微細化に対応可能な半導体装置の製造方法を提供する。

【解決手段】素子分離領域及び活性領域を形成する際は、素子分離用の溝部3が複数並んで形成されるセルアレイ領域SAよりも外側にある周辺領域CAに、当該セルアレイ領域SAに形成された溝部3よりも深い溝部3Aを形成する工程と、セルアレイ領域SAに形成された溝部3及び周辺領域CAに形成された溝部3Aにシリコン窒化膜28を埋め込んだ後、ウェットエッチングによりシリコン窒化膜28を選択的に除去しながら、少なくともセルアレイ領域SAに形成された溝部3の底部にシリコン窒化膜28が一定の厚みで残存した状態とする工程と、その後、セルアレイ領域SAに形成された溝部3及び周辺領域CAに形成された溝部3Aにシリコン酸化膜29を埋め込む工程とを含む。

(もっと読む)

キャパシタ、該キャパシタを備える半導体装置および半導体装置の製造方法

【課題】アスペクト比の高い電極を上下に接続して、静電容量の大きいキャパシタを形成する際、電極間の剥離を防止し、電極の倒壊を抑制する。

【解決手段】導電膜を外壁に有する下部電極30と、該下部電極の導電膜に対して、容量絶縁膜を介して形成された上部電極とを有するキャパシタにおいて、下部電極は少なくとも2層の積層構造であって、該積層構造は、下層側電極18に設けた掘り込み部に上層側電極22の底部が埋め込まれた構造であるキャパシタ。

(もっと読む)

81 - 100 / 266

[ Back to top ]